Fターム[4E351AA07]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | プリント基板の材料と性質 (2,230) | 無機材料を主体とするもの (650) | セラミックス (382)

Fターム[4E351AA07]の下位に属するFターム

高熱伝導率基板 (41)

ペロブスカイト型構造のもの (10)

Fターム[4E351AA07]に分類される特許

201 - 220 / 331

セラミックインターコネクト基板上の厚膜コンデンサ

【課題】高容量密度および他の望ましい電気的および物理的特性を有する厚膜コンデンサを、セラミックインターコネクト基板上に形成させる。

【解決手段】ガラスセラミックまたはセラミックのインターコネクト基板の上に第1の導電層を形成し、少なくとも約800℃の温度で焼成し、第1の導電層の上にコンデンサ誘電体を形成し、その誘電体の上に第2の導電層を形成し、コンデンサ誘電体と第2の導電層を共焼成する。

(もっと読む)

セラミックス回路基板及びその製造方法

【課題】半田層が介在することなく、放熱性、導電性、セラミックス基板と導体回路との接合信頼性、耐久性に優れるセラミックス回路基板及びその製造方法を提供する。

【解決手段】(A)セラミックス基板Bの表面に、第1のペーストを塗布して塗布層2を形成し、(B)この塗布層2を焼成して基板Bに対して密着性の高い第1のメタライズ層3を形成し、(C)このメタライズ層3に第2のペーストを塗布して、塗布層4を形成し、(D)この塗布層4を焼成して放熱性の高い第2のメタライズ層5を形成し、選択的に厚膜の放熱性導体回路1を有する回路基板を製造する。第1のペーストに比べて、銅粉などの金属粒子成分に対するガラス成分の割合が少ない第2のペーストを用いることにより、基板に対する密着性及び放熱性の高い放熱性導体回路1を形成できる。

(もっと読む)

配線基板内蔵用コンデンサ及び配線基板

【課題】樹脂材との密着性を向上させることが可能な配線基板内蔵用コンデンサ、及び信

頼性が充分に確保された配線基板を提供する。

【解決手段】配線基板内蔵用コンデンサ1は、積層された複数の誘電体層3と、互いに異

なる誘電体層3間に配置された内部電極層4,5とを有するコンデンサ本体2等から構成

されている。コンデンサ本体2の側面2c1〜2c3には、コンデンサ本体2の厚さ方向

に延びた凹部2dが形成されている。

(もっと読む)

モノリシックセラミック素子および作製方法

ここで提案されるのは、多層構造を有する改善形のモノリシックセラミック素子であり、この素子は、作製時に横方向に最小限にしか変形しない。これは、機能性セラミックからなる機能層(F1,F2)の他に、誘電再結晶材料を含む少なくとも1つのテンション層(S)を有する多層構造によって達成される。このテンション層の相転移温度は、焼成温度よりも低く、再結晶化される構造が得られる。この構造は、機能層の焼成温度の間、固体状態に止まり、上記の多層構造を横方向に力を加えるため、焼成による縮みは、層面に対して垂直なZ軸方向にしか発生しない。  (もっと読む)

(もっと読む)

高周波モジュール及びその製造方法

【課題】誘導性を有する回路部の一例としてのインダクタ部の厚さを厚くすることなく、インダクタ部を流れる電流の影響によるインダクタの特性劣化を防止し、薄型化することが可能な高周波モジュールを提供する。

【解決手段】本発明の高周波モジュール10は、基板11上に形成された、絶縁緩衝層12と、第2回路部としてのベタ電極13と、絶縁層14と、第1回路部としてのインダクタ電極15とから構成されており、ベタ電極13の電気抵抗率が、インダクタ電極15の電気抵抗率より高く形成されている。

(もっと読む)

インダクタ内蔵部品、及びこれを用いたDC−DCコンバータ

【課題】 漏れ磁束を低減し、インダクタを半導体集積回路(IC)と近接配置しても、優れた性能を発揮できるインダクタと、これを用いたDC−DCコンバータを提供する。

【解決手段】 相対向する上主面及び下主面と、上下主面間を連結する側面を備えた多層絶縁基板の、異なる磁性体層に配置したコイル導体を積層し、ビアホールを介して接続し上下方向に周回する積層コイルを備え、多層絶縁基板は、コイル形成磁性体層部と、その上下に位置する上磁性体層部と下磁性体層部を備え、積層コイルによって生じる磁束の方向に位置する磁性体層部の厚みを、他方の磁性体層部の厚みよりも厚くし、もって主面からの漏洩磁束を低減した。

(もっと読む)

配線基板およびその製造方法

【課題】実装パッドとフェライトとの界面の強度が高く、実装パッドに実装した半導体チップやチップ部品の実装信頼性が高い配線基板(例えばコイル内蔵基板)、およびその製造方法を提供する。

【解決手段】表層がフェライト層20とされた絶縁性基体と、フェライト層20に表面に形成された1以上の実装パッド5と、を備えた配線基板1であって、実装パッド5を、外周部に2価の金属酸化物を含むものとした。好ましくは、実装パッド5は、金属材料を主成分とする第1導体部51と、前記金属材料および前記2価の金属酸化物を含む第2導体部52と、を有するものとする。

(もっと読む)

導体層付セラミックス基板およびその製造方法

【課題】ハンダ付け性および接着強度に優れ、しかも比抵抗が小さい導体層が表面に形成されている導体層付セラミックス基板の提供。

【解決手段】焼成されてセラミックス積層体となるセラミックグリーンシート積層体の表面に、ガラス粉末および金属粉末を含有し焼成されて導体層となる導体ペーストが塗布されたものを焼成して得られたセラミックス基板であって、セラミックス積層体上の導体層がその表面側に存在する金属層とセラミックス積層体との界面側に存在するガラス層とに分離している導体層付セラミックス基板。

(もっと読む)

導電性ペースト

【課題】多層セラミック電子部品を製造する際に、有機ビヒクルの物理的特性変化による導電性材料の分散性低下を起こさず、かつセラミックグリーンシートへの浸食によるデラミネーションが生じない、すなわち、電気的特性の劣化の発生しないセラミック積層体を製造するための導電性ペースト用の溶剤を提供すること。

【解決手段】多層セラミック部品を製造する際に用いる導電性ペーストにおいて、溶剤成分として、芳香環含有エステル化合物および/または芳香環含有エーテル化合物を含有する導電性ペースト。

(もっと読む)

配線基板の製造方法

【課題】コイル内蔵基板の表層配線導体のメタライズ強度を高くすることで、基板の上面や下面に実装した半導体チップやチップ部品の実装強度の高いコイル内蔵基板を提供すること。

【解決手段】フェライトグリーンシート11を準備する工程と、フェライトグリーンシート11の表面に、2価の金属酸化物が添加された金属導体ペースト13を印刷する工程と、金属導体ペースト13が印刷された前記フェライトグリーンシートが表層に位置する積層体12を作製する工程と、積層体12を焼成する工程とを有する。

(もっと読む)

複合積層モジュール及びこれを用いた通信機

【課題】一つの積層体内に構成し小型軽量化を図ると共に回路間の相互干渉による特性劣化を抑制した複合積層モジュールを提供する。

【解決手段】分波回路と、スイッチ回路と、ローパスフィルタとを有し、これらの回路を構成するLC回路と伝送線路の一部は誘電体層に電極パターンにより構成し、ダイオードは積層体上に配置したアンテナスイッチ積層モジュールと、トランジスタと電源供給回路と整合回路とを有し、これらの回路を構成する伝送線路及びLC回路の一部は誘電体層に電極パターンにより構成し、トランジスタは積層体上に配置した高周波増幅器積層モジュールと、増幅器とアンテナスイッチモジュールを繋ぐ位相調整回路を伝送線路あるいはLC回路で構成し、一部を誘電体層に電極パターンにより構成し、両者を積層体の誘電体層に設けたシールド電極あるいは縦列したスルーホール電極により2つの領域に分けて形成した。

(もっと読む)

誘電体ペースト、ガラスセラミック多層配線基板、電子装置、およびガラスセラミック多層配線基板の製造方法。

【課題】高い誘電率を有し、加熱や電圧印加に対する誘電体層の絶縁性が高いコンデンサを、1000℃以下で焼成することができる誘電体ペーストを提供すること。

【解決手段】誘電体ペーストは、チタン酸バリウム粉末を70.0乃至99.6質量部と、マンガンおよび希土類元素を含む軟化点が1000℃以下のガラスからなるガラス粉末を0.4乃至30.0質量部と、を含む。

(もっと読む)

セラミック基板の製造方法

【課題】焼成時の収縮を抑制しながら突起電極を形成することができる、セラミック基板の製造方法を提供する。

【解決手段】(1)未焼成セラミック基板本体の少なくとも一方主面に、基板本体の焼成温度では実質的に焼結しない基材中に基板本体の焼成温度以下で焼結する主成分金属材料及び基板本体の焼成中に酸化・膨張する添加金属材料を含んだ未焼成突起電極用パターンを有する拘束層を密着してなる未焼成複合積層体を形成し、(2)拘束層の基材は実質的に焼結せず、基板本体及び主成分金属材料を焼結させ、添加金属材料を酸化・膨張させ得る温度・雰囲気のもとで、未焼成複合積層体を焼成し、(3)拘束層の基材を除去して、焼結済みセラミック基板本体16の一方主面に主成分金属材料の焼結体中に添加金属材料の酸化物18xを含有する突起電極18を有するセラミック基板15を取り出す。

(もっと読む)

導電性ペーストの製造方法および配線基板の製造方法

【課題】いわゆる収縮焼成抑制プロセスに好適で、グリーンシートの厚みに沿った収縮を抑制し、且つ焼成後のビア導体の突き上げが生じにくい導電性ペーストの製造方法、および当該導電性ペーストを用いる配線基板の製造方法を提供する。

【解決手段】導電性ペーストv1,v2をガラス−セラミックからなるグリーンシートs1〜s3の厚み方向に沿って貫通して充填する工程と、前記グリーンシートs1〜s3を積層してグリーンシート積層体GSを形成する工程と、かかるグリーンシート積層体GSの両面に、グリーンシートs1〜s3の焼成温度では焼成しない収縮抑制シートy1,y2を積層して複合積層体ZSを形成する工程と、かかる複合積層体ZSをグリーンシートs1〜s3の焼成温度で焼成する工程と、を含む、配線基板(1)の製造方法。

(もっと読む)

薄膜デバイスおよびその製造方法

【課題】キャパシタを備えた薄膜デバイスにおいて、キャパシタにおける一対の電極を構成する一対の導体層の相対的な位置関係の変化に起因するキャパシタの特性のばらつきを抑制する。

【解決手段】薄膜デバイス1は、基板2と、基板2の上に設けられたキャパシタ3を備えている。キャパシタ3は、下部導体層10と、一部が下部導体層10の上に配置された誘電体膜20と、誘電体膜20の上に配置された上部導体層30とを有している。下部導体層10は、上面と、側面と、これらによって形成される角部を有している。上部導体層30は、誘電体膜20を介して下部導体層10の上面に対向する下面を有する上部電極部分30aを有している。上部導体層30の上方から見たときに、上部電極部分30aの下面の外縁は、下部導体層10の上面の外縁に接することなく、その内側に配置されている。

(もっと読む)

基板の配線構造

【課題】多層構造を持たない基板において、高周波信号の伝送品質を確保することが可能な基板の配線構造を提供することを目的とする。

【解決手段】複数の集積回路を搭載可能な基板の配線構造100において、集積回路間を接続するための信号配線150と、対向配置される第1電源層130および第2電源層140と、信号配線150に略並行に配されたリターン・パス用配線130a、140aとを備え、リターン・パス用配線130aの両終端を第1電源層(Vcc層)130に接続し、リターン・パス用配線140aの両終端を第2電源層(Gnd層)140に接続する。

(もっと読む)

金属インク、並びにそれを用いた電極形成方法及び基板

本発明は、金属インク、並びにそれを用いた電極形成方法及び基板に関する。本発明は、金属酸化物ナノ微粒子及び金属部分縮重合酸化物から選ばれた少なくとも一つの100 nm以下の酸化物と、100 nm以下の金属ナノ微粒子とが溶媒内に超微粒子として孤立分散している金属インク、上記金属インクをインクジェットプリンタを用いてパターニングして導線を形成する電極形成方法、及びそれにより形成された基板を提供する。本発明によれば、インクジェットプリンタによるパターニングが可能であり、かつ基板に対する付着力が増大する。本発明の金属インクは、PDP等の各種パネルの電極を製造するのに有用である。  (もっと読む)

(もっと読む)

配線基板、及び電子装置

【課題】リフロー処理を行っても基材上の下地電極層がSnによって侵食されることもなく電極喰われを効果的に防止することのできるようにする。

【解決手段】配線基板1上の端子部3が、Cu等の下地電極層4と、該下地電極層の表面に形成されたNi層5と、該Ni層5の表面に形成されたCu層6と、該Cu層6の表面に形成されたSn層7とからなる4層構造とされている。そして、表面実装型電子部品を配線基板1上に搭載してリフロー処理を施すと、溶融したSnが、Cu層6、場合によってはNi層とも反応して金属間化合物を生成し、凝固後にはCu層6又はNi層5上にSn−Cu層又はSn−Cu−Ni層が形成される。

(もっと読む)

薄膜電子部品用基板及びそれを用いた薄膜電子部品並びにそれらの製造方法

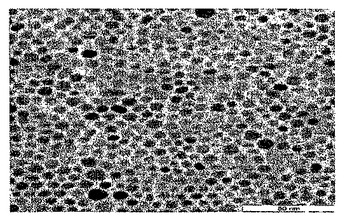

【課題】本発明の目的は、数nm〜数μmの膜厚の薄膜を成膜する高精度の薄膜デバイス製造技術を適用しうる、高精度の平滑性を有するセラミックス多結晶基板やガラスセラミックス基板及び該基板の上に受動素子を形成した薄膜電子部品並びにそれらの製造方法を提供することである。

【解決手段】本発明に係る薄膜電子部品用基板は、板状のセラミックス多結晶体若しくはガラスセラミックス体の少なくとも片面に、金属酸化物薄膜からなるコーティング層を設け、金属酸化物薄膜の膜厚を0.1μm以上20μm以下とし、且つ表面粗さRaを0.5nm以上20nm以下としたことを特徴とする。この高精度の平滑性を有する基板上に薄膜電子部品をPVD法等の薄膜デバイス製造技術を適用して形成する。

(もっと読む)

回路基板

【課題】 鉛フリー半田による導体の喰われを抑制し、鉛フリー半田による接合において接合信頼性の高い回路基板1を提供すること。

【解決手段】 配線5及びランド6を備えランド6に鉛フリー半田7で電子部品を接合する回路基板1であって、ランド6は配線5を形成する第一の導体からなる第一層61と第二の導体からなる第二層62とからなり、第二の導体で第一の導体を覆うように形成し、第二の導体の組成比を銀が65〜75重量%、パラジウムが20重量%以下、白金が10重量%以上で、かつ、白金/パラジウムの値が、1/2以上としたものである

(もっと読む)

201 - 220 / 331

[ Back to top ]