Fターム[4E351AA07]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | プリント基板の材料と性質 (2,230) | 無機材料を主体とするもの (650) | セラミックス (382)

Fターム[4E351AA07]の下位に属するFターム

高熱伝導率基板 (41)

ペロブスカイト型構造のもの (10)

Fターム[4E351AA07]に分類される特許

141 - 160 / 331

導体パターン形成用インク、導体パターンおよび配線基板

【課題】セラミックス成形体の熱膨張による導体パターンの断線を防止することができる導体パターン形成用インクを提供すること、信頼性の高い導体パターンを提供すること、および、このような導体パターンを備え、信頼性の高い配線基板を提供すること。

【解決手段】本発明の導体パターン形成用インクは、セラミックス粒子と、バインダーとを含む材料で構成されたシート状のセラミックス成形体上に付与され、導体パターンの形成に用いられる導体パターン形成用インクであって、水系分散媒と、水系分散媒中に分散した金属粒子と、セラミックス成形体に対して脱脂・焼結処理を施した際の、前記セラミックス成形体の熱膨張に追従しうる有機物で構成された断線防止剤とを含むことを特徴とする。前記有機物は、ポリグリセリン骨格を有するポリグリセリン化合物であるのが好ましい。

(もっと読む)

配線基板用導体ペーストおよびこれを用いた配線基板の製造方法、ならびに配線基板

【課題】線幅のバラツキやショート、断線の抑制された線幅30μm以下の微細な配線を形成するための配線基板用導体ペーストおよびこれを用いた配線基板の製造方法、ならびに配線基板を提供する。

【解決手段】金属粉末と有機バインダーと有機溶剤とを含み、前記有機バインダーのSP値と前記有機溶剤のSP値との差の絶対値が1.4〜3.9であることを特徴とする配線基板用導体ペーストである。また本発明は、複数の絶縁層と、該絶縁層の表面に形成された断面矩形状の配線とを含み、平面視による前記配線の直線部分の線幅が30μm以下であって最大線幅と最小線幅との差が8μm以下であることを特徴とする配線基板である。

(もっと読む)

導体パターン形成用インク、導体パターンおよび配線基板

【課題】液滴吐出ヘッドから安定して吐出可能な導体パターン形成用インクを提供すること、信頼性の高い導体パターンを提供すること、および、このような導体パターンを備え、信頼性の高い配線基板を提供すること。

【解決手段】本発明の導体パターン形成用インクは、液滴吐出法により、基材上に導体パターンを形成するための導体パターン形成用インクであって、金属粒子を水系分散媒に分散してなる分散液中に、導体パターン形成用インクの乾燥を抑制する乾燥抑制剤が含まれることを特徴とする。乾燥抑制剤の含有量は、3〜25wt%であるのが好ましい。乾燥抑制剤は、主として、多価アルコールで構成されているのが好ましい。多価アルコールは、糖アルコールを含むのが好ましい。多価アルコールは、少なくとも2種以上の糖アルコールを含むのが好ましい。

(もっと読む)

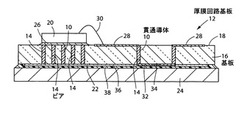

導体ペーストおよび厚膜回路用基板

【課題】 高い導電性を有して配線接続にも用い得る貫通導体を形成可能な導体ペーストおよびその貫通導体が形成された厚膜回路用基板を提供する。

【解決手段】 貫通導体10を形成するための導電ペーストは、焼成収縮率が35(%)以下と小さい銀粉末が用いられると共に、これに窒化珪素粉末が添加されていることから、高い導電性を確保しつつ焼成収縮が抑制される。そのため、酸化雰囲気中で焼成処理が施されることにより、サーマルビアとしても配線接続用としても用い得る貫通導体10が得られる。

(もっと読む)

高周波用電子部品

【課題】インダクタ用導体層とキャパシタ用導体層とを含む低温同時焼成セラミック多層基板を用いて構成された高周波用電子部品の特性および信頼性を向上させる。

【解決手段】電子部品1は、1以上のインダクタおよび1以上のキャパシタを含む低温同時焼成セラミック多層基板10を備えている。多層基板10は、積層された複数の誘電体層と、それぞれ積層方向に隣接する2つの誘電体層の間に配置された複数の導体層とを有している。複数の導体層は、1以上のインダクタを構成するための1以上のインダクタ用導体層と、1以上のキャパシタを構成するための2以上のキャパシタ用導体層とを含んでいる。インダクタ用導体層の厚みは、キャパシタ用導体層の厚みよりも大きい。また、インダクタ用導体層における金属材料に対するガラス成分の割合は、0であるか、キャパシタ用導体層における金属材料に対するガラス成分の割合よりも小さい。

(もっと読む)

電子部品およびその製造方法

【課題】

小型、かつ、湿度や温度の影響を受けにくく、長期的な信頼性の高い電子部品を提供する。

【解決手段】

受動素子を内蔵した低温同時焼成セラミックス(LTCC)基板10と;LTTC基板10の表面上に形成され、インダクタ固定に用いられる固定用樹脂絶縁層31と;固定用樹脂絶縁層31のLTTC基板10側と接触していない表面上に形成されたスパイラル状の金属銅製のインダクタ32と;を備える構成を採用する。

(もっと読む)

配線基板

【課題】 接続パッドが絶縁基体に強固に接合され、接続パッドを介して配線基板を外部電気回路基板に長期にわたって確実に電気的に接続させておくことが可能な、高い電気的な接続信頼性を有する配線基板を提供する。

【解決手段】 内部に配線導体2を有する板状の絶縁基体1の下面に複数の接続パッド3が縦横の並びに配列形成され、複数の接続パッド3の中央部分にそれぞれビア導体4の下端が接合されてなる配線基板9であって、接続パッド3のうち少なくとも縦横の並びの角部分に位置するものは、角部分の外側の外縁部分が、ビア導体4に隣接して形成された補助ビア導体5の下端と接合されている配線基板9である。接続パッド3の外縁部分が補助ビア導体5の下端と強固に接合されるため、接続パッド3の剥がれが抑制され、接続信頼性が向上する。

(もっと読む)

配線基板およびその製造方法

【課題】ビア導体におけるセパレーションの発生を低減させること。

【解決手段】基板11、活性金属の酸化物層15および導体層12を有している。基板11は、セラミックスからなり、スルーホールを有している。酸化物層15は、スルーホール11hの内側壁面に形成されている。導体層12は、活性金属からなり、酸化物層15の内側に形成されている。配線基板は、ビア導体13および導体パターン14を有している。ビア導体13は、11族の金属材料からなり、導体層12の内側に形成されている。導体パターン14は、スルーホール11h上に形成されている。

(もっと読む)

薄膜電子部品の製造方法

【課題】導体パターンの寸法精度を向上させることができる薄膜電子部品の製造方法を提供する。

【解決手段】セラミック基板1上に、第1樹脂からなる樹脂パターン3を形成する工程、樹脂パターン3及びセラミック基板1上にシード層15を形成する工程、シード層15上に、第2樹脂からなる樹脂層16を形成する工程、樹脂層16を、樹脂パターン3をトレースするように露光し、現像により樹脂層16の一部を除去してシード層15を露出させる工程、露出したシード層15上に導体パターン2を形成する工程、樹脂層16の残部を除去してシード層15を露出させる工程、露出したシード層15を除去する工程を含む薄膜電子部品の製造方法。

(もっと読む)

電子部品用セラミックス基板及びその製造方法

【課題】配線層として必要な伝熱性及び導電性を確保しつつ熱膨張率を低減し、配線層とセラミックス基板との界面における熱応力を低減せしめた電子部品用セラミックス部品、及びその製造方法を提供すること。

【解決手段】セラミックス基板10と、セラミックス基板10の表面に配設した配線層20を備えた電子部品用セラミックス基板1である。配線層20は、微細炭素繊維22と導電性母材21を含む複合材から成り、その厚さ方向において、連続した伝熱経路及び導電経路aが形成されている。微細炭素繊維22の軸方向が、配線層の面方向Fとはほぼ平行である。

(もっと読む)

配線及びその製造方法並びに配線を用いた電子部品及び電子機器

【課題】導電性微粒子本来の機能を損なうことなく保持しており、任意の基材表面に選択的に配列した単層の導電性微粒子層又は複数層の導電性微粒子層を有する配線及びその製造方法並びに配線を用いた電子部品及び電子機器を提供する。

【解決手段】基材11の表面のパターン部分22にのみ導電性微粒子31が配列した導電性微粒子層が1層結合固定されたパターン状の配線1、3であって、基材11の表面のパターン部分22には、分子の一端に第1の官能基を有する第1の膜化合物の被膜13が形成され、導電性微粒子31の表面には、分子の一端に第2の官能基を有する第2の膜化合物の被膜33が形成され、導電性微粒子31は、第1及び第2の官能基と第1のカップリング剤とのカップリング反応により形成された結合を介して基材11上に固定されている。

(もっと読む)

セラミック配線基板

【課題】一対の導体部の間を電気的に接続する厚膜抵抗体を有するセラミック配線基板において、厚膜抵抗体のトリミング部における抗折強度の低下を極力防止する。

【解決手段】セラミック層11の一面1a上に設けられた一対の導体部13と、一対の導体部13を電気的に接続する厚膜抵抗体14とを備え、厚膜抵抗体14のうち一対の導体部13の間に位置する部位が、トリミングされて切り欠かれたトリミング部20とされているセラミック配線基板S1において、厚膜抵抗体14におけるトリミング部20の直下では、当該トリミング部20とセラミック層11との間に、厚膜抵抗体14よりも電気絶縁性の大きな材料よりなる絶縁部17が設けられている。

(もっと読む)

セラミック配線基板及びセラミック配線基板の製造方法

【課題】抵抗が低い電気回路用配線及び十分な実装強度を有する実装用配線とを備えるセラミック配線基板、及びそのようなセラミック配線基板の製造方法を提供する。

【解決手段】本セラミック配線基板1は、セラミック絶縁体11(アルミナ絶縁体等)と、銅、タングステン粒子等、及び金属化合物粒子(アルミナ粒子等)とを含有し、且つ銅とタングステン粒子等との合計を100質量部とした場合に、銅は25〜65質量部、タングステン粒子等は35〜75質量部である電気回路用配線121(信号伝達用配線等)と、銅、タングステン粒子等、及びセラミック絶縁体を構成するセラミックと同種のセラミックの粒子(アルミナの粒子等)を含有する実装用配線122とを備え、セラミック粒子の平均粒径が、金属化合物粒子の平均粒径より大きいことを特徴とする。また、本セラミック配線基板の製造方法は、上記の配線基板の製造方法であり、特定の工程を備える。

(もっと読む)

パワーモジュール用基板及びその製造方法並びにパワーモジュール

【課題】回路層の各回路同士が良好に絶縁されるとともに、小型化・低価格化が可能なパワーモジュール用基板及びその製造方法並びにパワーモジュールを提供することにある。

【解決手段】セラミックス基板1の表面に、その上に接合したアルミニウム層2のエッチングにより回路層2aを形成してなるパワーモジュール用基板であって、前記回路層2aは、その前記セラミックス基板1との接合界面6から200μm以内のSiの含有量が0.7wt%以上1.2wt%以下とされていることを特徴とする。

(もっと読む)

導電性パターン用インク、導電性パターン形成方法及び導電性パターンを有する基板

【課題】低温での熱処理により抵抗値の低い導電性パターンを形成することが可能であり、また200℃程度の熱処理によって、ガラス系基板、セラミック基板又は金属基板との優れた密着性を有する導電性パターンを形成することが可能な導電性パターン用インクを提供する。

【解決手段】銀及びビスマスからなる合金ナノ粒子を含有することを特徴とする導電性パターン用インク。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

セラミック基板の製造方法、セラミック基板、および電子装置

【課題】抵抗を覆うオーバーコートガラスのめっき耐性の高いセラミック基板を確実に製造することが可能なセラミック基板の製造方法、および信頼性の高いセラミック基板、および該セラミック基板を用いた電子装置を提供する。

【解決手段】一方主面1aに抵抗15となる抵抗膜115が形成され、抵抗膜を覆うように、収縮開始温度が、抵抗膜のそれより高い第1のガラス膜111を形成し、形成された第1のガラス膜111を覆うように、第1のガラス膜を構成するガラス材料よりめっき耐性が大きいガラス材料を含む第2のガラス膜112を形成し、かつ、少なくとも一方主面1aに、焼成工程で焼結しないセラミック材料からなる収縮抑制用グリーンシート102が配置された積層体を形成し、この積層体を、セラミックグリーンシートが焼結し、収縮抑制用グリーンシートが実質的に焼結しない温度で焼成する。

(もっと読む)

配線基板およびプラズマ発生体

【課題】表面に形成された電極表面の酸化を抑制し、酸化雰囲気下においても電気的接続性に優れた配線基板を提供する。

【解決手段】酸化雰囲気下で用いられる配線基板1であって、絶縁基板2と、少なくとも一部が絶縁基板2の表面に設けられた電極3と、表面に設けられた電極3aを覆う耐酸化性の被覆層4とを備える。また、好ましくは、絶縁基板2は、熱膨張率が4ppm以下の絶縁体から成り、電極3は、熱膨張率が4ppm以下の導電性材料から成る。

(もっと読む)

セラミック配線基板およびその製造方法

【課題】 絶縁層の比誘電率を増加せることなく、マイクロ波加熱による焼成が可能なセラミック配線基板およびその製造方法を提供する。

【解決手段】 内部配線導体2、ビアホール導体3および表面配線導体4,5は、Ag系、Cu系、Pd系、Ptなどの金属導体に加えて、絶縁層よりも比誘電率の高い材料から成る添加剤を含むように構成されている。添加剤の比誘電率は7以上が好ましく、具体的には、比誘電率が高いSiC、TiO2、ZrO2、MgO、AlN、Cr2O3、ZnOおよびSi3N4から選ばれる1種または2種以上を用いることができる。これらの中でもSiC、TiO2、ZrO2、MgO、Cr2O3、ZnOは、少ない添加量で比誘電率を高くすることができるので好ましい。

(もっと読む)

ビアホール充填用導電性ペースト組成物とそれを用いた多層配線基板

【課題】通常の印刷手法によってビアホールに充填でき、非鉛なので環境負荷低減の点から好ましく、また、多層配線基板に積層後におけるビアホールに欠陥がなく、接続信頼性が高く、抵抗値を非常に小さくできる、ビアホール充填用導電性ペースト組成物及び該ペースト組成物を用いた多層配線基板を提供する。

【解決手段】多層配線基板(200)におけるビアホール(30)に充填する導電性ペースト組成物(40)における、導電粉末およびバインダー成分の質量比を90/10以上98/2未満とし、導電粉末を、180℃以上260℃未満の融点を有する非鉛半田粒子である第1の合金粒子、Au,Ag,Cuからなる群から選ばれる少なくとも一種以上である第2の金属粒子とし、第1の合金粒子と第2の金属粒子との質量比を76/24以上90/10未満とし、バインダー成分をビスアリルナジイミド化合物とする。

(もっと読む)

141 - 160 / 331

[ Back to top ]