Fターム[4E351BB22]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | 印刷電気部品の種類と構造 (5,073) | 構造一般 (3,045) | 同一基板内の複数印刷部品(裏面を含む) (110)

Fターム[4E351BB22]の下位に属するFターム

材料の異なる同種印刷部品 (71)

Fターム[4E351BB22]に分類される特許

21 - 39 / 39

多層プリント配線板

【課題】高誘電率の部材で絶縁層を形成する必要のある素子と、インダクタとを近接して配置しても、インダクタの共振周波数を高く保つことが可能な多層プリント配線板を提供する。

【解決手段】多層プリント配線板10は少なくとも第一の絶縁層11、第二の絶縁層12、および第三の絶縁層13が順に重ねて配されてなる。また、第二の絶縁層12と第三の絶縁層13との間には、インダクタ15が形成されている。そして、第一の絶縁層11、第二の絶縁層12、および第三の絶縁層13のうち、少なくとも1つの絶縁層は、他の絶縁層に対して誘電率の異なる部材で形成されている。

(もっと読む)

非接触電力伝送用フィルム

【課題】非接触方式で電力を効率的に伝送することが可能であるとともに、製造時の環境負荷が小さく、コンパクトな非接触電力伝送装置の設計に寄与することが可能で実用的な非接触電力伝送用フィルムを提供する。

【解決手段】非接触電力伝送用フィルム1は、ナノ銀ペーストを含有した導電性インクをスクリーン印刷することによって、フィルム(基材)2の表面および裏面に、アンテナパターン層3a,3bが積層されている。そして、表面側のアンテナパターン層3aの上には、絶縁パターン層4a、配線パターン層5が積層されており、裏面側のアンテナパターン層3bの上には、絶縁パターン層4bが積層されている。また、アンテナパターン層3aとアンテナパターン層3bとは、フィルム2に設けられたスルーホール6,6・・によって接続されている。

(もっと読む)

高周波用電子部品

【課題】インダクタ用導体層とキャパシタ用導体層とを含む低温同時焼成セラミック多層基板を用いて構成された高周波用電子部品の特性および信頼性を向上させる。

【解決手段】電子部品1は、1以上のインダクタおよび1以上のキャパシタを含む低温同時焼成セラミック多層基板10を備えている。多層基板10は、積層された複数の誘電体層と、それぞれ積層方向に隣接する2つの誘電体層の間に配置された複数の導体層とを有している。複数の導体層は、1以上のインダクタを構成するための1以上のインダクタ用導体層と、1以上のキャパシタを構成するための2以上のキャパシタ用導体層とを含んでいる。インダクタ用導体層の厚みは、キャパシタ用導体層の厚みよりも大きい。また、インダクタ用導体層における金属材料に対するガラス成分の割合は、0であるか、キャパシタ用導体層における金属材料に対するガラス成分の割合よりも小さい。

(もっと読む)

多数個取りセラミック基板

【課題】縦横に複数の基板部分を表面および裏面に沿って形成されたブレーク溝により分割してなる多数個取りセラミック基板において、表面および裏面に形成した導体層同士を確実に導通できる各基板部分を得る。

【解決手段】単層のセラミック層Sからなり、ほぼ矩形を呈する複数の基板部分10を縦横に隣接して有する基板本体2と、隣接する基板部分間における基板本体2の表面3および裏面の平面視で同じ位置に形成されたブレーク溝vと、該ブレーク溝vが直角に交差する位置ごとに形成され、基板本体を貫通する複数の貫通孔hと、該貫通孔hごとの内壁面に形成された筒形導体層16と、基板本体2の表面3における基板部分10ごとの四辺に沿って形成され、各コーナ付近で筒形導体層16と接続する表面導体層12とを含み、隣接する基板部分10ごとの表面導体層12は、筒形導体層16のみを介して互いに導通している多数個取りセラミック基板1。

(もっと読む)

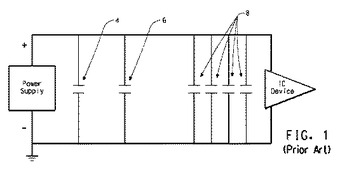

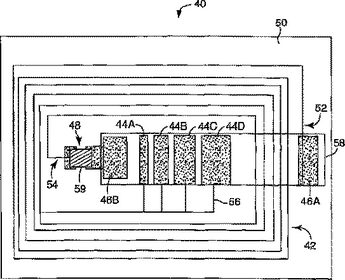

プリント配線板のビルドアップ層への薄膜キャパシタの統合方法

ここで提供されるのは、ノーングッド薄膜箔上焼成キャパシタから作製された単一化キャパシタを含むプリント配線板を含むデバイスである。提供されるのは、プリント配線板のビルドアップ層に単一化キャパシタを組み込んでインピーダンスを最小限にする方法である。単一化キャパシタは、ICの各電力およびグランド端子を、それ自体の単一化キャパシタの電力およびグランド電極にそれぞれ直接接続できるようにするピッチを有する。ノーングッド箔上焼成キャパシタの供給材料を用いることにより、PWB歩留まりが改善される。  (もっと読む)

(もっと読む)

キャパシタを含むチップ・キャリア基板およびその製造方法

【課題】基板内にそれぞれ設置された、キャパシタ・アパーチャおよび側方に離間されたバイア・アパーチャを含むチップ・キャリア基板を提供すること。

【解決手段】キャパシタ・アパーチャは、基板内でキャパシタ・アパーチャおよびバイア・アパーチャを同時にエッチングするために用いられるプラズマ・エッチ法におけるマイクロローディング効果に伴なってバイア・アパーチャよりも狭い線幅およびより浅い深さで形成される。その後、キャパシタ・アパーチャ内でキャパシタが形成および設置され、バイア・アパーチャ内でバイアが形成および設置される。第1のキャパシタ・プレート層、キャパシタ誘電体層および第2のキャパシタ・プレート層の様々な組み合わせは、キャパシタ・アパーチャおよびバイア・アパーチャに関しては連続し得る。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の各層と電子部品との位置精度を向上させることにより、小型化を可能とし、さらに、一括で半導体素子、キャパシタ、抵抗体、及びインダクタ等の電子部品を配線基板内に内蔵させることより、製造時間及びコストを低減させる。

【解決手段】半導体素子、キャパシタ、抵抗、及びインダクタ等の電子部品が内蔵される配線基板において、各層の積層の際に、電子部品が実装されているフィルムキャリアのスプロケットホール等により位置合せを行うことで、配線基板の各層と電子部品との位置精度を向上させることにより、また、技術的に確立されたILB接続技術を用いることにより、半導体素子の狭ピッチ化への対応、接続の信頼性確保、さらには、上層に最短距離で配線を引き出しが可能となり、小型化を実現する。

(もっと読む)

放熱基板とその製造方法及び電源ユニット及びプラズマ表示装置

【課題】従来の、PDP(プラズマディスプレイパネル)等の電源ユニットに使われるコイルは、そのインダクタンス値(L成分)が最大±20%ばらついてしまい、更にプラズマパネルの容量負荷(C成分)もばらついてしまうため、プラズマテレビの電力損の最小化に影響を与えるという課題を有していた。

【解決手段】一つ以上の孔16を有する金属板11の上に、一部がコイル15であるリードフレーム12を埋め込んだシート状の伝熱樹脂部10を固定し、前記コイル15の略中央部に形成した孔16にフェライトコア17を挿入し、インダクタンス値(L成分)を調整することで、プラズマテレビの電力損を抑える。

(もっと読む)

固体電解コンデンサ内蔵基板の製造方法

【課題】本発明は、固体電解コンデンサを高精度に容易に製造できる電解コンデンサ内蔵基板の製造方法を提供することを目的とする。

【解決手段】弁作用を有する金属箔上に形成された固体電解質層、集電体層からなる小型大容量の固体電解コンデンサを電気絶縁性基板内に内蔵し、インナービアとスルーホール電極で接続したので、短配線で実装面積の小型化が図れ、低インピーダンス特性を有する電解コンデンサ内蔵基板の製造方法を実現できる。

(もっと読む)

固体電解コンデンサ内蔵基板およびその製造方法

【課題】高速ICの電化供給、ノイズ低減を容易にする固体電解コンデンサ内蔵基板を提供する。

【解決手段】表面に誘電体被膜が形成された多孔質部を有する弁金属箔の一部において、絶縁材料からなる陽陰極分離部を有し、陽陰極分離部によって陽極と陰極が電気的に絶縁され、陰極は多孔質部上に形成された固体電解質層を有し、陽極は弁金属シート体の金属部分と電気的に接続され、かつ固体電解コンデンサを内部に複数個有し、それぞれの固体電解コンデンサ同士が電気的接続を有しない構成であり、個々の固体電解コンデンサは陽極の一部から電流が流入するとともに、他の陽極から電流が流出する電極構成を有する固体電解コンデンサ内蔵基板である。

(もっと読む)

セラミックインターコネクト基板上の厚膜コンデンサ

【課題】高容量密度および他の望ましい電気的および物理的特性を有する厚膜コンデンサを、セラミックインターコネクト基板上に形成させる。

【解決手段】ガラスセラミックまたはセラミックのインターコネクト基板の上に第1の導電層を形成し、少なくとも約800℃の温度で焼成し、第1の導電層の上にコンデンサ誘電体を形成し、その誘電体の上に第2の導電層を形成し、コンデンサ誘電体と第2の導電層を共焼成する。

(もっと読む)

フレキシブル回路基板およびその製造方法

【課題】複数の可撓性を有するシート状回路デバイスを埋設して、可撓性の極めて大きく、信頼性に優れたフレキシブル回路基板およびその製造方法を提供することを目的とする。

【解決手段】少なくとも一方の面に配線パターン11が設けられた可撓性を有する第1の基板12と、配線パターン11と接続された複数の可撓性を有するシート状回路デバイス15と、シート状回路デバイス15を埋設する可撓性を有する第2の基板13と、を備え、第1の基板12と第2の基板13とを一体化した基板14に配線パターン11およびシート状回路デバイス15を埋設して構成する。

(もっと読む)

複合積層モジュール及びこれを用いた通信機

【課題】一つの積層体内に構成し小型軽量化を図ると共に回路間の相互干渉による特性劣化を抑制した複合積層モジュールを提供する。

【解決手段】分波回路と、スイッチ回路と、ローパスフィルタとを有し、これらの回路を構成するLC回路と伝送線路の一部は誘電体層に電極パターンにより構成し、ダイオードは積層体上に配置したアンテナスイッチ積層モジュールと、トランジスタと電源供給回路と整合回路とを有し、これらの回路を構成する伝送線路及びLC回路の一部は誘電体層に電極パターンにより構成し、トランジスタは積層体上に配置した高周波増幅器積層モジュールと、増幅器とアンテナスイッチモジュールを繋ぐ位相調整回路を伝送線路あるいはLC回路で構成し、一部を誘電体層に電極パターンにより構成し、両者を積層体の誘電体層に設けたシールド電極あるいは縦列したスルーホール電極により2つの領域に分けて形成した。

(もっと読む)

コイル内蔵基板

【課題】コイル内蔵基板の内蔵コイルの重畳特性を向上させると共に、上面や下面に搭載された半導体チップやチップ部品に対するコイル用導体から発生する磁力線の影響を大幅に抑制することができるコイル内蔵セラミック基板を提供すること。

【解決手段】本発明のコイル内蔵基板は、間に平面スパイラルコイル4が埋設されている、第1のフェライト層2および第2のフェライト層3を、一対の絶縁層1で挟持してなるコイル内蔵基板において、平面スパイラルコイル4のコイル導体間に第1のフェライト層2および第2のフェライト層3より透磁率の小さい第3のフェライト層を形成することで成る。

(もっと読む)

高密度化金属粉末を使用する電磁通信回路構成要素の形成

電気構成要素を形成するための製造技術が記載される。たとえば、金属粉末組成物の層を基材の少なくとも一部の上に堆積させる。1つ以上の突起を有する液圧プレスによって圧力を金属粉末組成物に加え、パターンを基材上に捕捉する。液圧プレスの突起によって圧縮された金属粉末組成物は、基材に接着して、捕捉されたパターンを形成する。液圧プレスの突起によって圧縮されない領域の金属粉末組成物は、基材に接着せず、除去することができる。これらの金属粉末組成物を圧縮して、電子監視システム(EAS)、無線周波数識別(RFID)システムなどに使用するための、アンテナ、キャパシタプレート、導電パッドなどの電気構成要素を形成することができる。  (もっと読む)

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】アンテナとして十分に機能する導電膜を有する半導体装置および当該半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上にトランジスタを含む素子形成層と、素子形成層上に設けられた絶縁膜と、絶縁膜上に設けられたアンテナとして機能する導電膜とを有し、トランジスタと導電膜は電気的に接続され、絶縁膜は溝を有し、絶縁膜の表面および溝に沿って導電膜を設ける。なお、絶縁膜が有する溝は、絶縁膜を貫通させて設けてもよいし、絶縁膜を貫通させずに絶縁膜に凹部を形成して設けてもよい。溝の構造はどのように設けてもよく、例えばテーパー状等に設けることができる。

(もっと読む)

導電体充填ビアを用いた内蔵キャパシタ

内蔵キャパシタ及びその製造方法が提供される。内蔵キャパシタの製造方法は、誘電体基板(100)に少なくとも1つの孔部(115)を形成する工程を含む。孔部を形成するため、誘電体基板は機械的に打ち抜かれ、或いはレーザ切断され得る。第1電極(470)を形成するために孔部は導電体(250)で充填される。第1電極と電気的に接触しないように誘電体基板に導体(360)が形成される。孔部の深さ及び/又は断面積は、電極と導体との間に所望量の容量結合が設けられるように選定される。さらに、第2導体が、第1電極と電気的に接触するように誘電体基板に堆積される。少なくとも第2の孔部が誘電体基板に形成され、第2電極を形成するために導電体で充填される。第2電極は第1電極に電気的に接続される。  (もっと読む)

(もっと読む)

境界を有する1若しくはそれ以上の層を備える層状のバリア構造及び該バリア構造の製造方法

システムは、環境的バリアを備える。環境的バリアは、回路を提供するのに好適に使用可能である。例えば、装置が薄いフィルム状のバッテリ(例えば、リチウムやリチウム化合物を備えるバッテリ)を備え、このバッテリが電気回路に接続する形態を挙げることができる。環境的バリアは、交代層として積層される。交代層を構成する層のうち少なくとも1つは、平滑化、平坦化及び/又は水平化を、物理的構造機能をもたらす層に与える。交代層を構成する層のうち少なくとも他の1つの層を構成し、この層は拡散バリア機能を発揮する。物理的構造機能を与える層は、フォトレジスト、光学的に境界を定めることが可能な層、エネルギ的に境界を定めることが可能な層及び/又はマスク可能な層を備える。物理的構造層は誘電体からなるものであってもよい。層状の構造は、複数の層の対を備え、各層の対は物理的構造層及びバリア層を備える。バリア層は低い気体透過速度性能を備える。このことにより、現状において検知可能な水準以下にまでガスの透過速度を低減可能となる。 (もっと読む)

プリント基板

【課題】 基板上に取り付けられたシールドケースの内部と外部の信号線を接続するのに、作業量及び部品コストを低減する構造のプリント基板を提供する。

【解決手段】 プリント基板16を多層構造にし、シールドケース1が取り付けられると共に当該シールドケース1の内部及び外部に信号パターン17、23が形成された最上層(1/4層)に、シールドケースの内部及び外部に形成された信号パターンにそれぞれ接続されるコンデンサ18,19を設けると共に、下層に、スルーホール24,25を介して最上層に設けられたコンデンサと接続されてフィルタ回路を構成するプリントコイル20,21を形成し、フィルタ回路を介してシールドケースの内部及び外部に形成された信号パターン17,23を接続する。

(もっと読む)

21 - 39 / 39

[ Back to top ]