Fターム[4K029HA01]の内容

Fターム[4K029HA01]の下位に属するFターム

Fターム[4K029HA01]に分類される特許

481 - 487 / 487

マスクアライメント法を用いたディスプレイの製造方法

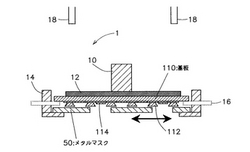

【課題】ディスプレイ基板とマスクのアライメントプロセスを迅速/正確に行い、表示品位の高い大画面ディスプレイを提供する。

【解決手段】複数の画素パターンを有する基板110と、画素パターンに対応する穴部を有するマスク50を準備する第1工程と、マスクと基板とを位置合わせし、両者を固定する前の状態における穴部と画素パターンとの位置関係を測定する第2工程と、マスクと基板との位置関係を固定し、この状態における穴部と画素パターンとの位置関係を測定し、この位置関係と第2工程において測定した位置関係との間の位置ずれ量を算出する第3工程と、同一のマスクを他の基板に対して位置合わせを行う際に、前記位置ずれ量をフィードバックし、マスクと該他の基板との位置関係を補正する第4工程と、蒸着源より蒸着物をマスクの穴部を介して画素パターン上に被着させることにより、画素パターン上に蒸着物層114を形成する第5の工程とを備える。

(もっと読む)

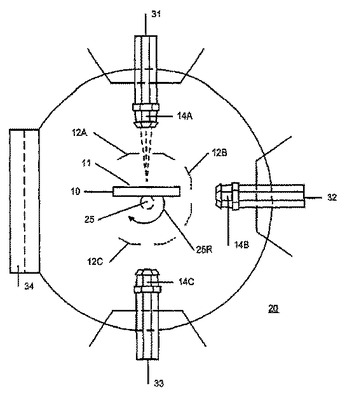

蒸着装置

【課題】 本発明は、極力材料の無駄が発生しない蒸着装置を提供することを目的とする。

【解決手段】 蒸着装置10aは、各基板14間を移動し、材料を加熱蒸発させ、各基板14に対して蒸発物を堆積させるための蒸発源12を備える。基板14を真空チャンバーA,Cに出入したりアライメントしたりする間に他の基板14を蒸着する。材料の無駄が非常に少なく、製造されるOLEDの製造コストを下げることができる。

(もっと読む)

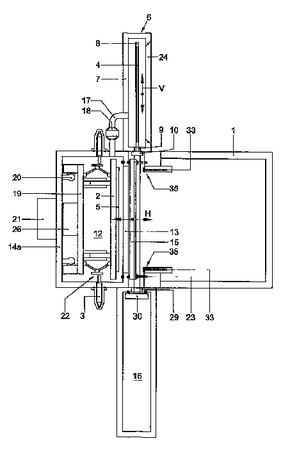

成膜源、成膜方法、および加熱板、ならびに有機EL素子の製造方法

【課題】成膜材料の有効利用が可能であり、かつ、良好な膜質の膜を成膜することが可能な成膜源を提供する。

【解決手段】成膜源102は、成膜材料121が内部に充填される成膜材料収容部である坩堝122と、充填された成膜材料121の表面に載置される加熱体である加熱板123とを備える。加熱板123には複数の貫通孔125が所定のパターンで形成されている。また、加熱板123の貫通孔125が形成されていない領域には、ヒータ126が配設されている。成膜時には、ヒータ126によって加熱された加熱板123により、坩堝122内の成膜材料121の表面が加熱され、該表面の成膜材料121が蒸発して蒸着成膜が実施される。

(もっと読む)

材料組み合わせ研究のための高スループット物理気相成長システム

無限に変更可能な物理気相成長マトリックスシステムは、多数の材料を同時堆積することによって、又は多数の触媒成分を次々に層状に堆積することによって、或いはその両方によって、多数の組み合わせの触媒サンプルを概ね同時に合成できるようにし、それによって、所定の応用形態のために最適な材料混合物を後の試験において実験的に決定することができるようにする。指定された反応及び装置において利用するための最適な触媒の組み合わせの発見が容易になる。高スループットシステムによって、組み合わせの触媒材料を配合し、試験するために通常必要とされる処理時間が短縮され、その方法が簡単になる。

(もっと読む)

(もっと読む)

蒸着法

材料の混合物を基板(1)上で量を徐々に変化させて蒸着させるのに使用可能で、様々な目的に使用可能であるが、コンビナトリアルケミストリーにおいて特別な価値を有する蒸着法において、ソース(3)から基板(1)までの蒸発材料の経路は、マスク(5)によって部分的に妨げられ、基板(1)により規定される平面と平行な平面におけるマスクの配置は、基板(1)に沿う方向に実質的に連続して増加する厚みで材料を基板(1)上に蒸着させるようになされる。 (もっと読む)

基板を処理するためのシステムおよび方法

少なくとも1つの基板(5)を真空プロセスにて処理するための少なくとも1つの処理チャンバ(1)を備えた、基板を処理するためのシステムであって、前記処理チャンバ(1)は、閉鎖ボディ(15)にて閉鎖することができる基板アクセス(13)を備え、このシステムは、少なくとも前記閉鎖ボディ(15)を移動させるように構成された運搬デバイス(8)を備え、この運搬デバイス(8)は、前記基板(5)を前記真空プロセスの際に少なくとも部分的にカバーするためのマスク(4)を、少なくとも前記処理チャンバ(1)の外側のある位置と前記処理チャンバ(1)の内側のある位置との間で運搬するように構成される。少なくとも前記基板ホルダ(2)に、基板ホルダ(2)とマスク(4)とを互いに位置決めするための手段が提供された場合は、有利である。本発明は、更に、このようなシステムの使用に係る。  (もっと読む)

(もっと読む)

薄膜トランジスタの封止方法

ゲート電極と、ゲート誘電体と、ソースおよびドレイン電極と、半導体層とを含む薄膜トランジスタを提供する工程と、封止材料をアパーチャマスクのパターンを通して前記半導体層の少なくとも一部の上に蒸着する工程とを含む、薄膜トランジスタの封止方法。  (もっと読む)

(もっと読む)

481 - 487 / 487

[ Back to top ]