Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

201 - 220 / 2,965

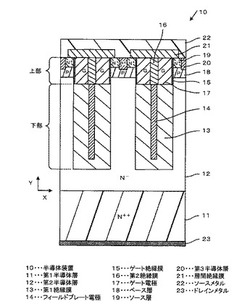

半導体装置およびその製造方法

【課題】ゲート電極とフィールドプレート電極間の容量を低減させた半導体装置およびその製造方法を提供する。

【解決手段】一実施形態によれば、半導体装置10は、N++型の第1半導体層10上にN−型の第1導電型の第2半導体層12が形成されている。フィールドプレート電極14が第2半導体層12に形成されたトレンチの底面側であって、第1絶縁膜13を介してトレンチの下部を埋め込むように形成されている。第2絶縁膜16がトレンチの上部において、フィールドプレート電極14の上面に接するように形成されている。ゲート電極17がトレンチの開口側であって、ゲート絶縁膜15を介するとともに第2絶縁膜16を挟んでトレンチの上部を埋め込むように形成されている。P型のベース層18が第2半導体層12の上部に形成されている。N+型のソース層19がベース層18の上部に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】安定したリカバリ耐量が得られる半導体装置を提供する。

【解決手段】表面電極21のうち抜き取り部2bに形成されたコンタクトホール20bから露出するコンタクト領域23と対向する部分をそれぞれコンタクト部21dとし、コンタクト部21dと表面パッド5とを結ぶ最短距離の線分L1上にそれぞれ切り込み部21cを形成する。これによれば、コンタクト部21dから表面パッド5までのホールが流れる経路が長くなって抵抗が高くなるので、コンタクト領域23にホールが集中することを抑制することができ、安定したリカバリ耐量を得ることができる。

(もっと読む)

半導体装置

【課題】信頼性を犠牲にすることなく、オン抵抗を低減することができるトレンチゲート型の半導体装置を提供する。

【解決手段】半導体装置1は、ドレイン領域21と、ドレイン領域21に積層されたチャネル領域20と、チャネル領域20に積層されたソース領域16とを有するシリコン半導体層からなる活性領域30を含む。半導体装置1は、さらに、ソース領域16からチャネル領域20を貫通してドレイン領域21に至るトレンチ15内に埋め込まれたゲート導体(ポリシリコンゲート)26と、ソース領域16に電気的に接続されたソース電極4とを含む。ソース電極4は、ソース領域16に接するように形成され、ソース領域16との界面がシリサイド化された密着層41を有する。密着層41は、膜厚が150Å以下の金属層からなる。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

電力用半導体装置

【課題】高温動作において配線の金属材料と半導体領域に接続する電極との反応が生じにくく、かつ、高温動作において歪みが生じにくい電力用半導体装置を実現する。

【解決手段】第1金属層14は、ゲート電極9とソース電極11との上に形成され、かつ、Pt,Ti,Mo,W,Taのうち少なくとも1種を含んでいる。第2金属層15は、第1金属層14上に形成され、かつ、Mo,W,Cuのうち少なくとも1種を含んでいる。層間絶縁膜10は、p型SiC領域13およびゲート絶縁膜8またはゲート電極9の表面上であってソース電極11が形成された領域以外の領域において形成されている。第1金属層14および第2金属層15は、層間絶縁膜10上に延在している。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、アミノシラン系ガスのアミノシランは熱分解させないで、下地上に吸着させる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】Al原子を有するコンタクト電極が用いられる場合に、絶縁膜の絶縁信頼性を向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板面12Bを有する炭化珪素基板10が準備される。基板面12Bの一部を覆うように絶縁膜15が形成される。絶縁膜15に接触するように基板面上にコンタクト電極16が形成される。コンタクト電極16はAl、TiおよびSi原子を含有する。コンタクト電極16は、Si原子およびTi原子の少なくともいずれかと、Al原子とを含有する合金から作られた合金膜50を含む。炭化珪素基板10とコンタクト電極16とがオーミックに接続されるようにコンタクト電極16がアニールされる。

(もっと読む)

半導体装置

【課題】十分なチャネル移動度と製造コストの低減とを両立することが可能な半導体装置を提供する。

【解決手段】MOSFET100は、{0001}面に対するオフ角が50°以上65°以下である主面1Aを有する炭化珪素基板1と、主面1A上に形成された活性層7と、活性層7上に接触して形成されたゲート酸化膜91と、活性層7においてゲート酸化膜91と接触する領域を含むように形成され、導電型がp型であるp型ボディ領域4と、p型ボディ領域4内において活性層7の炭化珪素基板1とは反対側の主面を含むように形成され、導電型がn型であるn+領域5と、活性層7上にn+領域5と接触するように形成されたソースコンタクト電極92とを備え、p型ボディ領域4におけるp型不純物密度は5×1017cm−3以上であり、ソースコンタクト電極92とp型ボディ領域4とは直接接触している。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理に使用するガスを供給する処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、処理室101に、被処理体1を複数収容するとともに、コントローラ150が、下地を加熱し、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、下地を加熱し、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御する。

(もっと読む)

半導体装置

【課題】 縦型MOSFETのオン抵抗及びスイッチング損失の低減。

【解決手段】 封止体と、前記封止体内に位置する半導体チップと、前記封止体の内外に亘って延在する複数のリードと、前記半導体チップの電極と前記封止体内に位置するリードの内端を電気的に接続する導電性のワイヤとを有し、前記半導体チップには縦型電界効果トランジスタセルが並列接続状態で複数組み込まれ、半導体チップの表面にはゲート電極とソース電極が交互に並んでそれぞれ複数配置されるとともに、前記各電極に対応してリードが並び、前記各電極と前記対応した各リードは前記ワイヤによって接続されていることを特徴とする半導体装置。

(もっと読む)

半導体装置および電力変換装置

【課題】低損失と高耐圧を保持しながら、ターンオンスイッチング期間中におけるdv/dtのゲート駆動回路による制御性を向上できる半導体装置を提供する。

【解決手段】第1導電型の第1半導体層4と、その表面付近に形成された第2導電型の第2半導体層2と、これに電気的に接続する第1主電極11と、第1半導体層4に隣接し第2半導体層2とは逆側の表面付近に形成された第2導電型の第3半導体層6と、この上部に選択的に設けられた第1導電型の第4半導体層7と、第3半導体層6及び第4半導体層7に電気的に接続する第2主電極14と、側面が第4半導体層7と第3半導体層6に接し第1半導体層4に達するトレンチ17と、この側面に沿ってポリシリコンのサイドウオールにより形成されたゲート電極9と、トレンチ17内でゲート電極9から離れて設けられ第2主電極14と電気的に接続するポリシリコン電極18が設けられている。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

201 - 220 / 2,965

[ Back to top ]