Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

161 - 180 / 2,965

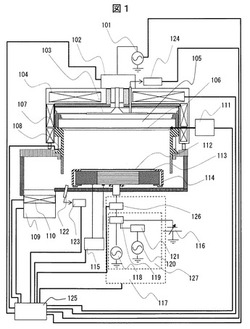

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

半導体装置

【課題】リーク電流を抑制した半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、第1導電型の半導体層、複数のトレンチ、絶縁層、導電層、第1半導体拡散層、及びアノード電極を有する。半導体層は、半導体基板上に形成され第1の不純物濃度よりも小さい第2の不純物濃度を有する。複数のトレンチは、半導体層の上面から下方に延びるように半導体層中に形成されている。導電層は、絶縁層を介してトレンチを埋めるように形成され且つ半導体層の上面から第1の位置まで下方に延びる。第1半導体拡散層は、複数のトレンチの間に位置する半導体層の上面から第2の位置に達し且つ第2の不純物濃度より小さい第3の不純物濃度を有する。アノード電極は、第1半導体拡散層とショットキー接合されている。半導体層の上面から第2の位置までの長さは、半導体層の上面から第1の位置までの長さの1/2以下である。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】低いオン抵抗を維持したまま、耐圧の向上を図ることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、制御電極、第1主電極、内部電極、絶縁領域、を備える。制御電極は、トレンチの内側に設けられる。第1主電極は、第3半導体領域と導通し、トレンチの外側に設けられる。内部電極は、トレンチ内に設けられ、第1主電極と導通する。絶縁領域は、トレンチの内壁と第1主電極とのあいだ、及びトレンチの内壁と内部電極とのあいだ、に設けられる。内部電極は、制御電極よりもトレンチの底面側の第1領域に含まれる第1内部電極部と、第1領域と、第1主電極と、のあいだの第2領域に含まれる第2内部電極部と、を有する。第1内部電極部とトレンチの内壁との間隔は、第2内部電極部とトレンチの内壁との間隔よりも広い。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の実施形態は、トレンチ構造におけるゲート・ソース間容量を低減できる半導体装置およびその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面側に設けられた第1主電極と、前記半導体層の第2の主面側に設けられた第2主電極と、前記半導体層の前記第1の主面側から前記第2の主面の方向に形成されたトレンチの内部に設けられ、前記第1主電極と前記第2主電極との間に流れる電流を制御する2つの第1制御電極と、前記トレンチの内部において、前記2つの第1制御電極と、前記第2の主面側の底面と、の間に設けられた第2制御電極と、を備える。前記2つの第1制御電極は、前記第1の主面に平行な方向に離間して設けられ、それぞれ第1の絶縁膜を介して前記トレンチの内面に対向し、前記第2制御電極は、第2の絶縁膜を介して前記トレンチの内面と対向する。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

MOSトランジスタの製造方法

【課題】 本発明は、メタルソース/ドレインを有するMOSトランジスタにおいて、メタルソース/ドレインの位置制御且つショットキーバリアハイトの制御の両者を実現できる技術を提供することを課題とする。

【解決手段】 SOI層上にゲート電極構造を形成する工程と、該ゲート電極構造をマスクにSOI層上に窒素添加Ni膜を成膜する工程と、窒素添加Ni膜上にTiN膜を形成する工程と、窒素雰囲気中でアニールしSOI層中にMOSトランジスタのソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極構造をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化アニールする工程とを含むMOSトランジスタの製造方法。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

161 - 180 / 2,965

[ Back to top ]