Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

81 - 100 / 2,965

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

イメージセンサのピクセル縮小のためのコンタクト構造及びその製造方法

【課題】フィルファクターの低下なしで、ピクセル縮小が可能なイメージセンサ及びその製造方法を提供する。

【解決手段】イメージセンサのピクセルは、ピクセル内に互いに電気的に接続が必要なポリシリコン402と活性領域401を有するイメージセンサにおいて、前記ポリシリコン膜が、前記活性領域の上部に一部が重なるように拡張され、前記ポリシリコン膜が、前記活性領域と埋没コンタクト403されるようにする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

成膜装置及び成膜方法

【課題】処理空間内の圧力を高めることができる成膜装置を提供すること。

【解決手段】処理容器2内に、基板であるウエハWの載置領域を備えた載置台3と、この載置台3と対向する天板部材4とを設け、載置台3を昇降機構5により天板部材4側へ上昇させて、載置台3と天板部材4との間で処理空間Sを形成する。載置台3における載置領域の外側領域と天板部材4との少なくとも一方には突起部43が設けられ、前記処理空間Sの形成時にその先端が他方に接触することにより、前記外側領域と天板部材4との間の離間距離が規制され、前記載置領域を囲むように排気用の1mm未満の隙間40が形成される。隙間40が狭小であることから、処理空間S内に反応ガスを封じ込めることができ、処理空間内の圧力が高められる。

(もっと読む)

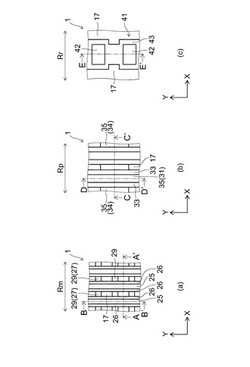

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】電極抵抗および界面抵抗の低下を実現する熱安定性の高いバリアメタル構造を備えた半導体装置を提供すること。

【解決手段】実施形態の半導体装置は、半導体基板1の上に形成されたポリシリコン膜2と、前記ポリシリコン膜上に形成された金属のシリサイド膜10と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜4と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜5と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および閾値電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有するSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。そして、ショットキーバリアダイオード1の閾値電圧Vthを0.3V〜0.7Vにし、定格電圧VRにおけるリーク電流Jrを1×10−9A/cm2〜1×10−4A/cm2にする。

(もっと読む)

二層レジストプラズマエッチングの方法

【課題】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法を提供する。

【解決手段】二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

81 - 100 / 2,965

[ Back to top ]