Fターム[4M104BB05]の内容

Fターム[4M104BB05]に分類される特許

201 - 220 / 2,151

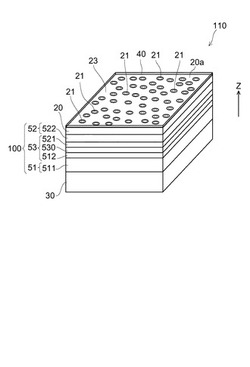

半導体発光素子及びその製造方法

【課題】高輝度化を図ることができる半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態に係る半導体発光素子は、構造体と、第1電極層と、電極層と、無機膜と、を備える。構造体は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、第1半導体層と第2半導体層との間に設けられた発光層と、を有する。電極層は、構造体の第2半導体層の側に設けられる。電極層は、金属部と、複数の開口部と、を有する。金属部は、第1半導体層から第2半導体層に向かう方向に沿った厚さが10nm以上、100nm以下である。開口部は、前記方向に沿って金属部を貫通し、円相当直径が10nm以上、5μm以下である。無機膜は、前記方向に沿った厚さが20nm以上、200nm以下で、金属部の表面及び開口部の内面を覆うように設けられ、発光層から放出される光に対して透過性を有する。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

ノーマリオフ型ヘテロ接合電界効果トランジスタ

【課題】p型不純物のドーピングおよびそのp型不純物の活性化を必要とすることなく、簡便かつ低コストでノーマリオフ型HFETを提供する。

【解決手段】ノーマリオフ型HFETは、厚さt1のアンドープAlxGa1−xN層(11)、この層(11)へ電気的に接続されかつ互いに隔てられて形成されたソース電極(21)とドレイン電極(22)、これらソース電極とドレイン電極との間でAlxGa1−xN層上に形成された厚さt2のアンドープAlyGa1−yN層(12)、ソース電極とドレイン電極との間においてAlyGa1−yN層の部分的領域上でメサ型に形成された厚さt3のアンドープAlzGa1−zN層(13)、およびAlzGa1−zN層上に形成されたショットキーバリア型ゲート電極(23)を含み、y>x>zおよびt1>t3>t2の条件を満たすことを特徴としている。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

ショットキーバリア型半導体装置

【課題】低バイアス領域からリーク電流IRの低減効果を得ることのできるショットキーバリア型半導体装置を提供する。

【解決手段】表面に第1導電型を有する第1の半導体層2を有する半導体基板と、第1の半導体層の表面から所定の深さに設けられ、第1導電型の半導体層よりも低濃度の第1導電型を有する第2の半導体層3と、第1の半導体層の表面から所定の深さに配設されたジャンクションバリアとして第2導電型を有する複数の第3の埋め込み半導体層5と、第1の半導体層の表面で第3の埋め込み層を囲むように環状に形成された、第2導電型を有するガードリング4と、第1の半導体層およびガードリングに接するように配置された金属層6を具備したショットキーバリア型半導体装置であって、第2の半導体層の比抵抗が第1の半導体層の比抵抗よりも高い。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

ショットキーバリア型半導体装置

【課題】リーク電流IRの低減を維持しつつ耐圧の向上をはかることのできるショットキーバリア型半導体装置を提供する。

【解決手段】ショットキーバリア型半導体装置において、ガードリング4の外側で、第1の半導体層の表面から所定の深さに配設されたジャンクションバリア5としての埋め込み半導体層を具備する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

炭化珪素ジャンクションバリアショットキーダイオードおよびその製造方法

【課題】炭化珪素ジャンクションバリアショットキーダイオードの製造において、ハードマスクを使用せずに、pウェル上に選択的にp+領域を形成し、また金属電極とp+領域とコンタクト抵抗を低減する。

【解決手段】n型のエピタキシャル層2の上部全体に高温イオン注入によってp+領域4aを形成し、当該p+領域4aを選択的にエッチングしてp+領域4a下のn型領域を部分的に露出させることにより、そのn型領域の上面より上方へ突出したp+半導体凸部4を形成する。アノード電極は、上記のn型領域の露出した部分およびp+半導体凸部4を覆うように形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】イオン注入を用いることなく2次元正孔ガスの所期の濃度分布を容易且つ確実に得て、電界集中のなだらかな緩和を実現する高信頼性の窒化物半導体装置を得る。

【解決手段】n−GaN基板1のN面上に形成されたn−GaN層2と、n−GaN層上に形成されたAlGaNからなるJTE構造10と、n−GaN層2上に形成されたアノード電極4とを有しており、n−GaN層2のJTE構造10との界面に、アノード電極4から離間するほど正孔濃度が低くなるように、2次元正孔ガスが生成される。

(もっと読む)

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

【課題】

ドーパントが注入されたSiC基板がオーミックコンタクトの形成前に薄くされる場合には、オーミックコンタクトを形成するために堆積された金属は、基板上に堆積されたときにオーム特性を持たないことがある。

【解決手段】

炭化ケイ素半導体デバイスを形成する方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、前記第1の表面にキャリア基板を取り付けるステップとを含む。さらに、前記炭化ケイ素基板を、前記第1の厚さ未満の厚さまで薄くするステップ、前記第1の表面とは反対側の前記薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、前記金属層を局所的にアニールするステップを含む。前記炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

ワイドバンドギャップ逆阻止MOS型半導体装置

【課題】SiCやGaNなどの半導体材料を主要な半導体基板として用いた場合に、大電流を低オン電圧で流すことができ、高信頼性の逆耐圧特性を備えるワイドバンドギャップ逆阻止MOS型半導体装置を提供すること。

【解決手段】SiCのn-型のドリフト層1の一方の主面側に、p+型基板100と、該p+型基板100を貫通して前記n型のSiCのn-型のドリフト層1に達する複数の裏面トレンチ101と、該複数の裏面トレンチ101底部に前記n型のSiCのn-型のドリフト層1とショットキー接合を形成するチタン電極102とを備え、該ショットキー接合領域に対向する他方の主面側領域に、MOSゲート構造を含む活性領域200と、該活性領域200の外周を取り巻く耐圧構造領域203と、該耐圧構造領域203を取り巻き前記他方の主面から前記p+型基板100に達するとともに内部に絶縁膜21が充填されるトレンチ分離層20とを備える構造とする。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

電力用半導体装置

【課題】本発明は、製造プロセスが煩雑でなく、かつ高い絶縁耐力を有する電力用半導体装置の提供を目的とする。

【解決手段】本発明に係る電力用半導体装置は、第1導電型のSiC基板1と、SiC基板1上に形成され、その表面にリセス構造2aが形成された第1導電型のドリフト層2と、リセス構造2aの表面内に配設された第2導電型の終端部3と、終端部3の一端にかかるようにドリフト層2上に形成され、ドリフト層2とショットキー接続するショットキー電極4,5と、終端部3を被うようにドリフト層2上に形成された絶縁膜6と、絶縁膜6上に形成され、ショットキー電極5と電気的に接続された導電膜8とを備える。導電膜8の抵抗値は106(Ω/sq.)以上1013(Ω/sq.)以下である。

(もっと読む)

高耐圧半導体装置

【課題】従来の高耐圧半導体装置の場合よりも耐圧の低下を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタル層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118とを備え、最内周の第1ガードリング層122とエッジターミネーション層120との間隔が3μm〜5μmの範囲内にある高耐圧半導体装置100。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

201 - 220 / 2,151

[ Back to top ]