Fターム[4M104BB05]の内容

Fターム[4M104BB05]に分類される特許

141 - 160 / 2,151

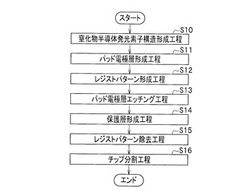

窒化物半導体発光素子の製造方法

【課題】工程数が少なく生産性を向上する窒化物半導体発光素子の製造方法を提供する。

【解決手段】まず、パッド電極層形成工程S11で、窒化物半導体発光素子構造上に、n側パッド電極およびp側パッド電極となるパッド電極層を形成し、レジストパターン形成工程S12で、パッド電極層上に、n側パッド電極およびp側パッド電極を形成する領域を被覆するレジストパターンを形成する。次に、パッド電極層エッチング工程S13で、このレジストパターンをマスクとして、パッド電極層をエッチングしてn側パッド電極およびp側パッド電極を形成する。続いて、このレジストパターンを除去せずに、保護層形成工程S14で、窒化物半導体発光素子構造の表面およびレジストパターン上に絶縁性の保護層を形成した後に、レジストパターン除去工程S15で、レジストパターンを除去する。

(もっと読む)

半導体装置

【課題】本発明は、トレンチの設計自由度が損なわれることなく、プロセス条件に制約されることなく、電気的特性を向上することができる半導体装置を提供する。

【解決手段】半導体装置10は、第1の半導体領域1内のトレンチ15の底部に第4の半導体領域4を介して配設され、隣り合う同士において相互に離間され、第1の半導体領域1よりも高い不純物密度を有する第1の導電型の第5の半導体領域5を備える。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、ドレイン電極12の長手方向の端12A,12Bから長手方向と直交する短手方向に伸ばした仮想線M1,M2よりも長手方向外方に位置すると共にソース電極11に隣接する領域の下のGaN系積層体5、およびドレイン電極12の長手方向の端12A,12Bに長手方向外側に隣接する領域の下のGaN系積層体5に2次元電子ガスが存在しない2次元電子ガス除去領域31が形成されている。2次元電子ガス除去領域31の存在によって、スイッチング時の動的な電界変動によってソース電極11の端部からドレイン電極12の端部へ向かって電子流が集中することを回避できる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体上の銅のめっき

【課題】前面電流トラックを形成したドープ半導体ウェハの銅めっきに関する改善された銅めっき方法を提供する。

【解決手段】前面、裏面およびPN接合を含む半導体を提供し、下層を含む導電トラックのパターンを前記前面が含み、かつ前記裏面が金属接点を含んでおり;前記半導体を一価銅めっき組成物と接触させ;並びに導電トラックの下層上に銅をめっきする。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

金属パターン材料及びその製造方法

【課題】めっき後に細線乃至小ドットの金属パターンを高解像度で形成できる金属パターン材料及び金属パターン材料の製造方法の提供。

【解決手段】特定のめっき形成用光感応材料を6μm未満のピッチで露光する際に、6μmピッチ露光時の最適パワーに対し、100%未満であり、かつ〔(ピッチ(μm)×75/6+25)−30〕〜〔(ピッチ(μm)×75/6+25)+15〕%のレーザーパワーで露光する露光工程と、露光後のめっき形成用光感応材料を現像液で現像する現像工程と、現像後のパターンが形成されためっき形成用光感応材料を、めっき浴比が10未満でめっきを行うめっき工程とを含む金属パターン材料の製造方法である。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

141 - 160 / 2,151

[ Back to top ]