Fターム[4M104BB05]の内容

Fターム[4M104BB05]に分類される特許

101 - 120 / 2,151

半導体デバイス及びその製造方法

【課題】接合障壁ショットキーダイオード及びその製造方法を提供すること。

【解決手段】第1の導電型を有する半導体層と、この半導体層上にあり、半導体層と共にショットキー接合部を形成する金属接点と、半導体層内に半導体領域とを含んでいる。半導体領域と半導体層とが、第1のp−n接合部を、ショットキー接合部と並列に形成する。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、ショットキー接合部に隣接する半導体層内に空乏領域を発生させるように構成され、それによってショットキー接合部を通る逆漏れ電流が制限される。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、第1のp−n接合部のパンチスルーが、ショットキー接合部の降伏電圧よりも低い電圧で起こるように構成される。

(もっと読む)

半導体素子およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体素子およびその製造方法等を提供する。

【解決手段】半導体素子は、有機半導体層と、この有機半導体層と接するように配設された電極と、この電極とは別体として形成され、かつ電極と電気的に接続された配線層とを備えている。半導体素子の製造方法は、基板上に、有機半導体層およびこの有機半導体層と接する電極を形成する工程と、この電極と電気的に接続された配線層を形成する工程とを含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の十分な低減を可能とする半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法は、少なくとも一方の主面を含む領域が単結晶炭化珪素からなる基板を準備する工程と、一方の主面上に活性層23を形成する工程と、基板の前記一方の主面とは反対側の他方の主面を含む領域を研削する工程と、他方の主面を含む領域を研削する工程において形成されたダメージ層22Cを除去する工程と、ダメージ層22Cが除去されることにより露出した主面に接触するように裏面電極を形成する工程とを備え、一方の主面は{0001}面に対するオフ角が50°以上65°以下となっている。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】窒化物半導体層上の層間絶縁膜の開口部が、電界の集中が緩和される形状に安定して精度良く形成された窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層30と、窒化物半導体層30上に配置された第1の絶縁膜41と、第1の絶縁膜41上に配置された第2の絶縁膜42と、窒化物半導体層30上に互いに離間して配置された第1及び第2の主電極51,52と、第1及び第2の主電極51,52間で第2の絶縁膜42上に配置され、第1及び第2の絶縁膜に設けられた開口部を介して窒化物半導体層に接続するフィールドプレート60とを備える窒化物半導体装置であって、開口部において、窒化物半導体層30の表面と第1の絶縁膜41の側面とのなす第1の傾斜角が、窒化物半導体層30の表面と第2の絶縁膜42の側面を延長した線とのなす第2の傾斜角よりも小さく形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを十分に抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたゲート電極3、及び平面視でゲート電極3を間に挟む2個のオーミック電極4a及び4bと、が設けられている。更に、ゲート電極3上方に形成され、ゲート電極3並びにオーミック電極4a及び4bから絶縁分離されたフィールドプレート6が設けられている。フィールドプレート6のオーミック電極4a及び4bを互いに結ぶ方向における少なくとも一方の端部は、平面視で、オーミック電極4a及び4bとゲート電極3との間に位置する。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

蒸着用マスク、蒸着用マスクの製造方法、電子素子および電子素子の製造方法

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の第1主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。

【課題】印刷法による少ない工程数のメリットを生かしつつ、より微細であり、絶縁性の低下がなく、導電部寸法精度の高い、配線部材および電子素子の製造方法を提供することを目的とする。また、配線部材、積層配線、電子素子、電子素子アレイ及び表示装置を提供することを目的とする

【解決手段】基板上にエネルギーの付与により臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程、紫外領域のレーザーを用いたレーザーアブレーション法により、濡れ性変化層に凹部を形成する工程、凹部に導電性インクを塗布して導電部を形成する工程、を含み、前記濡れ性変化層の凹部のパターン形成と同時に、前記臨界表面張力を変化させて高表面エネルギー領域のパターン形成が行われることを特徴とする配線部材の製造方法、電子素子の製造方法、及び、それにより得られた配線部材、電子素子を提供する。また、電子素子アレイ及び表示装置を提供する。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、保護膜の境界面での膜厚を厚くし、はんだが金属膜の下方に侵入し難い半導体装置を提供することを目的とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

(もっと読む)

Ga2O3系半導体素子

【課題】Ga2O3系化合物を半導体として用い、これに適合したショットキー特性が得られる電極を有するGa2O3系化合物半導体素子を提供する。

【解決手段】本発明のGa2O3系半導体素子は、n型導電性を有するβ−Ga2O3化合物半導体からなるn型層と、前記n型層上に形成されたショットキー特性を有する電極とを備え、前記電極は、Au、Pt、あるいはNi及びAuの積層体のいずれかによって構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてオーミック特性を良好にし、かつ、酸・アルカリによる腐食に対し高い耐性を有することが可能な技術を提供することを目的とする。

【解決手段】半導体装置は、不純物が添加された高濃度不純物領域2を有する窒化物半導体層1と、高濃度不純物領域2上に順に積層された下地電極層3及び主電極層4を含む電極11とを備える。主電極層4は、窒化物半導体層1に対して下地電極層3よりも仕事関数が近い第1金属と、水素よりもイオン化傾向が小さい第2金属とからなる合金を主成分として含む。下地電極層3は、主電極層4よりも窒素との反応性が高い金属を主成分として含み、かつ、第1金属を含む。

(もっと読む)

太陽電池及びその製造方法

【課題】改善された光電変換効率を有する太陽電池を提供する。

【解決手段】太陽電池1は、光電変換部10と、第1の電極21と、第2の電極22とを備える。第1の電極21は、光電変換部10の一主面10aの上に配されている、第2の電極22は、光電変換部10の他主面10bの上に、第1の電極21よりも小面積に配されている。第1の電極21は、第1の第1電極導電層21aと、第2の第1電極導電層21cとを含む。第1の第1電極導電層21aは、光電変換部10の一主面10aの上に配されている。第2の第1電極導電層21cは、第1の第1電極導電層21aの上に配されている。第1の第1電極導電層21aは、第2の第1電極導電層21cよりも高い光反射率を有する。第2の第1電極導電層21cは、第1の第1電極導電層21aよりも低い電気抵抗を有する。

(もっと読む)

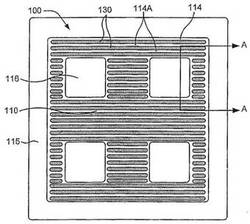

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCを用いて、逆方向特性が良好なショットキーダイオードを高い歩留まりで得る。

【解決手段】図1(b)に示されるように、バリアメタル21を部分的にエッチングする(電極層エッチング工程)。電極層エッチング工程によってバリアメタル21がエッチングされた領域における半導体層10中に、埋め込み絶縁層を形成する(埋め込み絶縁層形成工程)。図1に示される製造方法においては、この埋め込み絶縁層形成工程は、半導体層エッチング工程、絶縁層形成工程、エッチバック工程からなる。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

101 - 120 / 2,151

[ Back to top ]