Fターム[4M104BB05]の内容

Fターム[4M104BB05]に分類される特許

81 - 100 / 2,151

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

ニッケル膜の成膜方法

【課題】CVDにより不純物の少ないニッケル膜を高スループットで成膜することができるニッケル膜の成膜方法を提供すること。

【解決手段】基板上に、成膜原料として、分子構造中に窒素−炭素結合をもつ配位子を有し、配位子中の窒素がニッケルに配位した構造を有するニッケル含有化合物を用い、還元ガスとして、アンモニア、ヒドラジン、およびこれらの誘導体から選択された少なくとも1種を用いたCVDにより初期ニッケル膜を成膜する第1工程と、初期ニッケル膜の上に、成膜原料として、分子構造中に窒素−炭素結合をもつ配位子を有し、配位子中の窒素がニッケルに配位した構造を有するニッケル含有化合物を用い、還元ガスとして水素ガスを用いたCVDにより主ニッケル膜を成膜する第2工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高い逆方向耐圧VR及び低いリーク電流IRを維持したまま、順方向降下電圧VFを低くしたり、逆回復時間trrを短くしたりすることが可能な半導体装置を提供する。

【解決手段】n+型半導体層112とn−型半導体層114とを有する半導体基体110と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130とを備える半導体装置であって、半導体基体110には、n−型半導体層114の表面で濃度が最も高くなるように重金属としての白金が拡散されている。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれと第1半導体層との接合部がそれぞれ第1と第2の接合部からなり、第1接合部は、第1半導体層と接続する単位アノード部部分が正孔が多数キャリアの第2半導体層であるP−N接合部であり、第2接合部は、第1半導体層と接続する単位アノード部部分が金属によって構成されたショットキー接合部である、ようにした。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、ワイドバンドギャップ材料を用いて電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれの、少なくとも第1半導体層と接合する部分が、所定の半導体材料を用いて正孔を多数キャリアとするように構成されてなる第2半導体層であり、第1半導体層と第2半導体層との接合部においてはP−N接合が形成されてなる、ようにした。

(もっと読む)

オーミック電極とその形成方法

【課題】コンタクトホールを形成するために用いられたレジスト膜を、硫酸を含むエッチング液を利用して除去することが可能なオーミック電極の形成方法を提供する。

【解決手段】積層電極部2を形成する積層電極部形成工程と、積層電極部2を熱処理するアニール工程と、熱処理後の積層電極部2を被覆部3で被覆して被覆電極部4を形成する被覆電極部形成工程と、被覆電極部4を覆うように半導体層1の表面に絶縁体膜5を形成する絶縁体膜形成工程と、被覆電極部4に対応して開口7が形成されているレジスト膜6を絶縁体膜5の表面にパターニングするレジスト膜形成工程と、レジスト膜6の開口7から露出する絶縁体膜5を除去して被覆電極部4を露出させる露出工程と、硫酸を含むエッチング液を用いてレジスト膜6を除去するレジスト膜除去工程を備えている。被覆部3の材料は、金又は白金である。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

成膜装置及び成膜方法

【課題】処理空間内の圧力を高めることができる成膜装置を提供すること。

【解決手段】処理容器2内に、基板であるウエハWの載置領域を備えた載置台3と、この載置台3と対向する天板部材4とを設け、載置台3を昇降機構5により天板部材4側へ上昇させて、載置台3と天板部材4との間で処理空間Sを形成する。載置台3における載置領域の外側領域と天板部材4との少なくとも一方には突起部43が設けられ、前記処理空間Sの形成時にその先端が他方に接触することにより、前記外側領域と天板部材4との間の離間距離が規制され、前記載置領域を囲むように排気用の1mm未満の隙間40が形成される。隙間40が狭小であることから、処理空間S内に反応ガスを封じ込めることができ、処理空間内の圧力が高められる。

(もっと読む)

半導体素子のための非活性化保護リング

【課題】半導体素子、特にショットキーダイオードのような金属対半導体整流接合を組み込む半導体素子を提供する。

【解決手段】保護リングは、ショットキー接合又はショットキーダイオードの一部である半導体領域に形成される。保護リングは、高抵抗領域を形成するために、半導体コンタクト層を完全にアニール処理することなく半導体コンタクト層内へのイオン注入によって形成される。保護リングは、層のエッジ部か又は代替的に層のエッジ部からある一定距離を離して位置することができる。ショットキー金属接点は、層の上に形成され、ショットキー接点のエッジ部は、保護リングの上に配置される。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

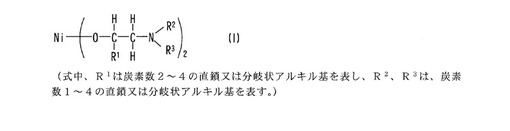

アルコキシド化合物及び薄膜形成用原料

【課題】融点が低く液体の状態で輸送が可能であり且つ蒸気圧が大きく気化させやすく、CVD法等の化合物(プレカーサ)を気化させて薄膜を形成する方法において用いる薄膜形成用原料として好適なニッケル化合物を提供すること。

【解決手段】下記一般式(I)で表されるアルコキシド化合物。 (もっと読む)

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】接合障壁ショットキーダイオード及びその製造方法を提供すること。

【解決手段】第1の導電型を有する半導体層と、この半導体層上にあり、半導体層と共にショットキー接合部を形成する金属接点と、半導体層内に半導体領域とを含んでいる。半導体領域と半導体層とが、第1のp−n接合部を、ショットキー接合部と並列に形成する。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、ショットキー接合部に隣接する半導体層内に空乏領域を発生させるように構成され、それによってショットキー接合部を通る逆漏れ電流が制限される。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、第1のp−n接合部のパンチスルーが、ショットキー接合部の降伏電圧よりも低い電圧で起こるように構成される。

(もっと読む)

81 - 100 / 2,151

[ Back to top ]