Fターム[4M104BB26]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | MoSi (259)

Fターム[4M104BB26]に分類される特許

1 - 20 / 259

半導体装置

半導体装置の製造方法

【課題】電極と半導体基板が良好にオーミック接合している半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の電極形成面に、単原子の金属イオンを注入するイオン注入工程と、金属イオンが注入された半導体基板をアニール処理して半導体基板にシリサイド層を形成するアニール工程と、アニール工程の後に、半導体基板の電極形成面に電極を形成する電極形成工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】SiC半導体基板の裏面電極は、低コンタクト抵抗を実現するために、ニッケル等のシリサイド形成用メタル膜を堆積後、PDAとして摂氏1000度程度の熱処理を必要とする。この熱処理を通常の熱処理やRTAで実行する場合には、ウエハの表面側がアルミニウム等の融点を超えるため、アルミニウム膜等の形成前に実施しなければならないという制約がある。また、既存の紫外線レーザを用いたレーザアニールでは、コンタクト抵抗を十分に下げられないという問題がある。

【解決手段】本願の一つの発明は、SiC基板の表面側にアルミニウム系メタル膜が形成された状態で、裏面にシリサイド形成用メタル膜を成膜し、この裏面に対してレーザビームによってシリサイド化処理を実行する半導体装置の製造方法であって、このレーザビームを、前記シリサイド形成用メタル膜を実質的に透過しない波長域に属する可視光とするものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、Si基板の表面にシリサイド層を形成しつつ、Si基板の裏面における低融点金属とSi基板のSiとの相互拡散を防止できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体素子の製造方法は、Si基板の裏面に低融点金属を形成する工程と、該Si基板の表面に高融点金属層を形成する工程と、該高融点金属層の上にレーザ吸収層を形成する工程と、該レーザ吸収層にレーザ光を照射し、該低融点金属と該Si基板のSiとの相互拡散を防ぐように該低融点金属の温度を低く保ちつつ、該レーザ吸収層と該高融点金属層の界面、及び該高融点金属層と該Si基板の界面にシリサイド層を形成する工程と、該レーザ吸収層をエッチングする工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

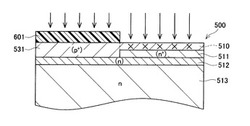

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

1 - 20 / 259

[ Back to top ]