Fターム[4M104DD04]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | 側壁堆積膜の利用 (769)

Fターム[4M104DD04]に分類される特許

761 - 769 / 769

集積回路技術におけるシリサイド化スペーサ

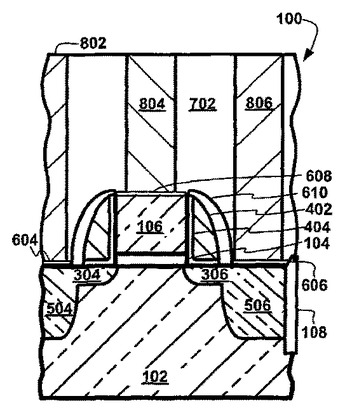

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

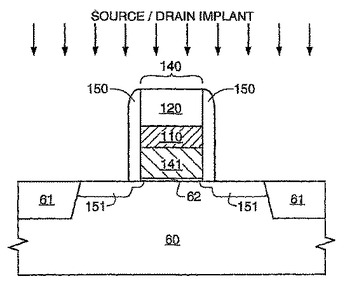

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

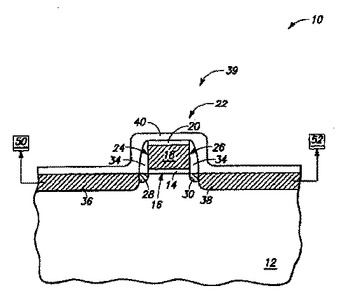

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

761 - 769 / 769

[ Back to top ]