Fターム[4M104DD26]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 基板への不純物導入 (557)

Fターム[4M104DD26]に分類される特許

201 - 220 / 557

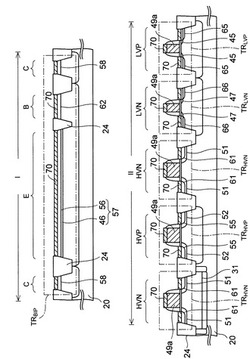

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】イオン注入された領域であるイオン注入領域が除去されない炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】この発明にかかる炭化珪素半導体装置の製造方法は、炭化珪素層の表層にイオン注入により環状のイオン注入領域を選択的に形成する工程と、前記イオン注入領域が形成された前記炭化珪素層を活性化アニールする工程と、前記炭化珪素層の表面の全面に犠牲酸化膜を形成する工程と、前記イオン注入領域にあたる前記犠牲酸化膜上にフォトレジストを形成する工程と、前記フォトレジストをマスクとして前記犠牲酸化膜を除去する工程と、前記フォトレジストと前記犠牲酸化膜をマスクとして前記犠牲酸化膜と前記活性化アニールの際に前記炭化珪素層の表層に形成される変質層を除去する工程とを備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた好適な構造のnチャネル型トランジスタおよびpチャネル型トランジスタを提供することを目的の一とする。

【解決手段】第1の酸化物半導体層と電気的に接続し、第1の材料を含む第1の導電層と第2の材料を含む第2の導電層の積層構造でなる第1のソース電極またはドレイン電極と、第2の酸化物半導体層と電気的に接続し、第1の材料を含む第3の導電層と第2の材料を含む第4の導電層の積層構造でなる第2のソース電極またはドレイン電極と、を有し、第1の酸化物半導体層には、第1のソース電極またはドレイン電極の第1の導電層が接触し、第2の酸化物半導体層には、第2のソース電極またはドレイン電極の第3の導電層および第4の導電層が接触する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

配線構造の製造方法、及び配線構造

【課題】製造コストが低い配線構造の製造方法、及び配線構造を提供する。

【解決手段】本発明に係る配線構造の製造方法は、基板10を準備する基板準備工程と、基板10上に半導体層を形成する半導体層形成工程と、半導体層上にドーパントを含むドーパント含有半導体層を形成するドーパント含有半導体層形成工程と、ドーパント含有半導体層の表面を、水分子を含ませた酸化性ガス雰囲気中で加熱することにより、ドーパント含有半導体層の表面に酸化層を形成する酸化層形成工程と、酸化層上に合金層を形成する合金層形成工程と、合金層上に配線層を形成する配線層形成工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】読み出しマージンの大きなSRAMセルを提供する。

【解決手段】第1インバータ回路と、出力ノードが前記第1インバータ回路の入力ノードに接続され、入力ノードが前記第1インバータ回路の出力ノードに接続された、第2インバータ回路と、ソース及びドレインの一方が前記第1インバータ回路の出力ノードに接続され、他方がビット線に接続された、第1アクセストランジスタとを具備する。前記第1インバータ回路は、第1トランジスタを含む。前記第1アクセストランジスタ及び前記第1トランジスタのそれぞれは、基板上に形成され、前記基板面に対して垂直に延びる半導体柱と、前記半導体柱を前記基板面に平行な方向で取り囲むように形成され、前記半導体柱にチャネル領域を形成させる、ゲート電極と、前記半導体柱の下端部又は上端部にそれぞれ接続されるソース及びドレインとを備える。前記第1トランジスタの電流駆動力は、前記第1アクセストランジスタのそれよりも高い。

(もっと読む)

炭化珪素半導体装置

【課題】炭化珪素半導体装置のpベースオーミックコンタクトは、高濃度イオン注入により形成されるp++層と金属電極とで構成される。高濃度イオン注入を室温で行うと、p++層の結晶が著しく劣化しプロセス不良の原因となるため、高温中で注入を行う方法が用いられる。デバイスのスイッチング損失等の観点から、pベースオーミックコンタクト抵抗率はより低いことが望ましい。

【解決手段】上記イオン注入工程に於いて、炭化珪素ウェハの温度を175〜300℃、望ましくは175〜200℃に保持しておく。175〜300℃でのイオン注入により形成されるp++領域を用いたpベースオーミックコンタクト抵抗率は8E−4Ωcm2以下となり、300℃を超える温度でイオン注入した場合よりも低くなる。又、プロセス不良も発生しない。

(もっと読む)

貼り合わせ基板の製造方法

【課題】接合強度を十分に維持できると共に、短時間で分離することができる、貼り合わせ基板の製造方法を提供する。

【解決手段】この貼り合わせ基板の製造方法は、III族窒化物半導体基板及び第1支持基板のうち少なくとも一方上に、表面粗さRrmsが0.1〜10000nmの表面を有する第1緩衝膜を形成する工程と、第1緩衝膜を介して、第1支持基板にIII族窒化物半導体基板を貼り合わせる工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

半導体構造体およびその製造方法(自己整合型ショットキー・ダイオード)

【課題】 自己整合型ショットキー・ダイオード及びその製造方法を提供する

【解決手段】 ショットキー障壁ダイオードは、セミコンダクタ・オン・インシュレータ(SOI)基板内の第2の導電型のドーピングを有するドープ保護環(リング)を含み、さらにダミー・ゲート電極の一方の側の、第2の導電型とは反対型の第1の導電型のドーピングを有する第1導電型ドープ半導体領域を含み、そしてショットキー障壁構造部は他方の側がドープ保護環により囲まれる。ショットキー障壁領域は、側部をダミー・ゲート電極及びドープ保護環により囲むことができる。ドープ保護環は、第2の導電型のドーピングを有するゲート側第2導電型ドープ半導体領域の非金属化部分を含む。ショットキー障壁領域は、側部を、ゲート側ドープ半導体領域及びSTI側ドープ半導体領域を含むドープ保護環により囲むことができる。ショットキー障壁ダイオードの設計構造体もまた提供する。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

半導体装置

【課題】強度を保持しつつ、導通時の抵抗を低減可能な電力用の半導体装置を提供する。

【解決手段】半導体装置10は、基板領域1と、基板領域1上に設けられ、炭化珪素を含む半導体材料からなり、複数の凹部が形成されたドリフト領域2と、側壁に配設されたアノード電極3と、凹部の側壁を挟んでアノード電極3と互いに対面するように側壁に配設され、かつ、アノード電極3と絶縁されたカソード電極4とを有する。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、電子供給層3上方に形成されたソース電極7s、ドレイン電極7d及びゲート電極7gと、が設けられている。ソース電極7sと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっており、ドレイン電極7dと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっている。

(もっと読む)

半導体装置の製造方法

【課題】集積度が高く低ノイズで高速な半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1導電型領域と第2導電型領域とに対して共通のコンタクトホールを形成するホール形成工程と、前記第1導電型領域および前記第2導電型領域の少なくとも一方に対して不純物を注入する注入工程と、前記コンタクトホールに導電材料を充填してシェアードコンタクトプラグを形成するプラグ形成工程とを含む。前記注入工程では、前記第1導電型領域と前記シェアードコンタクトプラグとがオーミック接触し、かつ前記第2導電型領域と前記シェアードコンタクトプラグとがオーミック接触するように、前記第1導電型領域および前記第2導電型領域の少なくとも一方に対して不純物を注入する。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ゲート絶縁膜における、ゲートトレンチ側面上の部分の厚さの増大を抑制しつつ、ゲートトレンチ底面上の部分の絶縁破壊を抑制することのできる半導体装置を提供すること。

【解決手段】 半導体装置1において、表面31がSi面となるように、SiCからなるエピタキシャル層3を形成する。エピタキシャル層3には、その表面31から掘り下がったゲートトレンチ6を形成する。また、ゲートトレンチ6の底面8および側面7上には、側面7上の部分(絶縁膜側部10)の厚さT1に対する底面8上の部分(絶縁膜底部11)の厚さT2の比が0.3〜1.0となるように、ゲート絶縁膜9を形成する。また、ゲートトレンチ6には、ゲート絶縁膜9を介してゲート電極12を埋設する。

(もっと読む)

201 - 220 / 557

[ Back to top ]