Fターム[4M104DD26]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 基板への不純物導入 (557)

Fターム[4M104DD26]に分類される特許

541 - 557 / 557

ショットキーバリアダイオード

【課題】 耐圧を確実に確保しながら、順方向降下電圧が低くすることが出来るショットキーバリアダイオードを提供する。

【解決手段】 低濃度N型エピタキシャル層2に、深さ2μm、不純物濃度1×1016/cm3〜6×1017/cm3程度の高濃度P型ガードリング領域5を形成することにより、耐圧を高くすることが可能となる。さらにガードリング領域5の表面に、深さ0.5μm、不純物濃度1×1020/cm3〜6×1021/cm3程度の高濃度P型領域8を形成することにより、耐圧を高くするのみでなく静電気サージ耐量も確保できることとなる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SiC基板に対して良好なオーミック接触を得ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】 n+型SiC層1の露出面の状態を荒らす工程と、荒らされたn+型SiC層1の露出面に電極を形成する工程とを有し、前記荒らす工程は、前記露出面についての研磨処理又はレーザー照射Lを有することを特徴とする。

(もっと読む)

シリサイド領域を有する半導体デバイスの製造方法

【課題】本発明は、半導体デバイスの製造方法及び半導体デバイスを含む集積回路の製造方法を提供する。

【解決手段】本発明の半導体デバイス(100)を製造する方法は、とりわけ、基板(110)上にゲート構造(120)を形成するステップオ、及びゲート構造(120)の近くの基板(110)にソース/ドレイン領域(190)を形成するステップを含む。本方法は、更に、ゲート構造(120)及び基板(110)をドライエッチングするステップ、及びゲート構造(120)及び基板(110)をドライエッチングするステップに続いて、ソース/ドレイン領域にフッ素を配置して、フッ化したソース/ドレインを形成するステップを含む。その後、本方法は、ゲート構造(120)とフッ化したソース/ドレインに金属スイサイド領域(510,520)を形成するステップを含む。

(もっと読む)

ショットキダイオードを含む半導体装置及びその製造方法

【課題】 本発明は、比較的低いコストにより、比較的低いシリーズ抵抗を有するショットキダイオードを含む半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 ショットキダイオードにおいて、ウェル領域の表面領域の不純物濃度はそのウェル領域の不純物濃度よりも小さく、ウェル領域の表面領域より深い、所定の深さ領域の不純物濃度はそのウェル領域の不純物濃度よりも大きく分布する、ウェル領域と同一型の不純物の濃度分布をウェル領域内に設定する。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

ゲート酸化膜形成法

【課題】厚さを異にする複数のゲート酸化膜を1回の熱酸化処理により形成する際に厚いゲート酸化を効率的に行なう。

【解決手段】半導体基板10の一方の主表面にフィールド絶縁膜12を形成した後、酸化膜14a,14bとして犠牲酸化膜又はゲート酸化膜を形成する。素子孔12a内にレジスト層16をマスクとし且つ酸化膜14aを介してアルゴン(又はフッ素)イオンを1又は複数回の注入処理により注入してイオン注入層18を形成する。酸化膜14a,14bを犠牲酸化膜としたときはレジスト層16及び酸化膜14a,14bの除去後に素子孔12a,12b内にゲート酸化膜を形成する。酸化膜14a,14bをゲート酸化膜としたときはレジスト層16の除去後に酸化膜14a,14bをエッチングで薄くしてから酸化膜14a,14bを厚くする。イオン注入層18を形成したことで14b対応のゲート酸化膜より14a対応のゲート酸化膜が厚くなる。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 Bモード故障とシリサイド未形成による動作不良の双方を解消した半導体装置を提供する。

【解決手段】 素子分離領域により画成された第1および第2の素子領域を有する基板と、前記第1の素子領域に形成された第1のポリシリコンゲート電極を有する第1の電界効果トランジスタと、前記第2の素子領域に形成された第2のポリシリコンゲート電極を有する第2の電界効果トランジスタと、前記第1のポリシリコンゲート電極と前記第2のポリシリコンゲート電極とを結んで前記素子分離領域上を延在するポリシリコンパターンと、前記第1のポリシリコンゲート電極の表面および前記第2のポリシリコンゲート電極の表面、さらに前記ポリシリコンパターンの表面に形成され、前記第1のポリシリコンゲート電極から前記第2のポリシリコンゲート電極まで、前記ポリシリコンパターン上を延在するシリサイド層とよりなる半導体装置において、前記シリサイド層は前記ポリシリコンパターン上において層厚が増大した厚膜部を含み、前記厚膜部では、前記シリサイド層の表面が上方に突出する。

(もっと読む)

半導体装置及び半導体装置の製造方法

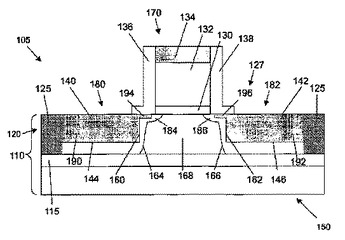

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

ショットキ・コンタクトを形成するために半導体上に導電性炭素材料を堆積するための方法、及び半導体コンタクト・デバイス

【課題】 本発明は、ショットキ・コンタクト(16)を形成するために半導体(14)上に導電性炭素材料(17)を堆積する方法に関する。

【解決手段】 本発明の方法は、半導体(14)をプロセス・チャンバ(10)内に導入するステップと、プロセス・チャンバ(10)の内部(10')を所定温度に加熱するス

テップと、プロセス・チャンバ(10)を第1所定圧力以下に減圧するステップと、プロセス・チャンバ(10)の内部(10')を第2所定温度に加熱するステップと、少なく

とも炭素を含むガス(12)を、第1所定圧力よりも高い第2所定圧力に達するまで導入するステップと、少なくとも炭素を含むガス(12)から、半導体(14)上に導電性炭素材料(17)を堆積することにより、半導体(14)上に堆積した炭素材料(17)がショットキ・コンタクト(16)を形成するステップを備えている。

(もっと読む)

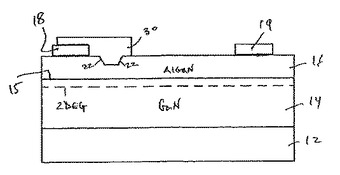

III族窒化物電流制御デバイスおよび製造方法

III族窒化物デバイスが、名目上オフ、すなわち、エンハンスメントモードのデバイスを作製するための凹部電極を含む。凹部電極を設けることによって、デバイス中の電流の流れを阻止するために、電極が非能動であるときに2つのIII族窒化物材料の境界面に形成された導電チャネルが中断される。電極はショットキー接点または絶縁金属接点であり得る。名目上オフの特性を有する整流器デバイスを形成するために、2つのオーム接点を設けることができる。電極が形成された凹部は傾斜側面を有することができる。電極は、デバイスの電流運搬電極と組み合わせて幾つもの幾何学配置で形成可能である。電極が凹部でないとき、名目上オンのデバイス、すなわち、ピンチ抵抗が形成される。ダイオードは、絶縁体を貫通してAlGaN層に達する非凹部のオーム接点およびショットキー接点を設けることによっても形成される。  (もっと読む)

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

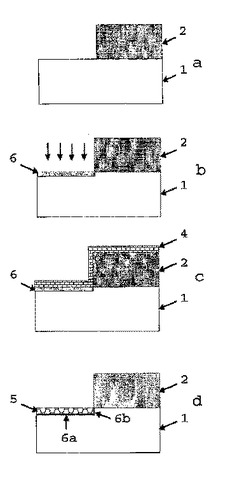

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

PN接合ダイオード装置及びその製造方法

【課題】より小型が可能なPN接合ダイオード装置及びその製造方法を提供することにある。

【解決手段】PN接合ダイオードのカソード電極22及びアノード電極23を共に、シリコン基板10の一方の主面に形成することにより、カソード電極22及びアノード電極23とをリードフレーム26に、ワイヤー等で接続することなく、接着することを可能にする。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

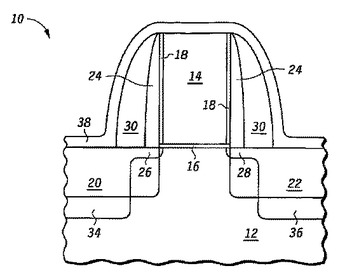

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

541 - 557 / 557

[ Back to top ]