Fターム[4M104DD26]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 基板への不純物導入 (557)

Fターム[4M104DD26]に分類される特許

161 - 180 / 557

電界効果トランジスタ

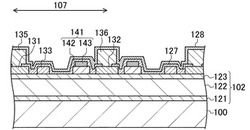

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、電極のパターン形成性に優れるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第1半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第2半導体領域6bと、第1半導体領域6aにオーミック接触するオーミック接合層7と、第2半導体領域6bにショットキー接触するショットキー接合層8と、を備え、オーミック接合層7が、第1半導体領域6a側からチタンとニッケルとを含む合金からなると共に、その上にモリブデンを主成分とする金属層を有し、ショットキー接続層8が、モリブデンを主成分とする金属からなることを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

裏面オーミックコンタクトを備えた縦型の半導体デバイス

【課題】オーミックコンタクトを有する半導体デバイスを、経済的に製造できるようにする。

【解決手段】半導体デバイス10は、半導体基板12と、該半導体基板の表面上にあり、半導体基板の解離温度未満の解離温度を有するエピタキシャル層14と、半導体基板内に形成された漸増キャリヤー濃度帯16と、金属層18とから構成される。漸増キャリヤー濃度帯は、約1000Åの厚さを有し、エピタキシャル層と反対の半導体基板の表面から該表面と反対側の表面に向かって伸びており、該反対側の表面に向かってドーパントの濃度が漸次低下している。金属層は、漸増キャリヤー濃度帯との境界20においてオーミックコンタクトを形成する。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む金属窒化物含有多結晶金属層32からなるバリア層と、これに積層された金属層31とを有している。

(もっと読む)

整流素子

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子を提供する。

【解決手段】ショットキー電極3は、SiCよりなるn-半導体層2とショットキー接触し、かつSiCよりなるp型半導体層5a,5bと電気的に接続している。ショットキー電極3とカソード電極4との電位差が変化することにより、ショットキー電極3とカソード電極4との間に電流を流す状態と、p型半導体層5a,5bに囲まれるn-半導体層2を空乏層化させてショットキー電極3とカソード電極4との間の電流経路を遮断する状態とを選択可能である。n-半導体層2とショットキー電極3との間のショットキー障壁φBn1が、0.68eV<φBn1<1.05eVであり、かつ250℃の温度でも、そのショットキー接触を確保できる。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

ガリウム窒化物又は他の窒化物ベースのパワーデバイスのためのゲルマニウムを含む低オーミックコンタクト

基板(120)、基板の上のIII族窒化物層(102、104,406)、及び、III族窒化物層の上の電気的コンタクト(108a、108b)を含む装置。電気的コンタクトは、導電性材料の複数層(110〜116)を有するスタックを含み、スタック内の前記層の少なくとも1つがゲルマニウムを含む。スタック内の層は、アルミニウム銅を含むコンタクト層(116)を含み得る。スタックは、チタン又はチタン合金層、アルミニウム又はアルミニウム合金層、及び、ゲルマニウム又はゲルマニウム合金層、を含み得る。スタック内の少なくとも1つの層は、約1%から約5%の間のゲルマニウム含有量を有するアルミニウム又はチタン合金を含み得る。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】オフセット構成となる場合があった。

【解決手段】第1導電型のドレイン領域と、前記ドレイン領域上に形成された第2導電型のボディ領域と、前記ボディ領域を貫通し、底面部分が前記ドレイン領域に達するトレンチと、前記トレンチに埋設されたゲート電極と、前記ゲート電極と、前記トレンチの側面及び底面とを絶縁する絶縁部と、を有し、前記ボディ領域は、前記トレンチ側面に近づくにつれ前記トレンチの深さ方向に深くなり、前記絶縁部は、トレンチ壁面に形成されたゲート絶縁膜と、トレンチ底部に形成された底部埋込絶縁膜とを備え、前記底部埋込絶縁膜は、前記トレンチの深さ方向に深くなるにつれ、前記ゲート酸化膜よりも厚くなる厚い絶縁膜部分を有し、前記厚い絶縁膜部分は、前記ボディ領域の最低部より前記トレンチの深さ方向に対して所定の深さに位置されている半導体装置。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素を材料とする半導体ウェハから半導体装置を製造する方法において、表面電極と半導体基板とのショットキー接合、裏面電極と半導体基板とのオーミック接合を確保することと、製造工程を簡略化する。

【解決手段】半導体ウェハの表面に表面Mo電極を形成した後で、半導体ウェハの裏面に裏面Ni系電極を形成し、形成した表面Mo電極および裏面Ni系電極を同時にシンター処理する。表面Mo電極は、900℃以上のシンター処理を行っても、半導体基板とのショットキー接合を確保できる。裏面Ni系電極が半導体基板とオーミック接合するために必要な高温(例えば900℃以上)で、表面電極と裏面電極のシンター処理を同時に行うことができるため、製造工程が簡略化される。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーボン膜の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化できるようにする。

【解決手段】オーミック電極5を形成するための金属層15の形成前にレーザ光の吸収効果の高いカーボン層14を形成しておき、その上に金属層15を形成してからレーザアニールを行うようにしている。これにより、金属層15を構成する金属がカーボン層14を構成する炭素(C)やn+型基板1を構成するシリコン(Si)または炭素と反応してオーミック電極5が形成されるため、カーボン層14を除去する必要がない。また、レーザアニール時にカーボン層14を用いているため、レーザ光の吸収率を高くすることができ、オーミック電極5のコンタクト抵抗の低抵抗化を十分に行うことが可能となる。したがって、カーボン膜14の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化することが可能となる。

(もっと読む)

半導体装置の製造方法。

【課題】本発明は、埋込みビットラインの抵抗を減少させ高速動作に有利な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ハードマスク膜をバリアとして半導体基板をエッチングし、複数の活性領域を画定するトレンチを形成するステップと、ハードマスク膜が突出部となるように前記トレンチ内部を一部ギャップフィルするギャップフィル膜を形成するステップと、突出部の両側側壁を覆うスペーサを形成するステップと、ドープドエッチング障壁膜をエッチングバリアとしてスペーサのうち何れか1つのスペーサを除去するステップと、残留するスペーサをエッチングバリアとして前記ギャップフィル膜をエッチングし、活性領域の一側側壁を露出させる側壁トレンチを形成するステップと、を含む。

(もっと読む)

161 - 180 / 557

[ Back to top ]