Fターム[4M104DD86]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 気相との反応 (289)

Fターム[4M104DD86]に分類される特許

281 - 289 / 289

半導体装置の製造方法

【課題】タングステン層の抵抗値の上昇を抑えることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、半導体基板(1)上に層間絶縁膜(2)を形成するステップと、前記層間絶縁膜(2)の内部に延びるコンタクトホールを形成するステップと、前記コンタクトホールの底面部及び側壁部にバリアメタル層(4)を形成するステップと、前記バリアメタル層(4)が形成された前記コンタクトホールに、フッ素を含む材料からタングステン層(5)を形成するステップと、ポストパージにより前記タングステン層(5)から前記フッ素を除去するステップとを具備している。

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

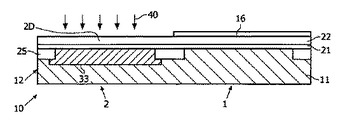

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】本発明は、信頼性の高く、且つしきい値電圧の変化量を高めることが可能な半導体不揮発性記憶素子を有する半導体装置の作製方法を提供する。また、信頼性の高い半導体不揮発性記憶素子を有する半導体装置を、大面積基板を用いて製造する方法を提供する。

【解決手段】本発明は、固溶限界を超えるシリコンを有する固溶体をターゲットとしてスパッタリングを行い、固溶体の主成分である金属元素の導電層と、シリコン粒子とからなる導電膜を成膜した後、金属元素の導電層を除去してシリコン粒子を露出する。また、当該シリコン粒子をフローティングゲート電極とする半導体不揮発性記憶素子を有する半導体装置を作製する。

(もっと読む)

半導体材料の予めパッシベーション化された表面を金属被覆するための方法及びその方法によって得られる材料

本発明は、半導体材料の予めパッシベーション化した表面を金属被覆するための方法及びその結果得られる材料に関する。本発明は、マイクロエレクトロニクスに適用可能であり、材料(2)の表面を前処理することにより、材料内に水素原子又は金属元素を吸着可能な結合を形成するステップ、表面をパッシベーション化化合物に露出することにより、好ましくは表面の直下に位置する一又は複数の層をパッシベーション化するステップ、及び表面(4)を水素原子へ又は金属元素に露出することにより、該表面を金属被覆するステップを含むことを特徴とする。  (もっと読む)

(もっと読む)

ゲート電極構造のトリミングを制御する方法

ゲート電極構造の第1寸法の決定によりゲート電極構造のトリミングをコントロールする方法および処理ツールであって、目標トリム寸法を選択し、プロセスパラメータのセットを生成するためにプロセスモデルに対して第1寸法および目標トリム寸法をフィードフォワードし、ゲート電極構造上にトリミングプロセスを実行する。トリミングプロセスを実行する際には、プロセスパラメータをコントロールし、ゲート電極構造をトリミングし、ゲート電極構造のトリム後の寸法を計測する。目標トリム寸法が得られるまで、トリミングプロセスは少なくとも1回は繰り返し行われる。トリム後寸法は、新たなプロセスパラメータのセットを生成するために、フィードバックされる。  (もっと読む)

(もっと読む)

ゲート電極をトリミングする方法

第1寸法を有するゲート電極層を備えたゲート電極構造をトリミングする方法および処理ツールを提供する。反応層は、ゲート電極構造と反応することによって形成される。そして、この反応層は、化学エッチングによって、ゲート電極構造の未反応部分から選択的に除去される。これにより、第1寸法よりも小さい第2寸法を有するトリミングされたゲート電極構造が形成される。トリミング処理は、反応層の形成が実質的に自己制限的となるプロセス条件にて実行される。トリミング処理は、ゲート電極構造の寸法をさらに減少させるために繰り返し行うことができる。  (もっと読む)

(もっと読む)

トランジスタ製造プロセスにおいて、high−kゲート絶縁体を組み入れる方法

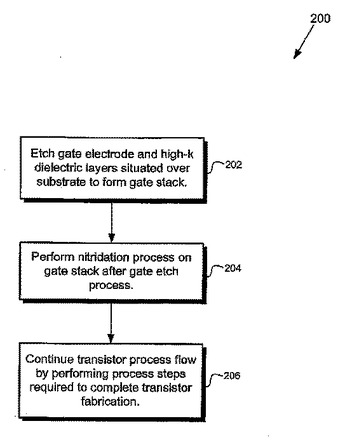

本発明の例示的な一実施形態は、その上に位置するhigh-k誘電体層と、このhigh-k誘電体層上に位置するゲート電極層と、を含む基板(104)上に電界効果トランジスタを形成する方法である。この方法は、基板(104)上に位置するhigh-k誘電体部(106)と、high-k誘電体部(106)上に位置するゲート電極部とを含むゲートスタック(102)を形成するように、ゲート電極層およびhigh-k誘電体層をエッチングするステップ(202)を含む。この例示的な実施形態によれば、この方法は、ゲートスタック(102)上で窒化プロセスを実行するステップ(204)をさらに含む。この窒化プロセスは、ゲートスタック(102)のサイドウォール(110)を窒化するように、窒素を含むプラズマを利用するステップによって実行することができる。この窒化プロセスの結果、窒素がhigh-k誘電体部(106)に入り込み、窒素がhigh-k誘電体部(106)中に酸素拡散バリアを形成するようにされてよい。  (もっと読む)

(もっと読む)

シーケンシャル流量堆積を使用して金属層を堆積させる方法。

【課題】 シーケンシャル流量堆積を使用して金属層を堆積させる方法を提供することである。

【解決手段】 シーケンシャル流量堆積を使用して良好な表面モホロジを有する金属層を堆積させる方法は、処理チャンバ内の基板を交互に金属−カルボニル前駆ガスと、還元ガスとに曝すことを含む。金属−カルボニルプリカーサガスにさらされる間、薄い金属層は、熱分解によって基板上に堆積され、その後の還元ガスに金属層を曝すことは、金属層から反応副生成物の除去するのを助ける。所望の厚さを有する金属層が達成されるまで、金属−カルボニルプリカーサガスと、還元ガスとの曝露ステップは、繰り返されることができる。

(もっと読む)

電極構造体の形成方法及び半導体装置の製造方法

【課題】 ポリメタル構造を有するゲート電極において、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くする。

【解決手段】 半導体基板10上にゲート絶縁膜11を介してポリシリコン膜12を堆積した後、該ポリシリコン膜12の上に、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16からなるバリア膜を形成する。バリア膜の上にタングステン膜18を堆積して、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18からなる電極構造体を形成した後、該電極構造体に対して750℃以上の熱処理を施す。このようにすると、第1の窒化チタン膜14中の窒素がチタン膜15及びポリシリコン膜12に拡散して、ポリシリコン膜12とタングステン膜18との間に新たな窒化チタン膜19が形成されると共に、ポリシリコン膜12の表面に窒化シリコンからなり厚さの小さい反応層20が形成される。

(もっと読む)

281 - 289 / 289

[ Back to top ]