Fターム[4M104FF06]の内容

Fターム[4M104FF06]の下位に属するFターム

T、Y、逆L型、逆T型 (276)

台形 (304)

階段状 (86)

フィールドプレート又はその変形 (254)

Fターム[4M104FF06]に分類される特許

641 - 655 / 655

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

薄膜トランジスタの製造方法、半導体装置、電気光学装置及び電子機器

【課題】 1度の不純物注入工程によってLDD構造を形成することができる薄膜トランジスタの製造方法等を提供する。

【解決手段】 本発明は、ゲート絶縁膜上に、チャネル長方向において端部から中央部に向けて徐々に膜厚が厚くなる傾斜部を有するゲート電極20を形成する工程を含む薄膜トランジスタうの製造方法を提供する。該ゲート電極20をマスクとしてリンなどの不純物元素のイオン打ち込みを行うことで、最終的には図3(B)に示すようなソース/ドレイン領域としての高濃度のN+型不純物拡散領域22a、低濃度のN-型不純物拡散領域22b、及びチャネル領域24が形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

凹凸薄膜つき基板およびその製造方法

【課題】 薄膜太陽電池に好適に用いられる透明導電膜つき基板において、好ましい凹凸形状をもつ基板を得る。

【解決手段】 透明導電膜の凹凸形状においては、その凹凸形状の凸部の頂上が略部分球面からなり、明瞭な稜線が見られない凹凸形状を透明導電膜が好ましい。その凹凸形状は、ピラミッド状の凸状突起群をもつ透明導電膜として、CVD法を用いてフッ素ドープ酸化錫膜を作製し、その凸状突起群を遊離砥粒で適切に研磨することによって製造する。

(もっと読む)

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

素子配置基板及びその製造方法

【課題】簡便に製造することができ、しかも基板上のパターン膜上に形成された薄膜にクラックが入ることを抑制することができる素子配置基板を提供する。

【解決手段】基板上に1以上のパターン化された膜を備える素子配置基板であって、上記パターン膜の少なくとも一つは、断面形状が上部の半楕円形状部と下部の順又は略垂直テーパ形状部とにより構成され、上記順又は略垂直テーパ形状部は、平均厚さが50Å以上、3000Å以下である。

(もっと読む)

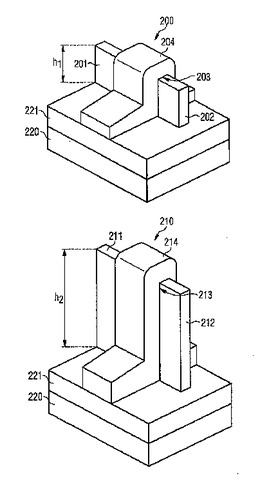

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

電気的な構成要素と該構成要素の電気的な接続導体とを有するシステム並びに該システムを製造する方法

本発明は、少なくとも1つの電気的な接触面(20)を有する少なくとも1つの電気的な構成要素(2)と、該構成要素(2)の前記接触面(20)を電気的に接触させるための少なくとも1つの電気的な接続導体(3)と、前記構成要素(2)の上に配置された少なくとも1つの絶縁層(4)とを有し、該絶縁層(4)が該絶縁層(4)の厚さ方向でこれを貫通する少なくとも1つの開口(42)を有し、該開口(42)が前記構成要素(2)の接触面(20)に向き合って配置されており、前記絶縁層(4)が前記開口(42)を制限する側面(43)を有し、前記電気的な接続導体(3)が前記側面(43)に配置された少なくとも1つの金属化層(30)を有しているシステムに関する。該システムは、前記金属化層(30)が前記接触面(20)に対し斜めに配向されていることを特徴としている。斜めに配向された金属化層によっては、前記絶縁層の上に配置された前記接続導体の区分と前記絶縁層と前記構成要素とが互いに機械的にかなり結合される。有利には金属化層は数μmの厚さを有している。機械的な減結合によって、前記接続導体と前記絶縁体と前記構成要素とは、熱的な膨張係数の異なる材料から成っていることができる。本発明は特に、出力半導体構成要素を大きな面積で電気的に接触させるために使用される。  (もっと読む)

(もっと読む)

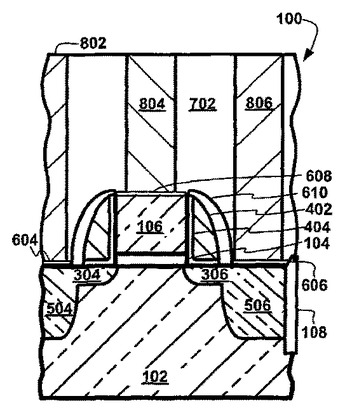

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

641 - 655 / 655

[ Back to top ]