Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

901 - 920 / 1,113

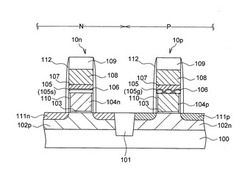

半導体装置及びその製造方法

【課題】 ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、ポリシリコン層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極の抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 STIによりフィールド絶縁膜を形成した半導体基板に、比較的ゲート酸化膜が厚くゲート長が長い高耐圧駆動MOSトランジスタを形成する時、STIに起因して熱応力に変化が生じて、半導体基板に欠陥が生じることを防止する。

【解決手段】 高耐圧駆動MOSトランジスタのゲート酸化膜102は、パイロ酸化により酸化成長させたSi酸化膜と、SiH4ガスの熱分解による減圧気相成長により成長させたSi酸化膜で構成される2層膜を、N2OもしくはNOガス中での急速加熱により酸化すると共に、微量に窒素を含むSi酸化膜を順次成長させたSi酸化膜系の絶縁膜で構成する。

(もっと読む)

マグネトロンスパッタリング装置用Ti−W材

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,W,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のTi−Wから成るコンタクトバリアー層のAl含有量を原子数で1×1018個/cm3以下、Al,Ti,W以外の重金属元素の含有量が5×1016個/cm3以下およびアルカリ金属の含有量が5×1016個/cm3以下に形成することが可能であり、Al濃度が1ppm以下であることを特徴とするマグネトロンスパッタリング装置用高純度Ti−W材である。

(もっと読む)

エッチング液、エッチング液及びその結果構造物を用いた導電性配線を含む薄膜トランジスタ基板の製造方法

【課題】銀(Ag)配線用エッチング液を提供すること。また、エッチング液を利用する銀(Ag)配線形成方法を提供すること。さらに、エッチング液を利用する薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】本発明により、エッチング液、これを用いた配線形成方法及び薄膜トランジスタ基板の製造方法が提供される。エッチング液は下記化学式1で表示される物質、酢酸アンモニウム及び超純水を含む。

(化学式1)

M(OH)XLY

(ただし、前記式でMはZn、Sn、Cr、Al、Ba、Fe、Ti、SiまたはBであり、Xは2または3であり、LはH2O、NH3、CN、COR、NH2Rであり、Yは0、1、2または3であり、Rはアルキル基である。)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に熱処理を施したとしてもコンタクトプラグの周囲に形成された窒化膜に生じる熱変形を抑え、半導体装置の電気的特性を維持することができる半導体装置の製造方法を提供する。

【解決手段】 工程14では、シリコン基板12上の層間絶縁膜14にコンタクトホール15aを形成する。工程15では、シリコン基板12におけるコンタクトホール15aの下側に不純物31を導入する。工程16では、導入した不純物31を、例えば、800℃の温度の熱処理によって拡散してドレイン電極23の領域を広げる。工程17及び18では、コンタクトホール15aの内面にチタン膜28及び窒化チタン膜29を形成する。工程19では、半導体装置11に、例えば、520℃の温度の熱処理を施して、シリコン基板12におけるバリアメタル26とシリコン基板12との間にシリサイド膜16を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 デバイスを形成する領域における半導体膜の電位を基板電位と同じにするか、別にするかのレイアウトの自由度を増加させることができる半導体装置を得る。

【解決手段】 半導体基板と、半導体基板上に形成された埋め込み絶縁膜と、埋め込み絶縁膜上に形成された半導体膜と、半導体膜の一部の領域を囲うように形成されたトレンチ分離と、トレンチ分離で囲まれた領域内に形成され、半導体膜及び埋め込み絶縁膜を貫通して半導体基板に接続された基板電位コンタクトとを有する。

(もっと読む)

CMOS半導体装置

【課題】CMOS半導体装置において、pチャネルMOSトランジスタの動作速度を向上させる。

【解決手段】第1の素子領域と第2の素子領域とを含む基板と、前記第1の素子領域上に第1のゲート絶縁膜を介して形成されたn型半導体材料よりなる第1のゲート電極と、前記第1の素子領域中、前記第1のゲート電極の両側に形成された一対のn型拡散領域と、前記第2の素子領域上に第2のゲート絶縁膜を介して形成されたp型半導体材料よりなる第2のゲート電極と、前記第2の素子領域中、前記第2のゲート電極の両側に形成された一対のp型拡散領域とよりなるCMOS半導体装置において、前記第2の素子領域は、前記第1の素子領域のホール移動度よりも大きなホール移動度を有する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 窒化シリコン膜のパターニングに付随して生じる欠陥を低減することができる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】 窒化シリコン膜5を全面に形成した後、その上に酸化シリコン膜6を形成する。次に、ゴミ等を除去するために水洗浄処理を行う。次に、酸化シリコン膜6及び窒化シリコン膜5のパターニングを行う。このとき、窒化シリコン膜5の形状は、その上に酸化シリコン膜6が存在しているため逆テーパ形状となる。次に、半導体膜4をパターニングする。次に、ソース電極7及びドレイン電極8を半導体膜4上に形成する。このようにして薄膜トランジスタ10が形成される。このとき、ソース電極7及びドレイン電極8の間に、金属膜の残部や堆積物等のゴミ11が発生することがある。このような場合であっても、窒化シリコン膜5が逆テーパ形状となっているため、ゴミ11とソース電極7及びドレイン電極8との間で段切れが生じる。

(もっと読む)

成膜方法およびコンピュータにより読み取り可能な記憶媒体

【課題】CVD法において、500℃未満の低い成膜温度でも異常成長のない良質の金属窒化膜を成膜することが可能な成膜方法を提供すること。

【解決手段】成膜温度に加熱された被処理基板に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより被処理基板上に金属窒化膜を直接堆積させる期間を含む第1段階と、同様に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより前記第1段階で堆積された初期の金属窒化膜の上にさらに金属窒化膜を堆積させて所定の膜厚とする第2段階とを含み、前記第1段階および前記第2段階ともに、前記金属化合物ガスおよび窒素含有還元ガスを供給する第1ステップと、前記金属化合物ガスを停止して前記窒素含有還元ガスを供給する第2ステップとからなるサイクルを1サイクル以上繰り返す。

(もっと読む)

半導体素子の製造方法

【課題】ゲート抵抗およびゲート間の干渉を減らすことが可能なタングステンゲート電極を有する半導体素子の製造方法を提供する。

【解決手段】半導体基板上にゲート酸化膜11とポリシリコン膜12,14と窒化膜を形成し、これらをパターニングしてポリゲートを形成する。前記ポリゲートの側面にスペーサ18を形成する。全表面上に犠牲窒化膜19を形成し、全面に層間絶縁膜20を形成する。前記窒化膜が露出するように、前記層間絶縁膜20と前記ポリゲート上に形成された犠牲窒化膜19を平坦除去する。前記窒化膜を除去すると同時に、前記犠牲窒化膜19の上部を除去する。前記窒化膜の除去により露出した側面に絶縁膜スペーサ22を形成し、前記犠牲窒化膜が除去された部分21に絶縁膜を充填する。前記窒化膜が除去された部分にタングステンゲート23を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 膜厚の異なるゲート絶縁膜を備えた構成の半導体装置で、ゲート絶縁膜剥離の工程の短縮を図りながら優れた特性を有する半導体装置の製造方法を提供する。

【解決手段】 NANDフラッシュメモリで、周辺回路の高電圧駆動トランジスタHV−P、HV−Nと低電圧駆動PチャンネルトランジスタLV−Pについて、ゲート電極7の形成後に、不純物のイオン注入時に、リソグラフィ処理で同時にゲート絶縁膜6、8を除去し、イオン注入を行う。これにより、低電圧駆動トランジスタLV−Pのシリコン基板1表面がシリコンガウジングを発生するが、特性に悪影響を与えることなくリソグラフィ工程を統合できる。

(もっと読む)

積層構造を備えた集積回路構造およびその製造方法

【課題】銅または銅合金からなる導電性のダマシン構造を含んだ集積回路構造のバリア層の形成方法を提供する。

【解決手段】導電構造(16、22)の側壁には、金属層、中間層が交互に積層され、少なくとも3つの層を含んだ積層構造(32)が設けられている。積層構造(32)の中に非常に薄い層があるにもかかわらず、外部電流を用いて銅を電解析出するために必要な導電率の高さに起因した銅の拡散に対する、高い障壁作用が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】 容量素子と拡散層との接続安定性を向上させる。

【解決手段】 半導体装置100は、DRAM部102を含み、DRAM部102に、シリコン基板101内に形成された第1拡散層108と、メタル上部電極128と、容量絶縁膜126と、メタル下部電極124とからなり、シリコン基板101上に形成されたMIM容量122と、第1拡散層108と、メタル下部電極124とを電気的に接続する第1の接続プラグと、を含む。第1の接続プラグは、第1シリコンプラグ112と、第1シリコンプラグ112の上部に接して設けられた第1シリサイド層146とから構成されるとともに、上面がメタル下部電極124に接して設けられ、MIM容量122に接続されている。

(もっと読む)

キャパシタおよびその製造方法

【課題】

DRAMに用いられる王冠型構造のキャパシタにおいて、厚い絶縁膜に形成された深孔の内壁に下部電極を形成した後、下部電極外壁周囲の絶縁膜を溶液エッチングすると、機械的強度が減少するため、下部電極が倒壊しペアビット不良が発生する問題を回避する。

【解決手段】

王冠型もしくは円柱状からなる内側下部電極と王冠型の外側下部電極とからなる2重下部電極構造とし、導電プラグが形成された層間絶縁膜上に窒化シリコン膜を設け、内側の電極底部は窒化シリコン膜を貫通して導電プラグと接続し、外側の電極底部は窒化シリコン膜の表面に張出すように形成する。これにより下部電極自身が窒化シリコンの側壁に加えて窒化シリコンの上面にも接している構造となるので横方向に加わる力に対して機械的強度を向上させることができ、倒壊を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】良好な抵抗値を示すコンタクトプラグを備えた半導体装置の製造方法を提供する

こと。

【解決手段】

コンタクトプラグを備えた半導体装置の製造方法であって、半導体シリコン基板表面に設けられた高濃度N導電型拡散層の表面部分および層間絶縁層により形成されたコンタクトホールを通じて、加速エネルギーを30〜120keVの範囲とし、注入量を1.0×1013〜5.0×1014/cm2の範囲としてインジウムイオンを注入するこにより、前記コンタクトホール下部の前記高濃度N導電型拡散層の表面部分にインジウム含有層を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体工業に使用するための三成分系材料を無電解メッキする組成物

本発明は、半導体工業における型NiM−R(但し、MはMo、W、Re、Crであり、RはB、Pであるものとする)の無電解メッキされた三成分系ニッケル含有金属合金の使用に関する。殊に、本発明は、半導体構造素子中での銅の拡散およびエレクトロマイグレーションを阻止するための、バリヤー材料としてかまたは選択的なケーシング材料としての前記のメッキされた三成分系のニッケル含有金属合金の使用に関する。 (もっと読む)

無欠陥の導体で深く広い開口部を埋め込む方法

集積回路メタライゼーションまたはパッケージングビアの比較的大きな開口あるいはフィーチャ(102)が、順に2つのめっきあるいは電着処理によって埋め込まれる。第1の電着処理は、大きな、高アスペクト比のフィーチャ(102)を第1の層(104)でコンフォーマルに覆い、内部キャビティ(116)を画定する。第2の層(118)を形成する第2の電着処理は、異なる溶液を使用して、第1の電着処理によって残された内部キャビティ(116)をボトムアップ式で埋め込む。コンフォーマル性が第1の電着処理においてレベラーの使用によって典型的に引き起こされるのに対して、促進剤及び抑制剤が第2の電着処理においてボトムアップ埋め込みを促進するために使用されうる。但し、いずれの処理も3つの添加剤のうちの何かを使用することができる。 (もっと読む)

半導体集積回路装置の製造方法

【課題】ポリメタルゲート構造とデュアルゲート構造とを採用するCMOS LSIにおいて、ゲート電極の一部を構成する高融点金属膜の酸化と、ゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素の拡散とを共に抑制することのできるライト酸化処理技術を提供する。

【解決手段】水素ガスおよび酸素ガスと水素ガスとから触媒により合成された水蒸気を含む混合ガスを半導体ウエハ1Aの主面に供給し、エッチングによって削られたゲート電極の端部下のゲート絶縁膜のプロファイルを改善する熱処理を、ゲート電極の一部を構成する高融点金属膜が実質的に酸化されず、かつゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素がゲート酸化膜を通って基板に拡散しない低熱負荷条件下で行う。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 良好な電気的特性のトランジスタが得られるようにし、これによって半導体装置の微細化や高密度化を可能にし、さらには3次元に積み重ねることをも可能にした、半導体装置の製造方法とこの製造方法によって得られる半導体装置を提供する。

【解決手段】 基体1上に形成された結晶性半導体膜3のうち第1の部分以外の少なくとも第2の部分及び第3の部分に不純物を注入する第1の工程と、第2の部分および第3の部分にそれぞれソース及びドレインを形成する第2の工程とを備える。第2の工程において、少なくとも第2の部分および第3の部分に対して加熱処理を施すことにより、第1の部分の少なくとも一部をシードとする第2の部分及び第3の部分の固相エピタキシー過程を誘起する。

(もっと読む)

901 - 920 / 1,113

[ Back to top ]