Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

961 - 980 / 1,113

エッチング液組成物及び薄膜トランジスタ表示板の製造方法

【解決課題】配線が良好なプロファイルが得られるエッチング液組成物及び、これを利用した薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】本発明は、60乃至75重量%のリン酸、0.5乃至15重量%の硝酸、2乃至15重量%の酢酸及び0.1乃至15重量%の硝酸アルミニウムを含有するエッチング液組成物及び前記エッチング液組成物を利用した薄膜トランジスタ表示板の製造方法を提供する。

(もっと読む)

原子層堆積のための表面のプラズマ前処理

集積回路内のデュアルダマシン構造のコンフォーマルなライニングのための方法および構造を提供する。好ましい実施形態は、多孔性物質で形成された開口を覆うコンフォーマルなライニングの提供に向けられる。トレンチが絶縁層内に形成される(100)。その後、その層が、特別のプラズマプロセスで適切に処理される(101)。このプラズマプロセスに引き続き、自己制限的、自己飽和的原子層堆積(ALD)反応(115)が、細孔の著しい埋め込みなしに起こり、改善された相互接続を形成する。 (もっと読む)

受け渡し機構及び処理装置

【課題】押し上げピンの昇降の際に、パーティクルを発生させるような接触や破損するような衝突や摺動を防止することができる処理装置を提供する。

【解決手段】ウエハWを載置する載置台202に複数設けられたピン挿入孔312に押し上げピン311が嵌入されている。押し上げピン311は、上端面が平坦であり、下端には貫通しない範囲で嵌合穴314が形成されている。嵌合穴314には位置決め駆動ピン315の上端部分が挿入され、位置決め駆動ピン315の下端は押し上げ部材316に貫装して固定されている。押し上げピン311の外径は、ピン挿入孔312内径よりもやや小さくなっており、僅かな隙間313ができるようにする。ピン挿入孔312はウエハWの裏面と載置202の上面との間の空間S1と、載置台202の裏面側(下方)の空間S2とを隙間313を介して連通している。

(もっと読む)

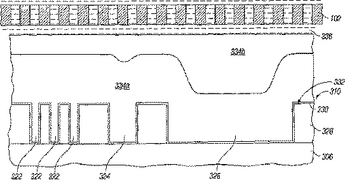

欠陥のない薄い及び平坦なフィルム加工

本発明のプロセスは半導体ウエハー表面に銅配線を形成する。該プロセス中、最初に、狭い(322)及びラージ(326)フィーチャーを該ウエハーの上部表面に提供し、そして、電着工程を使用することにより1次銅層(334A)を堆積する。該1次銅層は該フィーチャーを完全にふさぎ、そして、狭いフィーチャー上に平坦な表面及びラージフィーチャー上に平坦でない表面を形成する。電気化学メカニカル堆積工程を使用することにより、2次銅層(334B)を該1次銅層上に堆積し、狭い及びラージフィーチャー上に平坦な銅層を形成する。このプロセス工程後、電解研磨工程を使用して平坦な銅層の厚みを薄くする。  (もっと読む)

(もっと読む)

半導体装置

【課題】表面電極が設けられた半導体装置の構造を簡素化することができる。

【解決手段】半導体装置100においては、ゲート電極101およびソース電極104として、はんだ接続をすることが可能な金属であるCuが用いられている。そのため、従来の技術のように、ゲート電極およびソース電極の上部に別途はんだ接続が可能なメタル層を設ける必要がない。

(もっと読む)

表面の被覆プロセス

【課題】ポリマー及び有機高分子、電着され得て特定の金属の中にある固体、最終的に沈殿又は重力により堆積され得る固体を表面に確実に位置決めし、その材料を表面に付着させる共通のプロセスを提案すること

【解決手段】本発明は、表面上に材料を堆積又は付着することに関する。本発明は、第1材料及び第2材料による表面の被覆プロセスに関し、次の諸工程を含む:

− 前記表面上に前記第1材料をする工程、

− 前記表面上に配置された前記第1材料の中に前記第2材料の前駆体分子を挿入する工程、

− 被覆された前記表面上で、且つ前記表面上に配置された前記第1材料内部に前記第2材料が形成されるように、前記第1材料の中に挿入された前記第2材料の前駆体分子を前記第2材料へ転化する工程。

本発明のプロセスの目的は、あらゆるタイプの表面上にあらゆるタイプの材料を堆積することである。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】良好なコンタクトを得ることが可能なコンタクトホールを備えた半導体装置を提供する。

【解決手段】単結晶シリコン基板51の表面上にN型またはP型の不純物拡散層52を形成する際に、不純物拡散層52中の不純物濃度を適宜設定する。すると、図2(A)に示すRTN法を用いた熱処理時に、チタンシリサイド層57の成長を適度に抑制して最適化することができる。その結果、不純物拡散層52の接合深さが浅い場合でも、工程4におけるRTN法を用いた熱処理時に、コンタクトホール55の底面部に形成されたチタンシリサイド層57が成長し過ぎて不純物拡散層52を突き抜けるのを防止可能になり、チタンシリサイド層57と単結晶シリコン基板51とが直接接続されてショートするコンタクトリークが生じなくなる。

(もっと読む)

半導体装置とその製造方法

【課題】

酸化シリコンより誘電率の高い高誘電率絶縁膜を有する半導体装置を提供する。

【解決手段】

半導体装置の製造方法は、(a)シリコン基板の活性領域表面にSiOまたはSiONの界面層を形成し、(b)界面層上方に酸化シリコンより高い誘電率を有するHfSiON等の高誘電率のゲート絶縁膜を形成し、(c)ゲート絶縁膜上方にポリシリコンのゲート電極を形成し、(d)高誘電率のゲート絶縁膜形成前後の少なくとも一方で、基板表面をパッシヴェーション処理し、(e)少なくともゲート電極、高誘電率のゲート絶縁膜をパターニングして絶縁ゲート電極構造を形成し、(f)絶縁ゲート電極構造両側の活性領域にソース/ドレイン領域を形成する。

(もっと読む)

パルス化高周波源電力を使用するプラズマゲート酸化プロセス

半導体基板上にトランジスタデバイスのゲートを形成する方法は、プラズマリアクタの真空チャンバに基板を配置するステップと、チャンバの真空圧力を維持しつつ酸素を含むプロセスガスをチャンバ内へ導入するステップとを含む。連続した「オン」タイム中に真空チャンバ内のプラズマ生成領域にプラズマを生成し、制御可能なデューティーサイクルを画成する「オン」インターバル及び「オフ」インターバルのうちの、連続した「オン」インターバルを分離する連続した「オフ」インターバル中に、プラズマのイオンエネルギーが減衰するのを許容することにより、数オングストローム程度の厚さの酸化物絶縁層が基板に表面に形成される。酸化物絶縁層の形成中に、デューティーサイクルは、絶縁層におけるイオン衝撃による欠陥の形成を制限するように限定され、真空圧力は、絶縁層における汚染による欠陥の形成を制限するように限定される。導電性ゲート電極が絶縁層の上に形成される。 (もっと読む)

半導体装置とその製造方法

【課題】 トランジスタを形成する際に、そのトランジスタの下方に形成されている膜が受ける熱的ダメージを低減することができる半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜37の上に遮蔽膜38を形成する工程と、遮蔽膜38の上に第2絶縁膜39と非晶質半導体膜40とを順に形成する工程と、非晶質半導体膜40にエネルギービームを照射し、少なくとも薄膜トランジスタのチャネルとなる部分の非晶質半導体膜40を溶融して多結晶半導体膜41にする工程と、上記チャネルの上の多結晶半導体膜41上にゲート絶縁膜43aとゲート電極44aとを順に形成する工程と、ゲート電極44aの横の多結晶半導体膜41にソース/ドレイン領域41aを形成し、該ソース/ドレイン領域41a、ゲート絶縁膜43a、及びゲート電極44aでTFT60を構成する工程と、を有する半導体装置の製造方法による。

(もっと読む)

パルス化高周波源電力を使用する選択プラズマ再酸化プロセス

トランジスタゲート選択酸化プロセスは、半導体基板を収容した真空チャンバ内へ、真空チャンバの真空圧力を維持しつつ酸素を含むプロセスガスを導入するステップを含む。連続した「オン」タイム中に真空チャンバ内のプラズマ生成領域にプラズマを生成し、制御可能なデューティーサイクルを画成する「オン」インターバル及び「オフ」インターバルのうちの、連続した「オン」インターバルを分離する連続した「オフ」インターバル中に、プラズマのイオンエネルギーが減衰するのを許容することにより、数オングストローム程度の厚さの酸化物絶縁層が形成される。酸化物絶縁層の形成中に、デューティーサイクルは、絶縁層におけるイオン衝撃による欠陥の形成を制限するように限定され、真空圧力は、絶縁層における汚染による欠陥の形成を制限するように限定される。 (もっと読む)

半導体装置及びその製造方法

【課題】遮断周波数を向上すべくコレクタ層を高濃度化した場合にも、それに付随した寄生容量の増大を好適に抑制することのできる半導体装置を提供する。

【解決手段】p型シリコン基板1に設けられた素子分離膜3に囲繞されたn型不純物を含む活性領域2aをコレクタ層とし、その活性領域2aを含むp型シリコン基板1の上面に設けられたSiGe合金層4の上にエミッタ層として機能するn型拡散層5を形成する。またSiGe合金層4のうちでエミッタ層の直下に位置する第1合金層4aをベース層とするとともに、それに隣接する部分を外部ベース層として機能するp+拡散層10とする。更に活性領域2aの表面にそのベース層の直下の部分を囲繞するようにn型不純物の添加された不純物領域20を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】二酸化シリコン換算膜厚が5nm未満の極薄ゲート絶縁膜上にメタルゲート電極を形成したMISFETにおいて、メタルゲート電極を酸化させることなくゲート絶縁膜の欠陥を修復する。

【解決手段】単結晶シリコン基板1の主面上に形成した二酸化シリコン換算膜厚が5nm未満のゲート絶縁膜9A上にゲート電極材料であるW膜11Aを形成した後、水分/水素分圧比がW膜11Aを実質的に酸化せず、シリコンを酸化するような割合に設定された水分+水素混合ガス雰囲気中でシリコン基板1を熱処理することにより、W膜11A直下のゲート絶縁膜9Aの欠陥を修復する。

(もっと読む)

表面被覆方法、及び該方法を使用するマイクロエレクトロニクス相互接続の作製、並びに集積回路

本発明は、基板の表面を、金属材料から作られる核生成フィルムで被覆する方法に関し、前記表面は、導電性又は半導電性表面であり、凹部及び/又は凸部を含む。 本発明方法は、有機フィルムを表面上に蒸着する工程であって、前記フィルムの厚さが、その自由面が、導電性又は半導電性表面(その上に、フィルムが蒸着されている)の凹部及び/又は凸部に共形的にならうものから成る工程;金属材料の前駆体を、表面上に蒸着した有機フィルムに挿入する工程であって、前記表面上に有機フィルムを蒸着させることから成る工程と同時の又はその後に続く工程;及び金属材料の前駆体を金属材料に変換する工程にある。 本発明方法は、集積回路、超小型電子相互接続及びマイクロシステムの製造のために使用することができる。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】白金族金属、白金族合金または白金族金属の導電性酸化物を主成分とする膜を電極材料に用いた容量素子を有するDRAMの微細化を推進する。

【解決手段】酸化シリコン膜43に溝44を形成した後、あらかじめ酸化シリコン膜43の下層に形成しておいた導電性下地膜42をカソード電極とする電解メッキ法によって、溝44の内部にPt膜45を形成する。その後、酸化シリコン膜43をエッチングで除去した後、Pt膜45をマスクにして導電性下地膜42をドライエッチングすることにより、Pt膜45とその下部に残った導電性下地膜42とで容量素子の下部電極を形成する。

(もっと読む)

ルテニウム層堆積装置及び方法

本発明の実施形態は、四酸化ルテニウム含有ガスから基板表面上にルテニウム含有層を形成するための装置及び方法を提供する。一般に、方法には、基板表面を四酸化ルテニウム蒸気にさらして、基板表面上に触媒層を形成するステップと、続いて基板表面上のデバイス構造を少なくとも1つの堆積プロセスによって充填するステップとが含まれる。一実施形態において、ルテニウム含有層は、外部容器内で四酸化ルテニウムを生成し、その後、生成した四酸化ルテニウムガスを処理チャンバ内に位置する温度制御された基板表面に分配することによって基板表面上に形成される。他の実施形態において、ルテニウム含有層が四酸化ルテニウム含有溶媒を用いて、基板表面上に形成される。他の実施形態において、溶媒は四酸化ルテニウム含有溶媒から分離され、残りの四酸化ルテニウムは基板表面上にルテニウム含有層を形成するために用いられる。 (もっと読む)

半導体集積回路装置の製造方法

【課題】高速動作が可能なLDD型MISFETと、かつ高電圧駆動が可能なLDD型MISFETとを内蔵する半導体集積回路装置を低コストで実現する。

【解決手段】高速動作が可能なMISFETは、ゲートサイドウオール層に自己整合された高濃度領域に金属シリサイド層を有し、高電圧駆動が可能なMISFETは、上記ゲートサイドウオール層の幅よりも大きい幅を有するLDD部を有し、そのLDD部に接して高濃度領域を有し、そしてその高濃度領域に金属シリサイド層を有する。

(もっと読む)

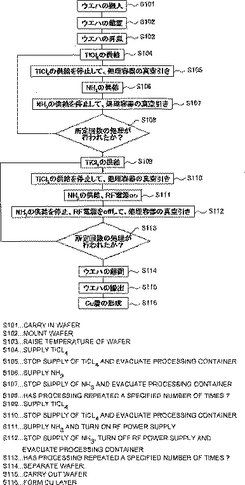

成膜方法、半導体装置の製造方法、半導体装置および成膜装置

処理容器内の被処理基板に成膜する成膜方法であって、ハロゲン元素を含まない有機金属化合物からなる第1の原料ガスを前記処理容器内に供給した後、前記第1の原料ガスを前記処理容器内から除去する第1の工程と、水素または水素化合物を含む第2の原料ガスを前記処理容器内に供給した後、前記第2の原料ガスを前記処理容器内から除去する第2の工程とを繰り返してなる第1の膜成長工程と、金属ハロゲン化物からなる第3の原料ガスを前記処理容器内に供給した後、前記第3の原料ガスを前記被処理基板から除去する第3の工程と、水素または水素化合物を含む第4の原料ガスを前記処理容器内に供給した後、前記第4の原料ガスを前記処理容器内から除去する第4の工程とを繰り返してなる第2の膜成長工程からなる成膜方法を用いた。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置の製造方法は、第1の高さのフィン型半導体領域うえに、第1の高さより高い第2の高さの絶縁ゲート電極構造を形成し、サイドウォール絶縁膜をフィン型半導体領域の側面からは完全に異方性エッチングで除去し、フィン型半導体領域近傍のゲート電極両側面ではフィン型半導体領域の上面、側面をサイドウォール絶縁膜が囲むように、ゲート電極両側面上下部を残して上部上からエッチング除去し、フィン型半導体領域の少なくとも露出している両側面に上端から下端までシリサイド層を形成する。層間絶縁膜形成後、フィン型半導体領域の両側面のシリサイド層を露出するコンタクトホールを形成し、導電性プラグを埋め込む。

(もっと読む)

化合物半導体装置

【課題】 ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】 化合物半導体層100上にショットキー接合してなるゲート電極101において、化合物半導体層100とショットキー障壁を形成するNi層41と、低抵抗金属層42との間に、低抵抗金属層42の金属の化合物半導体層100への拡散を抑止するTixW1-xN(0<x<1)からなる拡散防止層を設けるようにして、ゲート電極のリーク電流の増大を抑制する。

(もっと読む)

961 - 980 / 1,113

[ Back to top ]