Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

1,021 - 1,040 / 1,113

集積回路内での金属層の選択的形成

【課題】集積回路(IC)メタライゼーションにおいて信頼性が高いインターフェースを形成するための、生産的かつ制御可能な方法を与える。

【解決手段】埋め込み銅配線の表面が露出したビア底またはCMP直後の銅配線の上面での銅相互接続及び/またはコンタクトの信頼性を強化するための方法が与えられる。当該方法は、露出した銅表面を貴金属から成る気相化合物と接触させる工程と、銅置換反応または貴金属の選択的蒸着(例えば、ALDまたはCVD)により、露出した銅表面上に貴金属の層を選択的に形成する工程から成る。

(もっと読む)

有機金属化学蒸着用有機ニッケル化合物及び該化合物を用いたニッケル含有膜の製造方法

【課題】高い平坦性で膜を形成することができる。不純物含有量の少ない膜を形成することができる。

【解決手段】本発明の有機ニッケル化合物は、Ni(R-Cp)2で表される有機ニッケル化合物である。但し、式中のCpはシクロペンタジエニル基を示し、Rは水素又は炭素数が1〜4の直鎖若しくは分岐状アルキル基をそれぞれ示す。また、本発明のニッケル含有膜の製造方法は、上記有機ニッケル化合物を用いてMOCVD法によりニッケル含有膜を作製することを特徴とする。

(もっと読む)

窒化物、炭化物、および酸化物の保護コーティング形成のためのプロセッシング

【課題】コーティングの形成前にバルク基材材料からイオウを除去するか、または基材材料の調製の間に、少量の割合の強力な硫化物形成剤(例えば、イットリウムまたはハフニウム)を基材材料に添加して、基材表面に偏析するのに有用な遊離のイオウが存在しないようにすることを提供すること。

【解決手段】基材材料の表面上に、特異的反応性元素のバリア層を形成する方法であって、該基材材料が、該基材材料の表面に偏析し得る1ppm未満の遊離のイオウであって、そして特異的反応性元素、ならびにその窒化物、炭化物、または酸化物が、上記特異的反応性元素の対応する窒化物、炭化物、または酸化物よりも不安定である元素をさらに含み、上記方法が、窒化物、炭化物、または酸化物のバリア層を形成する工程を包含する方法。

(もっと読む)

有機ニッケル化合物及び該化合物を用いたニッケル含有膜の製造方法

【課題】有機金属化学蒸着法により高い平坦性で膜を形成することができる有機ニッケル化合物の提供。

【解決手段】本発明の有機ニッケル化合物は、Ni(R1R2N)2で表される有機ニッケル化合物である。但し、式中のR1及びR2は水素又は炭素数が1〜4の直鎖若しくは分岐状アルキル基をそれぞれ示し、R1とR2は互いに同一又は異なっていてもよい。また、本発明のニッケル含有膜の製造方法は、上記有機ニッケル化合物を用いてMOCVD法によりニッケル含有膜を作製することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィー工程を削減するとともに、活性領域の縮小により半導体装置の集積度を高める。

【解決手段】 フィールド形成用のシリコン窒化膜102を用いて素子分離領域105を形成した後、このシリコン窒化膜102をパターニングすることによりゲートトレンチ114bを形成する。次に、ゲートトレンチ114b内にゲート電極材料111〜113を埋め込み、これをエッチバックした後、シリコン窒化膜102を除去する。そして、これにより形成されたコンタクトホール内にコンタクトプラグを埋め込む。これにより、拡散層コンタクトパターンを用いることなく、コンタクトプラグを形成できるとともに、コンタクトプラグの周縁が素子分離領域と活性領域の境界と実質的に一致することから、活性領域を縮小することが可能となる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現する半導体記憶装置を提供する。

【解決手段】 半導体基板1上に形成されたメモリセルと、第1電荷保持部と、第2電荷保持部と、第1アクセストランジスタと、第1リークトランジスタ522Aと、第2アクセストランジスタと、第2リークトランジスタと、層間絶縁膜16と、層間絶縁膜16上に形成され、第1電荷保持部に接続されたメモリセル内の第1MISFET56A(Metal-Insulator-Semiconductor Field Effect Transistor)と、層間絶縁膜16上に形成され、第2電荷保持部と接続されたメモリセル内の第2MISFET(Metal-Insulator-Semiconductor Field Effect Transistor)とを備える。

(もっと読む)

集積回路の領域に、特にトランジスタの電極にコンタクト・パッドを生成するための方法

【課題】コンパクト・パッドの生成について改善された方法を提供する。

【解決手段】領域(51)は、該領域の表面の少なくとも一部に伸長する区域(510)であって、該領域に対して選択的に除去することが可能な材料から形成される区域を作成するよう、局所的に変更される。該領域は、絶縁材料(7)で覆われており、該区域の表面に出現するオリフィス(90)が、該絶縁材料内に形成される。該選択的に除去が可能である材料は、該区域に代わってキャビティ(520)を形成するように、該区域から、オリフィスを介して除去される。キャビティおよびオリフィスは、少なくとも1つの導電性材料(91)で充填される。

(もっと読む)

半導体装置

【課題】 高性能な半導体装置を提供する。

【解決手段】 シリコン基板1に、素子分離膜3に囲まれた活性領域2aが設けられる。活性領域2aの上には、ベース層として機能するSiGe合金層4およびエミッタ層として機能するn型拡散層5を設け、SiGe合金層4と素子分離膜3との間の活性領域2aの表面に溝60が設けられる。またSiGe合金層4およびn型拡散層5は、シリコン酸化膜からなる側壁膜6で囲われる。この側壁膜6は、活性領域2aの表面に設けられた溝60を埋め込むとともに、溝60と素子分離膜3との境界50にまたがって設けられる。n型拡散層5の上の多結晶シリコン膜7およびシリサイド膜8は、n型拡散層5、側壁膜6、及び素子分離膜3にまたがって設けられる。そして層間絶縁膜10を設けて平坦化した後、素子分離膜3の上のシリサイド膜8に接続するように、エミッタ層(n型拡散層5)につながる引き出し電極21が設けられる。

(もっと読む)

半導体装置の製造方法およびそれによって得られる半導体装置

【課題】 ウェハ面内において無電解メッキ法による所定のキャップ層を均一に形成するための半導体装置の製造方法と、その製造方法によって得られる半導体装置を提供する。

【解決手段】 リセス5bの内部を含む層間絶縁膜5の全面に導電性薄膜9が形成される。次に、無電解メッキ法により、導電性薄膜9上にCoWP膜の無電解メッキ層10が形成される。次に、CMP処理を施すことにより、リセス5b内に位置する無電解メッキ層10および導電性薄膜9の部分を残して、層間絶縁膜5の上面上に位置する無電解メッキ層10および導電性薄膜9の部分が除去されて、半導体装置において、銅メッキ層および無電解メッキ層等を含む銅配線が形成される。また、リセス5b内に位置する無電解メッキ層および導電性薄膜は銅メッキ膜を覆うキャップ層とされる。

(もっと読む)

半導体装置及びその製造方法

【課題】

ポリメタル構造のゲート電極を有するMOSFET、特に、DRAMのメモリセルトランジスタの接合リークをよりいっそう低減する。

【解決手段】

半導体基板上に、ゲート絶縁膜、ポリシリコン膜、タングステンなどの高融点金属膜、ゲートキャップ絶縁膜を順次積層し、エッチングによりゲートキャップ絶縁膜および高融点金属膜を選択的に除去する。その後、ゲートキャップ絶縁膜、高融点金属膜及びポリシリコン膜の側面に、シリコン窒化膜及びシリコン酸化膜からなる2重の保護膜を形成し、これをマスクとして用いてポリシリコン膜をエッチングする。その後、ライト酸化処理を行って、ポリシリコン膜の側面にシリコン酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極上に形成するコンタクトホールの底面の金属膜の表面が酸化されるのを抑制する。

【解決手段】 基板上コンタクトホール19a、19bと、底面に金属膜7aを露出させたゲート電極上コンタクトホール19cとを形成した後、基板上コンタクトホール19a、19bの底面に露出したシリコン基板1にそれぞれ不純物を注入してN型イオン注入層21、P型イオン注入層23を形成する。その後、基板上コンタクトホール19a、19bおよびゲート電極上コンタクトホール19cが埋め込まれない膜厚で、これらのコンタクトホールの内面に金属酸化防止膜24を形成する。そして、熱処理により不純物を活性化させた後に、それぞれのコンタクトホールの底面の金属酸化防止膜24を除去する。

このように形成することにより、上記熱処理において金属膜7aの表面が酸化されるのを抑制することができる。

(もっと読む)

半導体装置およびその製造方法

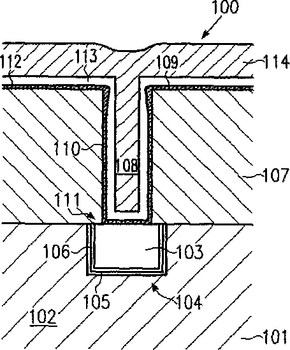

【課題】基板表面側でトランジスタとストレージノード電極との接続を低抵抗で実現する。

【解決手段】トレンチ3を形成し、トレンチの内壁にカラー酸化膜4を形成し、不純物が導入されている半導体材料を、前記カラー酸化膜4が形成されているトレンチ内に埋め込んでストレージノード電極5を形成する。ストレージノード電極5に隣接した基板領域に、ソース・ドレイン領域11を有するトランジスタTRを形成する。ソース・ドレイン領域11とストレージノード電極5とがカラー酸化膜4を挟んで近接する箇所を、半導体材料のエッチングレートに比べ絶縁材料のエッチングレートが大きい条件でエッチングする。このエッチングによりカラー酸化膜4が基板深部側に後退した部分4Aが形成され、そこに非晶質シリコンなどの半導体材料を埋め込んで半導体接続層15Aを形成する。半導体接続層15Aおよび周囲の半導体部に半導体と金属の合金層19を形成し、当該合金層19によりソース・ドレイン領域11とストレージノード電極5とを電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高いON電流を有し、しかも消費電力の低いCMOS回路を実現するためのMISトランジスタ構造を提供する。

【解決手段】 nチャネル型MISトランジスタ(Qn)とpチャネル型MISトランジスタ(Qp)のそれぞれのゲート絶縁膜5は、酸化ハフニウム膜で構成されている。また、ゲート電極18は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比がほぼ1(PtSix:x=1)のPtシリサイド膜で構成されている。pチャネル型MISトランジスタ(Qp)のゲート電極17は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比が1未満(PtSix:x<1)のPtシリサイド膜で構成され、ゲート電極17のフェルミレベルピニングが抑制されている。

(もっと読む)

触媒を用いた無電解めっきによりパターン化された絶縁体上に金属層を形成する方法

金属層は、触媒により活性化された下地材料の表面領域上に、めっきプロセスによって形成されうる。この触媒はCVD、PVDまたはALDによって堆積されるかまたは下地材料を堆積する際に少なくとも部分的に取り込まれる。このようにして、メタライゼーション構造の高アスペクト比のビアに優れた金属シード層を形成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 微細且つ電気的特性に優れた半導体装置の製造方法を提供する。

【解決手段】 層間絶縁膜10をマスクとしたストッパー膜9のドライエッチングによって、拡散層領域8に至るコンタクトホール11を形成する。この際、ストッパー膜9のオーバーエッチングによって、コンタクトホール11の底面をシリコン基板1の表面よりリセスする。続いて、シリコン基板1の表面を洗浄した後、コンタクトホール11の内面を覆うようにして層間絶縁膜10の上にポリシリコン膜12を形成する。ポリシリコン膜12の膜厚は、コンタクトホール11の底面がシリコン基板1の表面に対してリセスした深さより大きく、シリサイド化で消費されるシリコンの厚さより小さくなるようにする。これにより、オーバーエッチングおよびシリサイド化によってシリコン基板1から消失するシリコンの量を低減させることができる。

(もっと読む)

液晶表示装置の製造方法

【課題】液晶表示装置の低抵抗配線を作製するにあたって、ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止し、かつスパッタ時のダスト発生を抑制する。

【解決手段】Al合金配線を有する液晶表示装置を製造するにあたって、Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる第1の元素を0.001〜30原子%の範囲で含み、残部が実質的にAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、O、NおよびHから選ばれる第2の元素を含むガスを使用し、得られたインゴットまたは焼結体を加工してスパッタターゲットを作製する。このスパッタターゲットをスパッタして形成したAl合金膜にエッチング処理を施してAl合金配線を形成する。

(もっと読む)

ゲート構造及び該構造を作る方法

【課題】完全なシリサイドゲートを伴うMOSトランジスタの新規構造を得ることである。

【解決手段】本発明は、MOSトランジスタに関し、そのゲートは絶縁層(31)、金属シリサイド層(50)、導電性封入材料層(53)、及びポリシリコン層(55)を連続的に含む。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】 金属ゲート電極、金属ソース領域および金属ドレイン領域を備え、電流駆動能力を高めた電界効果型トランジスタおよびその製造方法を提供することである。

【解決手段】 ソース領域26、ドレイン領域28、およびゲート電極31n、31pをシリサイド等の金属材料により構成し、nチャネルMISFET24nでは、ゲート電極31nの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg<Wsであり、pチャネルMISFET24nでは、ゲート電極31pの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg>Wsであるように金属材料を選択する。

【効果】 ソース領域26とチャネル領域29との界面のバリア高さが低下し、チャネル領域29のキャリア濃度が向上し電流駆動能力が向上する。

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

銅配線の形成方法

【課題】CVD法により、埋め込み性、下地層との密着性に優れた銅配線形成方法の提供。

【解決手段】ホールや溝が形成された基板表面上に、金属原料としてテトラキスジエチルアミノバナジウム、テトラキスジメチルアミノバナジウム、テトラキスエチルメチルアミノバナジウム、テトラキスジエチルアミノチタン、テトラキスジメチルアミノチタン、テトラキスエチルメチルアミノチタンを、還元性ガスとしてターシャリーブチルヒドラジン、NH3、H2、SiH4、Si2H6を用いて、CVD法によりバナジウムまたはチタン含有膜からなる下地層を形成し、この上に、CVD法により銅含有膜を形成し、ホールや溝を埋め込み、配線を形成する。

(もっと読む)

1,021 - 1,040 / 1,113

[ Back to top ]