Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

1,001 - 1,020 / 1,113

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

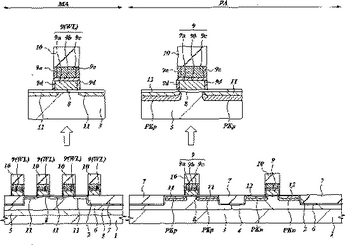

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】アルミ配線層間をタングステンプラグによって電気的に接続する構成において、スルーホール内面全面にバリアメタル層が形成され、タングステンプラグとアルミ配線層との電気的接続の信頼性が高く、接触抵抗が低い半導体装置を提供することを目的とする。

【解決手段】スルーホール9の内面にチタン膜10および窒化チタン膜11の2層構造で構成されるバリアメタル層を形成する。なお、チタン膜10および窒化チタン膜11は、層間絶縁膜7の主面上にも形成される。このバリアメタル層の形成に際しては、チタンターゲットを用いた高指向性スパッタリングが可能で、かつ、高周波電圧を半導体基板にバイアスする基板バイアス機構を備え、チタンターゲットからのスパッタ粒子を半導体基板に引き付けることで、窒化チタン膜11をアモルファス金属膜とすることが可能となる。

(もっと読む)

めっき装置及びめっき方法

【課題】 比較的簡単な構成で、例えアスペクト比が高く、深さが深いビアホール等にあっても、内部にボイドを発生させることなく、金属膜を確実に埋込むことができるようにする。

【解決手段】 めっき液188を保持するめっき槽186と、基板Wを保持して該基板に通電し、基板の被めっき面をめっき槽内のめっき液に接触させるホルダ160と、めっき槽内のめっき液に浸漬させて配置されるアノード214と、アノードとホルダで保持した基板との間に配置され、めっき槽内のめっき液を攪拌するめっき液攪拌部220,224と、基板とアノードとの間に電圧を周期的に印加するめっき電源230を有し、基板とアノードとの間に電圧が印加されていない時にめっき液攪拌部によるめっき液の攪拌を行い、基板とアノードとの間に電圧が印加されている時にめっき液攪拌部によるめっき液の攪拌を停止する。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ボイド等を生ずることなく被処理体の凹部を埋め込むことができ、しかもメッキ処理の負担を軽くして、表面の研磨処理の負担も軽減することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内でプラズマにより金属ターゲット56をイオン化させて金属イオンを発生させ、金属イオンを処理容器内の載置台20上に載置した被処理体Sにバイアス電力により引き込んで凹部2が形成されている被処理体に金属膜74を堆積させて凹部を埋め込むようにした成膜方法において、バイアス電力を、被処理体の金属ターゲットに対する対向面に関して、金属イオンに対する引き込みによる成膜レートとプラズマガスによるスパッタエッチングのエッチングレートとが略均衡するような状態になるように設定して成膜処理を行う。これにより、ボイド等を生ずることなく被処理体の凹部を埋め込むことができる。

(もっと読む)

半導体装置

【課題】 キャパシタの特性や信頼性の低下を防止することが可能な半導体装置を提供する。

【解決手段】 下部電極と上部電極と誘電体膜とを含むキャパシタを備えた半導体装置であって、下部電極は、イリジウムを含む第1の導電膜117と、誘電体膜122と第1の導電膜との間に設けられ且つ貴金属膜で形成された第2の導電膜119と、誘電体膜と第2の導電膜との間に設けられ且つペロブスカイト構造を有する導電性金属酸化物膜で形成された第3の導電膜121と、第1の導電膜と第2との導電膜の間に設けられ且つ金属膜及び金属酸化物膜の少なくとも一方を含み且つ第1の導電膜に含まれるイリジウムの拡散を防止する拡散防止膜118aと、を備え、誘電体膜は、ペロブスカイト構造を有する絶縁性金属酸化物膜を含み、該絶縁性金属酸化物膜は、A(ZrxTi1-x )O3 (ただし、Aは少なくとも1以上のAサイト元素、0<x<0.35)で表される。

(もっと読む)

半導体装置の製造方法

【課題】 ニッケルモノシリサイド層の熱安定性を向上させ、例えば65nm〜45nmノードにおける実用レベルの半導体装置の製造を可能にする。

【解決手段】 シリコン基板11の表面部に不純物拡散層12を形成し、その表面の自然酸化膜を除去した後、Ni−Ir合金層13を堆積させて、例えば300℃〜500℃の温度で窒素ガス雰囲気中の急速熱アニール(RTA)を施し、イリジウム含有のニッケルモノシリサイド層15を形成する。ここで、Ni−Ir合金層13のイリジウムの含有量は、0.1at.%〜5at.%の範囲にすると好適である。このシリサイド層の形成方法により、半導体素子の例えばMISFETのソース/ドレイン拡散層あるいはゲート電極上にイリジウム含有のニッケルモノシリサイド層を形成し上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】 表面に凹凸パターンを有する基板上に均一な膜を所定の膜厚で成膜する方法を提供することを目的とする。

【解決手段】 表面に凹凸パターンを有する基板上に第1の材料からなる第1の膜厚の薄膜を堆積する工程を備えた半導体装置の製造方法であって、表面に凹凸パターンを有しないモニタ基板上に前記第1の材料からなる薄膜を形成してその薄膜の膜厚を測定することにより前記第1の膜厚の薄膜を堆積する第1の条件を算出し、前記凹凸パターンを有する基板上に、前記第1の条件よりも厚い薄膜が堆積される第2の条件で前記第1の材料を堆積することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

成膜方法

【課題】 Cu拡散防止膜との密着力が良好であり、微細バターンに成膜が可能なCu膜の成膜方法を提供する。

【解決手段】 被処理基板上に形成されたCu拡散防止膜上に、Cu膜を形成する成膜方法であって、前記Cu拡散防止膜上に、当該Cu拡散防止膜と前記Cu膜との密着膜を形成する第1の工程と、前記被処理基板上に、超臨界状態の媒体にプリカーサが溶解した処理媒体を供給し、前記密着膜上に前記Cu膜を形成する第2の工程と、を有することを特徴とする成膜方法

(もっと読む)

半導体素子の製造方法

【課題】 SOI基板上にチタンシリサイド膜を形成する場合に発生するMOSトランジスタのサイドウォール上での短絡不良を防止し、かつN型シリコン領域でも比抵抗の小さいチタンシリサイド膜を形成する技術を提供する。

【解決手段】 SOI基板100上にPMOS領域403とNMOS領域404から成るCMOS領域を形成した後、SOI基板100のシリコン膜103をその膜厚の10%以上、90%以下の深さまでアモルファス化する工程と、チタン膜802を、10nmを下限として、シリコン膜103の膜厚以下で成膜する工程と、チタン膜802上に酸素及び窒素の浸入を防ぐためのバリア膜803を形成する工程と、550℃以上600℃以下の温度で、30秒以上180秒以下の時間熱処理する工程と、バリア膜803と未反応のチタン膜802とを選択的に除去する、アンモニア水と過酸化水素水の混合液を用いたウェットエッチング工程を行なう。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】被処理体の凹部の開口にオーバハング部分を生ずることなく、この凹部の側壁に均一に金属膜を形成することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内でプラズマにより金属ターゲット56をイオン化させて金属イオンを発生させ、金属イオンを処理容器内の載置台20上に載置した被処理体にバイアス電力により引き込んで凹部2が形成されている被処理体に金属膜6、70を堆積させるようにした成膜方法において、載置台に、金属イオンに対する引き込みによる成膜とプラズマガスによるスパッタエッチングとが同時に生ずるような大きさのバイアス電力を加えて、凹部の側壁に金属膜を堆積させる成膜工程を行う。これにより、凹部の開口にオーバハング部分を生ずることなく、この凹部の側壁に均一に金属膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】空孔を有する低誘電率絶縁膜上にバリアメタルを成膜する前におけるビア底の高抵抗層の除去手段として、プラズマを用いない新規な半導体装置の製造方法及び製造装置を提供する。

【解決手段】層間膜に比誘電率の値が3未満の低誘電率膜102を用いた金属膜配線103を含む半導体装置の製造方法において、前記金属膜配線と前記層間膜の間に形成されるバリアメタル105を成膜する前に、100℃〜400℃に温調されたNH3ガスなどの還元性を有するガスもしくは還元性を有するガスを含む混合ガスで熱還元処理を行う。

(もっと読む)

半導体装置の製造方法

【目的】 p−lowk膜上にバリアメタルを連続に形成することを目的とする。

【構成】 本発明の半導体装置の製造方法は、基体上に、表面にメチル(CH3)基が結合している絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜表面に、イミド系の高融点金属化合物を原料として、バリアメタル膜を形成するバリアメタル膜形成工程(114)と、を備えたことを特徴とする。そして、前記バリアメタル膜形成工程において、原子層気相成長法によりバリアメタル膜を形成する。

(もっと読む)

半導体装置の製造方法

【目的】 選択的に拡散防止膜を形成する場合でも、配線同士間でショートが生じてしまう原因となる導電性材料の研磨残りを生じさせないようにすることを目的とする。

【構成】 基体上の開口部に形成された導電性材料膜上に前記導電性材料膜に用いる導電性材料の拡散を防止する拡散防止膜を選択的に形成する拡散防止膜形成工程(S120〜S122)と、前記拡散防止膜が形成された後、前記基体上に絶縁膜を形成する絶縁膜形成工程(S124〜S128)と、前記絶縁膜形成工程の後、前記絶縁膜表面を研磨する平坦化工程(S130)と、を備えたことを特徴とする。

(もっと読む)

金属カルボニル前駆体からの金属層の成膜速度を上げる方法

金属カルボニル前駆体(52、152)の気相原料を一酸化炭素ガスと混合することにより、金属カルボニル前駆体(52、152)からの金属層の堆積速度を増大する方法(300)が開示される。この方法(300)は、堆積システム(1、100)のプロセスチャンバ(10、110)に基板(25、125)を提供する工程と、金属カルボニル前駆体の気相原料を含むプロセスガスを生成する工程と、熱化学気相堆積プロセスによって基板(25、125、400、402)に金属層(440、460)を堆積するために基板(25、125、400、402)をプロセスガスに晒す工程とを含む。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体製造装置

シリコンウエハ101上のゲート酸化膜102上に、ポリシリコンを成膜して、ポリシリコン電極層103(第一電極層)を形成する。このポリシリコン電極層103上に、タングステン層105(第二電極層)を形成する。なお、タングステン層105を形成する前に、予め導電性のバリア層104をポリシリコン電極層103の上に形成しておく。その後、窒化シリコン層106をエッチングマスクとして、エッチング処理を行う。そして、剥き出しとなったポリシリコン層103の露出面に、プラズマ酸化処理により、酸化絶縁膜107を形成する。これにより、タングステン層105を酸化させずに、ポリシリコン電極層103に対して選択的な酸化処理を行うことができる。  (もっと読む)

(もっと読む)

絶縁膜の成膜方法及びその絶縁膜を備えた半導体装置

【課題】絶縁膜の成膜方法において、シリコン原子を堆積させる第1ステップと、シリコン原子を窒化する第2ステップとを有するALD法を用い、フラットバンド電圧及び界面準位の小さい好適な特性を有する薄い絶縁膜の成膜方法を提供する。

【解決手段】第1及び第2ステップでの成膜温度と圧力を同一とし、成膜温度を510℃以下の低温とし、圧力を70Pa以下、RFパワーを0.1KW以上とすることでフラットバンド電圧及び界面準位の小さい好適な特性の絶縁膜が得られる。これらの好適な絶縁膜を備えた半導体装置が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】

ソース領域をエッチングするときに、ゲート電極が過剰にエッチングされてしまうことを防止する。

【解決手段】

本発明に関わる半導体装置は、半導体基板上に形成されたベース領域と、前記ベース領域上に形成されたソース領域と、前記半導体基板上に形成されたトレンチ内部に埋め込まれたゲート電極と、前記半導体基板上全面に形成された層間絶縁膜と、前記層間絶縁膜に形成され、前記ゲート電極を露出する第1のコンタクトホールと、前記層間絶縁膜および前記ソース領域に形成され、前記ベース領域を露出する第2のコンタクトホールと、前記第1のコンタクトホールが形成されるトレンチ上に形成された第2の導電膜とを有する。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

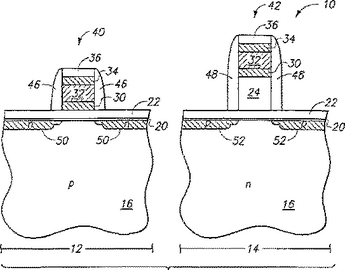

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

1,001 - 1,020 / 1,113

[ Back to top ]