Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

1,041 - 1,060 / 1,113

プラズマ加工ステップセットの調整方法及び装置

プラズマ加工システムで利用するプラズマ加工ステップの調整方法が開示されている。この方法はプラズマ加工システムのプラズマ反応器内で中性分子とイオンとを含んだ第1プラズマをストライク処理するステップを含んでいる。この方法はさらに、基板上の複数層を第1エッチングステップでエッチングするステップと、基板周囲に可動均一リングを設置するステップとを含んでいる。均一性リングの底面は基板の上面とほぼ同じ高さである。方法はさらに、プラズマ加工システムのプラズマ反応器内で本質的に中性分子で成る第2プラズマをストライク処理するステップを含んでいる。方法はさらに、基板上の複数層を第2エッチングステップでエッチングするステップを含んでいる。第1ステップのエッチングと第2ステップのエッチングとは実質的に均等である。  (もっと読む)

(もっと読む)

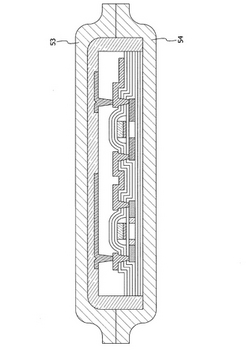

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

銅配線の形成方法

【課題】CVD法により、埋め込み性、下地層との密着性に優れた銅配線形成方法の提供。

【解決手段】ホールや溝が形成された基板表面上に、金属原料としてテトラキスジエチルアミノバナジウム、テトラキスジメチルアミノバナジウム、テトラキスエチルメチルアミノバナジウム、テトラキスジエチルアミノチタン、テトラキスジメチルアミノチタン、テトラキスエチルメチルアミノチタンを、還元性ガスとしてターシャリーブチルヒドラジン、NH3、H2、SiH4、Si2H6を用いて、CVD法によりバナジウムまたはチタン含有膜からなる下地層を形成し、この上に、CVD法により銅含有膜を形成し、ホールや溝を埋め込み、配線を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】シリコン窒化膜を堆積してもシート抵抗が上昇しない配線構造を提供する。

【解決手段】半導体基板上に第一の高融点金属膜5を形成する工程と、前記第一の高融点金属膜上に高融点金属窒化物の反応物7を持つ第二の高融点金属膜6Aを形成する工程と、前記第二の高融点金属膜上にシリコン窒化膜8を形成する工程とからなる。これにより、シリコン窒化膜の膜質を変化させることなく、また成膜時のパーティクルの発生を従来方法と同等としたまま、シリコン窒化膜下の高融点金属のシート抵抗の上昇を最小限に抑えることができる。

(もっと読む)

半導体素子とその製造方法、及び電子部品ユニット

【課題】 高品質の半導体素子を提供する。

【解決手段】 基板と、基板上方に形成された複合接合層と、複合接合層上方に形成された第1の電極と、第1の電極上を含む領域に形成された半導体層と、半導体層上の一部の領域に形成された第2の電極とを有し、複合接合層は、基板、及び第1の接合層を含む支持基板と、半導体層、第1の電極、及び第2の接合層を含む半導体積層構造とを接合するときに形成され、第1または第2の接合層は共晶成分を含み、支持基板及び半導体積層構造の少なくとも一方は、拡散材料を含む拡散材料層を含み、複合接合層は、第1または第2の接合層の一方に含まれる共晶成分が他方の接合層と混合して第1の混合体を形成し、更に第1の混合体と拡散材料層に含まれる拡散材料とが混合し、第1の混合体の溶融温度より高い溶融温度を有する第2の混合体を形成することにより形成される半導体素子を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

表面活性化剤を用いた銅の原子層蒸着

本発明は、原子層蒸着法において、基材上または多孔性固体の中あるいは上に銅膜を形成するための新規な原子層蒸着法に関する。 (もっと読む)

半導体デバイスの製造方法およびこのような方法で得られる半導体デバイス

本発明は、半導体ボディ(1)と基板(2)とを有し、少なくとも1つの半導体素子(3)を備える半導体デバイス(10)の製造に関し、この半導体デバイスは、少なくとも1つの接続領域(4)と、接続領域に接続された、上に位置する帯状の接続導体(5)と、を備え、この接続領域および接続導体は、両方とも誘電体に凹設され、第1材料の誘電体領域(6)が、半導体ボディ(1)の、接続領域(4)が形成される位置に設けられ、その後、誘電体領域(6)は、第1材料とは異なる第2材料の誘電体層(7)で被覆され、この誘電体層には、帯状の接続導体(5)が形成される位置に帯状の凹部(7A)が設けられ、この凹部は、誘電体領域(6)に重なり、かつ前記誘電体領域まで延び、凹部(7A)の形成と誘電体領域(6)の除去の後、接続領域(4)が、誘電体領域(6)の除去により作られた空間(6A)に導電性材料を堆積することにより形成され、接続導体(5)が、凹部(7A)に導電性材料を堆積することにより形成される。本発明によると、第1材料には、有機材料が用いられ、第2材料には、この有機材料より高い分解温度を有する材料が用いられ、誘電体領域(6)は、有機材料の分解温度より高く、第2材料の分解温度よりは低い温度で加熱することにより除去される。本発明に係る方法は、非常にシンプルであり、第2材料を任意に選択することにより、得られるデバイス(10)に高い平面性をもたらすことができる。誘電体領域(4)には、好ましくはフォトレジストが用いられ、誘電体層(7)には、好ましくはSILKまたはSOG材料などの液体材料が用いられ、これは、加熱により固体状に変換することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 従来技術による金属ゲート電極形成ではシリコン基板が大口径化した場合、ウェハ面内、及び疎密間での寸法及び形状のばらつきが大きくなるという課題があった。

【解決手段】 本発明は、タングステンゲートエッチングにおいて、寸法のウェハ面内均一性に優れた電極形成可能とした半導体装置の製法であって、具体的には、シリコン基板101にゲート絶縁膜としてシリコン酸化膜102、高誘電体膜(High−k膜)103、ゲート電極材料としてタングステン膜104、マスク膜としてシリコン窒化膜105を順に成膜する。反射防止膜106を塗布し公知のリソグラフィ技術によりパターンを形成し、この基板を反射防止膜106、シリコン窒化膜105を一般的な条件でエッチングした後、タングステン膜をシリコン基板の中央と外周のプラズマ密度の比を3〜4:1の条件で残膜が3〜5nmになるまでエッチングを行い、最後に残りのタングステン膜をプラズマ密度の比が中央:外周=1:1の条件でエッチングを行うこと方法である。

(もっと読む)

半導体装置及びその作製方法、並びにテレビジョン

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型のTFTを有する半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜を成膜し、該非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜上にドナー型元素又は希ガス元素を有する層を形成し加熱して触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型のTFTを形成して半導体装置を作製する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能を向上させる。

【解決手段】 LDMOSFETのゲート電極30およびn+型ソース領域53上にサリサイド工程により金属シリサイド膜64を形成し、n-型オフセットドレイン領域33、n型オフセットドレイン領域51およびn+型ドレイン領域52上にはこの金属シリサイド膜を形成しない。ゲート電極30のドレイン側の側壁上には、絶縁膜を介して、シリコン膜からなるサイドウォールスペーサが形成され、このサイドウォールスペーサによりフィールドプレート電極44が形成される。フィールドプレート電極44はゲート電極30上に延在しておらず、サリサイド工程ではゲート電極30の上面の全面に金属シリサイド膜64が形成される。

(もっと読む)

容量素子、半導体装置及び半導体装置の製造方法

【課題】 容量素子配置のためのスペースを確保しつつ、半導体装置の微細化を可能とする。

【解決手段】 基板上に形成された下部電極と、下部電極上に形成された誘電体膜と誘電体膜上に形成された上部電極とを備える容量素子において、下部電極は、基板上に形成されるトランジスタのゲート電極と同時に形成され、電極を共有する。また、上部電極は、基板上に形成されるコンタクトプラグと同時に形成され、コンタクトプラグを構成する材料と同一の材料で構成される。

(もっと読む)

半導体装置

【課題】 はんだ接続用パッドを有する半導体装置において、製造工程中の熱負荷などによって発生する恐れのある、パッド部の膜剥がれを防止する。

【解決手段】 シリコン、シリコン酸化膜上に形成されるTi膜またはTi化合物膜と、はんだが接続されるNi膜(またはCu膜)との間に、両者との密着性が良好なCr膜を挿入したパッド構造とする。さらに、Ti膜またはTi化合物膜とシリコン酸化膜との界面に生じる剥離を防止するため、Cr膜がTi膜またはTi化合物膜よりも大きな面積で形成された構造とする。

(もっと読む)

半導体装置の製造方法

【課題】タングステン層の抵抗値の上昇を抑えることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、半導体基板(1)上に層間絶縁膜(2)を形成するステップと、前記層間絶縁膜(2)の内部に延びるコンタクトホールを形成するステップと、前記コンタクトホールの底面部及び側壁部にバリアメタル層(4)を形成するステップと、前記バリアメタル層(4)が形成された前記コンタクトホールに、フッ素を含む材料からタングステン層(5)を形成するステップと、ポストパージにより前記タングステン層(5)から前記フッ素を除去するステップとを具備している。

(もっと読む)

半導体装置の製造方法

【目的】 点欠陥の集合によるボイドがCu配線内に形成しないようにすることを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S110)と、前記絶縁膜に開口部を形成する開口部形成工程(S112)と、前記絶縁膜表面と前記開口部とにシード膜を形成するシード膜形成工程(S116)と、前記シード膜を電極として第1の電流密度となる電流を流し、前記開口部に導電性材料をめっき法により堆積させる第1のめっき工程(S118)と、前記第1のめっき工程後、前記第1の電流密度より小さい第2の電流密度となる電流を流し、前記絶縁膜表面上に前記導電性材料をめっき法により堆積させる第2のめっき工程(S120)と、前記第2のめっき工程後、前記導電性材料が堆積した基体をアニール処理するアニール工程(S124)と、を備えたことを特徴とする。

(もっと読む)

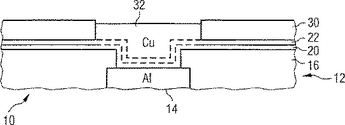

金属、特に銅を電着する方法、この方法の使用、および集積回路構造

とりわけ、絶縁層(16)内において相互接続(14)へのコンタクトホール(18)が生成される方法が示される。バリア層(20)が次いで提供される。その後、フォトレジスト層(30)が提供され、照射され、かつ、現像される。次いで、ガルバニック法を用いて、銅コンタクト(32)がコンタクトホール(18)において生成される。バリア層(20)またはさらなる境界電極層(22)のどちらか一方が、ガルバニック処理において境界電極としての役目をする。重大な金属汚染は、製造中、この方法によって抑制される。  (もっと読む)

(もっと読む)

多重積層膜構造の金属窒化膜の蒸着方法

【課題】素子回路線幅の超微細化、パターン縦横比の増加、および蒸着温度の低下にもかかわらず、膜特性、段差塗布性、大気/湿気露出に対する膜質変化に対する安定性の全てを満足させる多重積層膜構造の金属窒化膜の蒸着方法を提供する。

【解決手段】基板上に第1蒸着速度で第1下部金属窒化膜を形成し、前記第1下部金属窒化膜上に第2蒸着速度で第2下部金属窒化膜を形成し、前記2段階によって形成された下部TiN膜上に、窒素(N)含有量の多い上部金属窒化膜を第3蒸着速度で形成することからなり、前記n番目膜の蒸着速度は、第2蒸着速度≧第1蒸着速度≧第3蒸着速度である。本発明によれば、基板上にTiN積層膜を形成することで、大気/湿気露出に対する安定性を向上させることができ、クラスタシステムの同一反応チャンバーまたは相違した反応チャンバーで容易に基板上にTiN積層膜を形成することができる。

(もっと読む)

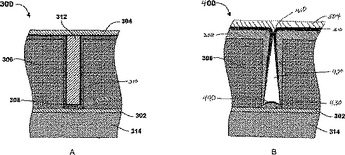

集積回路相互接続構造のGCIB処理

集積回路内の金属(304)の相互接続の製造工程および品質を改善するために、ガスクラスタ・イオンビーム(GCIB)(128)によって集積回路相互接続構造の溝やビア内の材料を取り除いたり再配分したりする方法が開示されている。この工程では、構造の入口の領域での不要な「ネックイン」を広げ、構造の頚部または底部等のより厚い領域から側壁に、バリア金属(308)を再堆積させたり、スパッタリングによって構造の底部の余分で不要な材料の一部を取り除く。GCIB処理は、バリア金属堆積後で銅シード層(310)/銅(312)電気メッキ前に適用することも、銅シード層(310)の形成後で電気メッキ前に適用することもできる。この方法は、既知の相互接続堆積技術の有用性を、次世代以降の集積回路まで拡張できる。  (もっと読む)

(もっと読む)

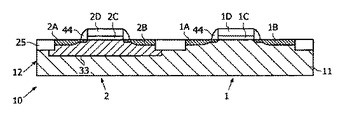

半導体装置及びその製造方法

本発明は、それぞれ金属及びさらなる元素の両方を含む化合物の第1及び第2の導電材料を有するゲート領域(1D,2D)を持つNMOST1及びPMOST2を備えるCMOS装置(10)に関する。本発明によれば第1及び第2の導電材料は共に前記金属としてモリブデンとタングステンとを含む群から選択される金属を含む化合物を有し、前記第1の導電材料は前記さらなる元素として酸素を有し、前記第2の導電材料は前記さらなる元素としてカルコゲナイドを有する。本発明はこのような装置の魅力的な製造方法を提供する。  (もっと読む)

(もっと読む)

反射防止コーティング及び積層配線ライン

【解決手段】 チタニウム−アルミニウム−窒素(「Ti−Al−N」)が半導体基板上に積層されて反射防止コーティングとしての役割を果たす。配線ラインの実施の形態に対して、アルミニウム導電層(54)及びアルミニウム−チタニウム下層(52)は、反射防止キャップ層の下に形成される。

【効果】 配線ライン製造プロセスに対して、Ti−Al−N層は、製造中の不要なフォトリソグラフ光(即ち、光子)の反射を防止するキャップ層(56)としての役割を有する。電界放射ディスプレイ装置(FED)(150)に対して、Ti−Al−N層は、ディスプレイスクリーン(118)のアノードに由来する光がトランジスタ接合部を通過して装置動作を妨害するのを防止する。Ti−Al下層は熱処理中にアルミニウム導電層に起きる収縮を低減する。

(もっと読む)

1,041 - 1,060 / 1,113

[ Back to top ]