Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

941 - 960 / 1,113

半導体装置とその製造方法

【課題】本発明は、CMOSトランジスタにおいて、nチャネル型トランジスタとpチャネル型トランジスタの両方に同一のメタルゲート材料を用いて好ましい、半導体装置と製造工程の効率が向上する製造方法を提供する。

【解決手段】nチャネル型トランジスタは、不純物領域と、ゲート酸化膜、ゲート電極からなるゲート電極側壁絶縁膜を有していない第1のゲート積層体と、半導体基板の表面および前記第1のゲート積層体を覆う引張応力を有する第1のシリコン窒化膜とを備え、前記半導体基板の第2の領域に配置されてなるpチャネル型トランジスタは、不純物領域と、ゲート酸化膜、ゲート電極およびゲート電極側壁絶縁膜からなる第2のゲート積層体と、半導体基板の表面および前記第2のゲート積層体を覆う圧縮応力を有する第2のシリコン窒化膜とを備える。

(もっと読む)

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

プラズマ加速原子層成膜のシステムおよび方法

プラズマ加速原子層成膜(PEALD)処理を用いて、基板上に膜を設置する方法であり、当該方法は、前記PEALD処理を行うことができるように構成された処理チャンバ内に、前記基板を配置するステップを有する。処理チャンバ内に、第1の処理材料が導入され、処理チャンバ内に、第2の処理材料が導入される。第2の処理材料の導入の間、処理チャンバには、600Wを超える電磁力が結合され、基板の表面での第1および第2の処理材料の間の還元反応を促進するプラズマが発生する。第1の処理材料と第2の処理材料の交互の導入により、基板上に膜が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造方法に関し、銅配線上の酸化銅を十分に除去しつつ、水分及びCu拡散防止用の絶縁膜を低誘電率絶縁材料により形成しうる半導体装置及びその製造方法を提供する。

【解決手段】表面に酸化銅膜が形成された銅配線上に、銅に対して拡散バリア性を有するシリコン化合物と、酸化銅を還元する有機化合物とを含む絶縁膜形成用組成物を塗布する工程と、熱処理により、有機化合物によって酸化銅膜を還元して除去するとともに、シリコン化合物を硬化してシリコン化合物よりなる絶縁膜を形成する工程とを有する。

(もっと読む)

パターン化された基板上にルテニウム金属層を形成する方法

ルテニウム金属層(560)を形成する方法は、成膜システム(1、100)の処理チャンバ(10、110)内に、パターン化された基板(25、125、500)を提供するステップであって、前記パターン化された基板(25、125、500)は、1もしくは2以上のビア、溝またはこれらの組み合わせを有するステップと、原子層成膜処理法で、前記基板(25、125、500)上に、第1のルテニウム金属層(540)を成膜するステップと、熱化学気相成膜処理法で、前記第1のルテニウム金属層(540)の上部に、第2のルテニウム金属層(550)を成膜するステップと、を有する。成膜されたルテニウム金属層(560)は、めっきの拡散バリア層、シード層、またはその両方に使用される。  (もっと読む)

(もっと読む)

マグネトロンスパッタリング装置用Ta材

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,W,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のTa窒化物から成るコンタクトバリアー層のAl含有量を原子数で1×1017個/cm3以下、Ta以外の重金属元素の含有量が1×1017個/cm3以下およびアルカリ金属の含有量が3×1016個/cm3以下に形成することが可能であり、Al濃度が1ppm以下であることを特徴とするマグネトロンスパッタリング装置用高純度Ta材である。

(もっと読む)

MIS型トランジスタおよびその製造方法

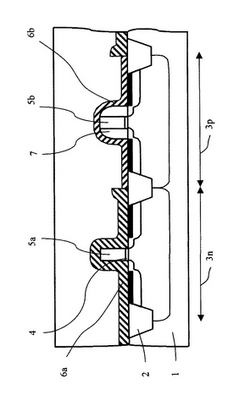

【課題】S/D拡散層抵抗の低減とゲート寄生容量の低減とを同時に実現することのできるMIS型トランジスタ及びその製造方法の提供。

【解決手段】MIS型トランジスタは、半導体基板と、この基板上に形成されたソース・ドレイン領域と、このソース・ドレイン領域間のチャネル領域の上方に設けられたゲート電極と、を備える。このMIS型トランジスタにおいて、前記チャネル形成面を挟んで設けられた前記ソース・ドレイン領域の上面が、前記チャネル形成面よりも嵩上げされてゲート電極側に位置し、かつ、前記ソース・ドレイン領域の上面は、嵩上げされて前記ゲート電極側に位置するレベルの実質的な平坦面と、この平坦面のレベルから前記チャネル形成面のレベルまで傾斜する傾斜面と、を備えると共に、前記チャネル形成面の上側に設けられたゲート絶縁膜により囲まれるゲート電極の形状が、段部を介して下側が先細りとなった断面T字の形状となっている。

(もっと読む)

マグネトロンスパッタリング装置用高純度Ti材の製造方法

【課題】高信頼性の半導体素子を得るために、Ti窒化物から成る膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のTi窒化物から成るコンタクトバリアー層のAl含有量を原子数で1×1018個/cm3以下に形成するためにTi原料からエレクトロンビ−ム溶解法でAlを3ppm以下に除去することを特徴とするマグネトロンスパッタリング装置用高純度Ti材の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】エレクトロマイグレーション耐性の高い銅配線を有する半導体装置を提供すること。

【解決手段】本発明の半導体装置は、基板上に形成された絶縁膜に溝又は孔を形成し、得られた基板上にバリア層25を形成し、バリア層上に銅シード層27を形成し、この銅シード層を利用して電解メッキ法によって銅メッキ層を形成し、表面の銅メッキ層及び銅シード層を除去することにより形成される配線層を有する半導体装置であって、銅シード層は、結晶粒径が異なる小粒層27aと大粒層27bとを備える複数層からなり、小粒層は、バリア層に接触している。

(もっと読む)

タンタル窒化物膜の形成方法

【課題】CVD法により、C、N含有量が低く、Ta/N組成比が高く、Cu膜との密着性が確保されているバリア膜として有用な低抵抗タンタル窒化物膜を形成する方法の提供。

【解決手段】成膜室内に、Ta元素の周りにN=(R,R')(R及びR'は、炭素原子数1〜6個のアルキル基を示し、それぞれが同じ基であっても異なった基であってもよい)が配位した配位化合物からなる原料ガス及びNH3ガスを同時に導入して基板上で反応させて、Ta−NN3を有する還元化合物を生成し、次いでH原子含有ガスを導入してタンタルリッチのタンタル窒化物膜を形成する。また、得られた膜中にスパッタリングによりタンタル粒子を打ち込み、さらにタンタルリッチとする。

(もっと読む)

パターン付基板及びその形成方法、並びに半導体装置及びその作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパターン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留まり高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合する膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成することを特徴とする。

(もっと読む)

タンタル窒化物膜の形成方法

【課題】CVD法により、C、N含有量が低く、Ta/N組成比が高く、Cu膜との密着性が確保されているバリア膜として有用な低抵抗タンタル窒化物膜を形成する方法の提供。

【解決手段】成膜室内に、Ta元素の周りにN=(R,R')(R及びR'は、炭素原子数1〜6個のアルキル基を示し、それぞれが同じ基であっても異なった基であってもよい)が配位した配位化合物からなる原料ガス及びハロゲンガスを導入してTaNx(Hal)y(R,R')z化合物膜(Halは、ハロゲン原子を表す)を形成し、次いでH原子含有ガスを導入してハロゲン化生成物と反応させてタンタルリッチのタンタル窒化物膜を形成する。また、得られた膜中にスパッタリングによりタンタル粒子を打ち込み、さらにタンタルリッチとする。

(もっと読む)

タンタル窒化物膜の形成方法

【課題】C、N含有量が低く、Ta/N組成比が高く、Cu膜との密着性が確保されているバリア膜として有用な低抵抗タンタル窒化物膜の形成方法の提供。

【解決手段】真空チャンバ内に、Ta元素の周りにN=(R,R')(R及びR'は、炭素原子数1〜6個のアルキル基を示し、それぞれが同じ基であっても異なった基であってもよい)が配位した配位化合物からなる原料ガスを導入して基板上に吸着させた後に、酸素原子含有ガスを導入してTaOxNy(R,R')zを生成し、次いで活性化した反応ガスを導入してTaに結合した酸素を還元し、かつ、Nに結合したR(R')基を切断除去し、Taリッチのタンタル窒化物膜を形成する。また、得られた膜中にスパッタリングによりタンタル粒子を打ち込み、さらにタンタルリッチとする。

(もっと読む)

銅配線層、銅配線層の形成方法、半導体装置、及び半導体装置の製造方法

【課題】広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な銅配線層の形成方法を提供すること。

【解決手段】基板上に銅シード層のパターンを形成する工程、及び前記銅シード層のパターン上に銅配線層を無電解めっき法で形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置、電子機器、半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】節を有する形状の導電層を、均一な間隔をもって隣接して形成する。隣接する導電層において、吐出する液滴の中心の位置が線幅方向に一致しないように、配線の長さ方向にずらして吐出する。液滴の中心がずれているので、導電層同士の線幅の最大個所(節の最大値)同士が隣接することがなく、より狭い間隔に隣接して設けることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む。より具体的には、ショットキ金属層15は、多結晶金属層32aと、この多結晶金属層32aの表面および粒界に形成された金属窒化物層32bとを有する金属窒化物含有多結晶金属層32を有している。

(もっと読む)

半導体素子の配線形成方法

【課題】トレンチ内に主金属配線材料の占有体積を十分確保すると同時に、Fアタック問題およびWボルカーノ問題を防止することが可能な半導体素子の配線形成方法を提供する。

【解決手段】所定の構造物が形成された半導体基板に層間絶縁膜を形成する段階と、前記層間絶縁膜に半導体基板の一定の領域を露出させるトレンチを形成する段階と、前記トレンチを含んだ全表面上に接着層と第1バリア金属膜を順次形成する段階と、前記トレンチの下部に第2バリア金属膜を形成する段階と、前記トレンチ内に配線を形成する段階とを含んでなる。

(もっと読む)

エッチング液組成物及び薄膜トランジスタ表示板の製造方法

【解決課題】配線が良好なプロファイルが得られるエッチング液組成物及び、これを利用した薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】本発明は、60乃至75重量%のリン酸、0.5乃至15重量%の硝酸、2乃至15重量%の酢酸及び0.1乃至15重量%の硝酸アルミニウムを含有するエッチング液組成物及び前記エッチング液組成物を利用した薄膜トランジスタ表示板の製造方法を提供する。

(もっと読む)

原子層堆積のための表面のプラズマ前処理

集積回路内のデュアルダマシン構造のコンフォーマルなライニングのための方法および構造を提供する。好ましい実施形態は、多孔性物質で形成された開口を覆うコンフォーマルなライニングの提供に向けられる。トレンチが絶縁層内に形成される(100)。その後、その層が、特別のプラズマプロセスで適切に処理される(101)。このプラズマプロセスに引き続き、自己制限的、自己飽和的原子層堆積(ALD)反応(115)が、細孔の著しい埋め込みなしに起こり、改善された相互接続を形成する。 (もっと読む)

受け渡し機構及び処理装置

【課題】押し上げピンの昇降の際に、パーティクルを発生させるような接触や破損するような衝突や摺動を防止することができる処理装置を提供する。

【解決手段】ウエハWを載置する載置台202に複数設けられたピン挿入孔312に押し上げピン311が嵌入されている。押し上げピン311は、上端面が平坦であり、下端には貫通しない範囲で嵌合穴314が形成されている。嵌合穴314には位置決め駆動ピン315の上端部分が挿入され、位置決め駆動ピン315の下端は押し上げ部材316に貫装して固定されている。押し上げピン311の外径は、ピン挿入孔312内径よりもやや小さくなっており、僅かな隙間313ができるようにする。ピン挿入孔312はウエハWの裏面と載置202の上面との間の空間S1と、載置台202の裏面側(下方)の空間S2とを隙間313を介して連通している。

(もっと読む)

941 - 960 / 1,113

[ Back to top ]