Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

981 - 1,000 / 1,113

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置の製造方法は、第1の高さのフィン型半導体領域うえに、第1の高さより高い第2の高さの絶縁ゲート電極構造を形成し、サイドウォール絶縁膜をフィン型半導体領域の側面からは完全に異方性エッチングで除去し、フィン型半導体領域近傍のゲート電極両側面ではフィン型半導体領域の上面、側面をサイドウォール絶縁膜が囲むように、ゲート電極両側面上下部を残して上部上からエッチング除去し、フィン型半導体領域の少なくとも露出している両側面に上端から下端までシリサイド層を形成する。層間絶縁膜形成後、フィン型半導体領域の両側面のシリサイド層を露出するコンタクトホールを形成し、導電性プラグを埋め込む。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び液晶表示装置

【課題】

本発明は、アルミ二ウム配線で発生するヒールロックを減少させる、薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】

本発明による薄膜トランジスタ基板は、下部アルミ二ウム層と、前記下部アルミ二ウム層の上に形成されている窒化アルミ二ウム層と、前記窒化アルミ二ウム層の上に形成されている上部アルミ二ウム層を含むことを特徴とする。

(もっと読む)

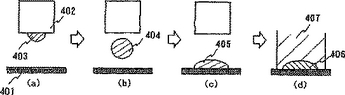

半導体集積回路装置の製造方法

【課題】絶縁膜に形成した溝の内部に導電層を形成する方法を提供する。

【解決手段】酸化シリコン膜24に形成した溝25の内部にアモルファスシリコン膜26Aを堆積し、続いてアモルファスシリコン膜26Aの上部にフォトレジスト膜30をスピン塗布する。次に、フォトレジスト膜30の全面に露光光を照射して溝25の外部のフォトレジスト膜30を露光する。このとき、溝25の内部のフォトレジスト膜30は、露光量が不足するので露光されない。次に、フォトレジスト膜30を現像して露光部である溝25の外部のフォトレジスト膜30を除去した後、溝25の内部に残った未露光のフォトレジスト膜30をマスクにしたドライエッチングで溝25の外部のアモルファスシリコン膜26Aを除去する。

(もっと読む)

荷電ビームを用いた液滴吐出装置及び該装置を用いてのパターンの作製方法

液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。本発明は、主に絶縁表面を有する基板上において、液滴吐出法によってレジスト材料或いは配線材料等を直接パターニングを行うに際し、液滴着弾精度を飛躍的に向上させることが可能になる。具体的には、液滴吐出法による液適の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させることを特徴とする。  (もっと読む)

(もっと読む)

銅裏面金属構造を備えるGaAs薄型ダイ

薄型GaAs基板(310)に銅裏面金属層(340)を設けてGaAs基板を従来のプラスチックパッケージング技術を使用してパッケージングすることができるようにする。GaAs基板に銅裏面金属層を設けることにより、GaAs基板を2ミル(約50ミクロン)未満に薄くできるので、熱放散の問題を軽減することができ、かつ半導体ダイに軟質はんだ技術を適用することができる。プラスチックパッケージへの半導体ダイのパッケージングを可能にすることにより、コストを大きく減らすことができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 パッド電極下に能動層が配置されている場合においても、パッド電極下における密着性を確保しつつ、バリアメタル構造を能動面上に安定して形成できるようにする。

【解決手段】 不純物拡散層5a、5bの表面が覆われるようにして層間絶縁膜6上にバリアメタル膜8を形成し、フォトリソグラフィー技術を用いることにより、開口部7が覆われるようにしてパッド電極16下に配置されるバリアメタル膜8の表面を露出させるレジストパターンRを形成し、レジストパターンRをマスクとして、バリアメタル膜8をエッチングすることにより、パッド電極16下に配置される層間絶縁膜6上のバリアメタル膜8を除去し、バリアメタル膜8を介してゲート電極4および不純物拡散層5a、5bに接続された配線層9を層間絶縁膜6上に形成し、ゲート電極4および不純物拡散層5a、5b上に配置されたパッド電極16を形成する。

(もっと読む)

液滴吐出装置、パターンの形成方法、および半導体装置の製造方法

本発明では液滴吐出装置から吐出された液滴が基板に着弾した後の位置制御を改善することが可能なパターンの作製方法を提供する。また着弾後の液滴位置精度を改善することが可能な液滴吐出装置を提供する。更には、本発明の液滴吐出装置を用いた半導体装置の製造方法を提供する。

本発明は、吐出部から吐出された液滴、又は液滴を着弾する基板にレーザ光を照射して、液滴の着弾位置を制御することを特徴とする。本発明によりフォトリソグラフィー工程を用いることなくパターンを形成することが可能である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】開口径が微細化され、高アスペクト比化されたコンタクトホールに対して、Ti膜及びTiN膜の機能を保持したまま、W膜の埋め込み特性を向上させる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板101の上面にNiSi層102を形成し、半導体基板101の上に層間絶縁膜103を堆積した後、層間絶縁膜103にコンタクトホール104を形成する。次に、層間絶縁膜103上に、コンタクトホールを覆うようにTi膜105を形成し、プラズマ窒化の処理を行う。これにより、Ti膜105における層間絶縁膜103の上面とコンタクトホールの底面にTiN膜106が形成される。次に、Ti膜105の上にコンタクトホールを埋め込むようW膜107を形成する。

(もっと読む)

半導体装置の製造方法

【課題】

広い範囲の有効領域を確保し、かつ、洗浄工程を簡素化することができる方法で導電体配線を形成することができる半導体装置の製造方法を提供すること。

【解決手段】

本発明の半導体装置の製造方法は、半導体基板上の絶縁膜に設けられた配線溝または接続孔の内部に導電体配線を形成する工程を備え、この導電体配線を形成する工程は、前記半導体基板上に、前記半導体基板の有効領域にのみ導電体シード膜を形成する工程と、前記導電体シード膜の上に電界メッキ法で導電体メッキ膜を形成する工程と、を備えることを特徴とする。

(もっと読む)

半導体装置とその製造方法

多電圧半導体集積回路装置を製造する簡略化された製造方法を提供する。 半導体装置の製造方法は、(a)半導体基板の第1の領域に第1の厚さの第1のゲート絶縁膜を形成する工程と、(b)前記半導体基板の第2の領域に前記第1の厚さより薄い第2の厚さの第2のゲート絶縁膜を形成する工程と、(c)前記第1および第2のゲート絶縁膜上にゲート電極を形成すると共に、前記第1および第2の領域上の前記第1及び第2のゲート絶縁膜を残す工程と、(d)前記第1および第2のゲート絶縁膜を介して、前記第1および第2の領域に不純物をイオン注入し、前記第1の領域に第1の低濃度、前記第2の領域に前記第1の低濃度より高い第2の低濃度の不純物を添加する工程と、(e)少なくともコンタクトを形成する領域の前記第1および第2のゲート絶縁膜を除去する工程と、(f)前記第1および第2の領域中、前記コンタクトを形成する領域を含む領域に高濃度の不純物を添加する工程と、を含む。  (もっと読む)

(もっと読む)

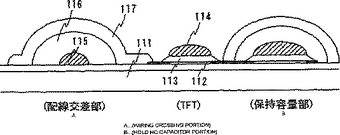

半導体装置およびその作製方法

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの特性に適応した仕事関数をもつデュアルメタルゲートを備え、トランジスタ特性や信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に、ゲート絶縁膜3および金属層4を形成する。nMOS領域あるいはpMOS領域のいずれか、例えばpMOS領域にバリアメタル層5を形成した後に、全面に導電層6として例えばポリシリコンを成膜する。nMOS領域およびpMOS領域において、ゲート電極形状に加工した後に、熱処理を行う。これにより、nMOS領域では、金属層4と導電層6の合金層7からなる第2ゲート電極G2が形成される。pMOS領域では、バリアメタル層5により金属層4と導電層6との反応が抑制され、積層膜からなる第1ゲート電極G1となる。

(もっと読む)

窒化金属膜作製装置、窒化金属膜作製方法及び窒化金属膜

【課題】窒化金属膜及び該窒化金属膜を作製する窒化金属膜作製装置及び作製方法を提供する。

【解決手段】基板3を支持台2に載置して収容したチャンバ1の内部において、ヘリウムで希釈した塩素ガスプラズマ16により、タンタルで形成した被エッチング部材14をエッチングして塩化タンタルガスからなる前駆体17を生成し、基板3の温度を被エッチング部材14の温度よりも低くして前駆体17を基板3に吸着させ、塩素ガスプラズマにより吸着した前駆体17を還元してタンタル成分を基板3に成膜する際に、窒素ガスをプラズマ化して得られる窒素ガスプラズマによりタンタル成分を窒化して、基板3に窒化金属膜18を成膜する窒化金属膜作製方法において、窒素ガスの供給量を制御して窒素ガス/ハロゲンガス流量比を0より大きく0.1以下とし、窒化金属膜18の窒素原子と金属原子の原子組成比であるN/M比を0より大きく1以下となるようする。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗性及び信頼性を同時に確保する。

【解決手段】基板110、該基板上に形成されゲート電極124を備えるゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173を備えるデータ線及びソース電極と対向しているドレイン電極175、データ線及びドレイン電極上に形成されている保護膜180、及びドレイン電極と接続されている画素電極190を備える。ゲート絶縁膜及び保護膜の少なくとも一方の下部にケイ素を含むカバー層801、803を備えている。これにより、接着性が向上し、配線抵抗を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール側壁のバリアメタル層の抵抗を下げることにより、コンタクト抵抗を低抵抗化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に層間絶縁膜3を形成し、層間絶縁膜3にコンタクトホール3aを形成した後に、コンタクトホール3aの底部および側壁に、チタン(Ti)層4aおよび窒化チタン(TiN)層4bからなるバリアメタル層4を形成する。その後、コンタクトホールの側壁におけるバリアメタル層4にイオン注入することにより、バリアメタル層4中に含まれる炭素等の不純物を除去する。イオン注入後、コンタクトホール3a内に埋め込み導電層6を形成することにより、バリアメタル層4および埋め込み導電層6からなるコンタクトが形成される。

(もっと読む)

表示装置用配線、該配線を有する薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗特性及び信頼性を同時に確保する。

【解決手段】導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する表示装置用配線と、基板110、該基板110上に形成されているゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されているソース電極173を含むデータ線171及びソース電極173と対向しているドレイン電極175、及びドレイン電極175と接続されている画素電極190を有している。ゲート線とデータ線171及びドレイン電極175の少なくとも一方とは、導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する。これにより、配線の密着性が向上するので剥離を防止することができ、信頼性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

めっき装置及びめっき方法

【課題】 比較的簡単な構成で、例えアスペクト比が高く、深さが深いビアホール等にあっても、内部にボイドを発生させることなく、金属膜を確実に埋込むことができるようにする。

【解決手段】 めっき液188を保持するめっき槽186と、基板Wを保持して該基板に通電し、基板の被めっき面をめっき槽内のめっき液に接触させるホルダ160と、めっき槽内のめっき液に浸漬させて配置されるアノード214と、アノードとホルダで保持した基板との間に配置され、めっき槽内のめっき液を攪拌するめっき液攪拌部220,224と、基板とアノードとの間に電圧を周期的に印加するめっき電源230を有し、基板とアノードとの間に電圧が印加されていない時にめっき液攪拌部によるめっき液の攪拌を行い、基板とアノードとの間に電圧が印加されている時にめっき液攪拌部によるめっき液の攪拌を停止する。

(もっと読む)

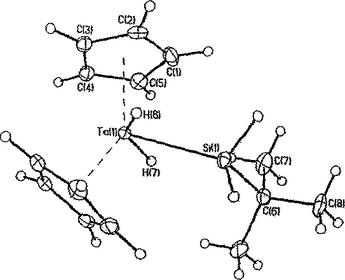

タンタル系材料の蒸着のための化学蒸着前駆体

タンタル含有材料、たとえば、タンタル、TaN、TaSiNなどの基板上への化学蒸着に好適なタンタル前駆体を開示する。該タンタル前駆体は置換シクロペンタジエニルタンタル化合物である。本発明の一態様では、かかる化合物はタンタル/シリコン源試薬を構成するためにシリル化される。本発明の前駆体は、半導体デバイス構造の銅メタライゼーションに関連して拡散バリアを形成するために半導体製造用途で有利に使用される。  (もっと読む)

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

981 - 1,000 / 1,113

[ Back to top ]