Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

1,061 - 1,080 / 1,113

LCDのTFT基板及びその製造方法

【課題】 液晶表示装置の薄膜トランジスタ基板及びその製造方法が開示されている。

【解決手段】 シリコン元素を含む基板、前記基板上に形成された拡散防止膜、及び前記拡散防止膜上に形成され、前記拡散防止膜形成物質が0.5〜15at%範囲で含まれた銅合金層を含んで形成される。前記拡散防止膜は、Zr、Ti、Hf、V、Ta、Ni、Cr、Nb、Co、Mn、Mo、W、Rh、Pd、Pt等のような化合物を50〜5000Å範囲で蒸着して熱処理して、シリサイド化合物に変換して製造する。銅合金配線を用いてトランジスタ基板を製造するので、低い抵抗と高い伝導度を具現することができる。又、薄い厚さの拡散防止膜と同じ元素を添加した銅合金と用いて銅配線を形成したので、同時エッチングが可能であり、後続工程で基板との相互拡散を防止することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

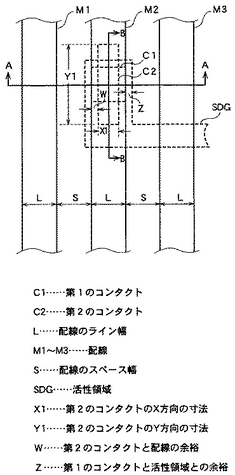

【課題】 配線及びコンタクトを微細化しながら活性領域の増大を抑制して、配線と活性領域とのコンタクトを良好に保つ。

【解決手段】 半導体装置では、配線M1乃至M3がY方向に平行して設けられ、配線直下に活性領域SDGが設けられ、配線M2が第1のコンタクトC1及び第2のコンタクトC2を介して活性領域SDGと接続されている。第1のコンタクトC1は、配線M2よりも幅の広い活性領域SDG内に、第1のコンタクトと活性領域との余裕Zだけ内側に設けられ、開口部にコンタクトプラグ6が埋設されている。配線M2内に設けられた第2のコンタクトC2は、第1のコンタクトC1上に第1のコンタクトC1と接して設けられ、X方向の寸法X1が第1のコンタクトC1及び配線M2よりも第2のコンタクトと配線の余裕Wの2倍分だけ小さく、且つY方向の寸法Y1が第1のコンタクトC1よりも大きく、活性領域SDGの外側まで設けられている。

(もっと読む)

半導体素子の製造方法およびマグネトロンスパッタリング装置用Ti材の製造方法

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,W,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】Ti原料からAlを除去してAl濃度が3ppm以下であるマグネトロンスパッタリング装置用Ti材を調製し、このTi材を用いてAl含有量が原子数で1×1018個/cm3以下であり結晶質または非晶質であるコンタクトバリアー又はゲート電極層をスパッタリング法により形成することを特徴とするソース−ドレイン領域の接合深さが0.3μm以下である半導体素子の製造方法である。

(もっと読む)

成膜方法

【課題】 金属と窒素と炭素を含む第1の処理ガスと、当該第1の処理ガスを還元する第2の処理ガスを交互に供給して薄膜を形成する成膜方法において、前記薄膜に含まれる、前記金属、窒素、および炭素のうち、少なくともいずれか一つの含有率の制御することを可能とすること。

【解決手段】 被処理基板を保持する保持台を内部に備えた処理容器に、金属と窒素と炭素を含む第1の処理ガスと、当該第1の処理ガスを還元する第2の処理ガスを供給し、前記被処理基板上に薄膜を形成する成膜方法であって、前記処理容器に前記第1の処理ガスを供給する第1の工程と、前記処理容器に前記第2の処理ガスを供給し、前記処理容器に設けられたプラズマ励起手段によって当該第2の処理ガスをプラズマ励起する第2の工程と、を有し、前記プラズマ励起手段に印加される高周波電力を変更することにより、前記薄膜に含まれる、前記金属、窒素、および炭素のうち、少なくともいずれか一つの含有率を制御することを可能としたことを特徴とする成膜方法。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜に取り込まれる不純物を低減させて、凹部内の配線における欠陥を減少させることが可能な半導体装置の製造方法を提供する。

【解決手段】まず、表面にビアホール1a及び配線溝1bを有するウェハWをめっき液に浸漬させ、かつウェハWとアノード11との間に電圧を印加して、ウェハW上にめっき膜4を形成する。めっき膜4を形成した後に、電圧を印加した状態でウェハWをめっき液から取り出す。そして、シード膜3及びめっき膜4に熱処理を施し、結晶を成長させて、配線膜5を形成する。最後に、ビアホール1a及び配線溝1bに埋め込まれた部分以外の配線膜5等を除去し、配線5aを形成する。

(もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミンおよび1,3−ジイミン銅錯体ならびに原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

配線形成方法及び配線形成装置

【課題】 絶縁膜の材料の違いによってプロセス条件を変えたりすることなく、配線の表面に金属膜を選択的に成膜でき、しかも、不要となったバリア膜を、機械的な要素が相対的に少ない方法で除去できるようにする。

【解決手段】 絶縁膜10内に配線用凹部12を形成した基板表面にバリア膜14を形成し、次いで配線用凹部12内ならびに基板表面に配線材料16を成膜した基板Wを用意し、基板表面に成膜した余剰の配線材料16を除去して配線用凹部12内に埋込んだ配線材料16で配線18を形成するとともに、該配線形成部以外のバリア膜14を露出させ、配線18の表面に金属膜20を選択的に成膜する。

(もっと読む)

銅の配線層を形成する方法

【課題】 少なくとも1つの窪みを有する第1領域と、前記少なくとも1つの窪みのアスペクト比とは異なるアスペクト比を有する窪みが複数個並んだ第2領域とを有する半導体構造に、低コストで銅の配線層を形成する方法を提供すること。

【解決手段】 本方法は、線幅の異なる2以上の溝を有する半導体構造に、第1の硫酸濃度を有するめっき液で銅の導電層を形成する第1工程と、前記第1の硫酸濃度より薄い第2の硫酸濃度を有するめっき液で、前記導電層上に更に導電層を積層する第2工程と、前記半導体構造上に成膜された銅の導電層を研磨する研磨工程とを有する。これにより、線幅の異なる2以上の溝を有する半導体構造に、低コストで銅の配線層を形成することができる。

(もっと読む)

バリア膜形成方法

【課題】バリア性に優れたバリア膜を提供する。

【解決手段】真空槽内に基板を搬入して(S1)、昇温させ(S2)、含窒素ガスと含高融点金属ガスのうち、一方のガスを導入し(S3)、該一方のガスを真空排気した後(S4)、他方のガスを導入し(S5)、該他方のガスを真空排気する(S6)。この工程を複数回繰り返して行うと(S9)、基板表面に吸着された一方のガスと、後から導入された他方のガスとの間でCVD反応が生じるので、コンタクトホール内にバリア膜がコンフォーマルに成長し、ステップカバレージのよいバリア膜を得ることができる。CVD反応を行う毎にパージガスを導入し(S7)、真空排気すると(S8)、基板や真空槽に吸着された副生成物ガスや未反応ガスがパージガスと交換されるので、より高純度なバリア膜を得ることが可能となる。

(もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミン銅錯体および原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

絶縁ゲート型電界効果トランジスタの製造方法

【課題】絶縁ゲート型電界効果トランジスタの製造方法において、ゲート−ドレイン間の絶縁不良を増やすことなく、より短時間に効率的にトレンチ埋め込み絶縁膜を形成することのできる絶縁ゲート型電界効果トランジスタの製造方法を提供すること。

【解決手段】第一TEOS酸化膜を前記トレンチ間に凹部が残る厚さに堆積してアニール処理をすることにより前記トレンチ間に第一絶縁膜を形成する工程と、該第一絶縁膜上に第二TEOS酸化膜からなる第二絶縁膜を形成する工程とから前記トレンチ内に埋め込まれる絶縁膜を形成する絶縁ゲート型電界効果トランジスタの製造方法とする。

(もっと読む)

酸素架橋構造及び方法

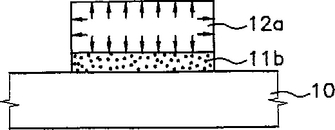

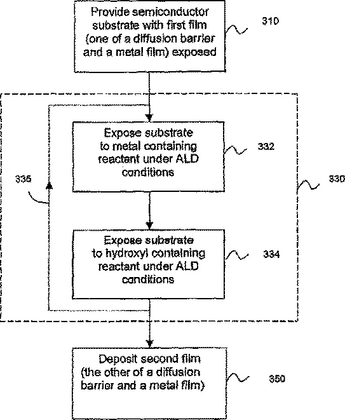

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

ショットキダイオードを含む半導体装置及びその製造方法

【課題】 本発明は、比較的低いコストにより、比較的低いシリーズ抵抗を有するショットキダイオードを含む半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 ショットキダイオードにおいて、ウェル領域の表面領域の不純物濃度はそのウェル領域の不純物濃度よりも小さく、ウェル領域の表面領域より深い、所定の深さ領域の不純物濃度はそのウェル領域の不純物濃度よりも大きく分布する、ウェル領域と同一型の不純物の濃度分布をウェル領域内に設定する。

(もっと読む)

薄膜形成方法

【課題】プラズマ前処理を行うこともなく、低温で、比抵抗が低く、酸化物膜やCu配線膜に対する密着性が優れ、またCu配線の信頼性を損なうことのないバリアメタル膜であるW系金属薄膜を形成する方法の提供。

【解決手段】真空チャンバー102内に原料ガス(WF6、W(CO)6ガス等)を導入する工程と、化学構造中に水素原子を含んだ反応性ガス(H2、NH3、SiH4、NH2NH2ガス等)を触媒体108に接触させて活性種にしてから真空チャンバー102内に導入する工程とからなるCAT−ALD法により成膜する。

(もっと読む)

半導体装置の製造方法

【目的】 ポーラス状に形成される多孔質低誘電率(p−lowk)膜内へのバリアメタルに用いたメタルの拡散を抑制することを目的とする。

【構成】 p−lowk膜を基体上に形成するp−lowk膜形成工程(S102)と、前記p−lowk膜表面側に形成される空孔が前記p−lowk膜内部側の空孔へ連結する連結位置における開口サイズより大きい分子(Ta−R1)を前記p−lowk膜表面に吸着させるTa[N(C2H5)2]5供給工程(S106)と、前記分子(Ta−R1)と反応するNH3を供給し、TaN膜を形成するNH3供給工程(110)と、前記開口サイズより小さい分子(Ta−R2)を吸着させるTaCl5供給工程(S114)と、前記分子(Ta−R2)と反応するNH3を供給し、TaN膜をさらに形成するNH3供給工程(120)と、を備えたことを特徴とする。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

素性構造及びウエハの均一な被覆率のため、磁場エンベロープの移動を伴う強くイオン化されたPVD

本発明は半導体ウエハのイオン化PVDプロセスに関し、単一プロセスチャンバ内の高い均一性の堆積−エッチングプロセスシーケンス及び高アスペクト比形状の被覆能力用状態を供する。プラズマは誘起結合プラズマ供給源で発生維持される。堆積プロセス段階は金属蒸気のPVD供給源のターゲットから発生中に行われる。ターゲット表面での位置やスパッタリング効率は磁場エンベロープの移動や掃引を生じて磁石の束の移動で増大する。ターゲットはDC供給源から電圧を印加されてスパッタリングされた原子の効率的熱運動化用の有効圧力が堆積中チャンバ内で保持される。ウエハ上での一様な厚さは各磁石の掃引サイクルで形成される。全ターゲット表面に亘る環状の掃引運動を用いた磁場の局在化は、合理的堆積率、高ターゲット利用率、金属原子の高イオン化、一様平坦領域堆積及びエッチング用状態、ウエハ中心及び端でHAR形状の被覆率に略同一な状態を生じる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ダマシンゲートトランジスタのゲート絶縁破壊を抑制し、デバイスの信頼性を確保することのできる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1の上に、犠牲ゲート絶縁膜104および犠牲ゲート電極105を形成した後、犠牲ゲート電極105の側面に第1の側壁膜106を形成する。次に、第1の側壁膜106を介して、犠牲ゲート電極105の側面に、第1の側壁膜106とエッチングレートの異なる第2の側壁膜110を形成する。ここで、第1の側壁膜106の膜厚は、犠牲ゲート絶縁膜104の膜厚より厚くなるようにする。これにより、第1の側壁膜106および犠牲ゲート絶縁膜104をウェットエッチングする際のプロセスマージンを大きくして、第2の側壁膜110のゲート電極側下部にスリットが入るのを防ぐことができる。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】 正常時に経時変化するパラメータに対して異常変動が生じた場合に、異常を検知することができる半導体装置の製造方法を提供する。

【解決手段】 まず、異常判断部は、受信部より所定時刻(第2時刻)の第2印加電圧値を入力する(S101)。そして、所定時刻の直前の時刻(第1時刻)に受信部から入力した正常な第1印加電圧値に基づいて、許容範囲を設定する(S102)。続いて、設定した許容範囲に第2印加電圧値が入っているかを判断する(S103)。そして、第2印加電圧値が設定した許容範囲から外れている場合、第2印加電圧値が異常値であると異常判断部は判断してアラームを送信部に出力する(S104)。一方、第2印加電圧値が設定した許容範囲に入っている場合、第2印加電圧値が正常値であると異常判断部は判断する(S105)。以下、上述した動作を繰り返す。

(もっと読む)

1,061 - 1,080 / 1,113

[ Back to top ]