Fターム[4M104GG16]の内容

Fターム[4M104GG16]に分類される特許

201 - 220 / 869

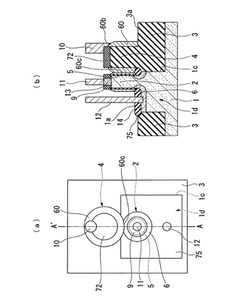

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法。

【課題】本発明は、埋込みビットラインの抵抗を減少させ高速動作に有利な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ハードマスク膜をバリアとして半導体基板をエッチングし、複数の活性領域を画定するトレンチを形成するステップと、ハードマスク膜が突出部となるように前記トレンチ内部を一部ギャップフィルするギャップフィル膜を形成するステップと、突出部の両側側壁を覆うスペーサを形成するステップと、ドープドエッチング障壁膜をエッチングバリアとしてスペーサのうち何れか1つのスペーサを除去するステップと、残留するスペーサをエッチングバリアとして前記ギャップフィル膜をエッチングし、活性領域の一側側壁を露出させる側壁トレンチを形成するステップと、を含む。

(もっと読む)

誘電体膜をパッシベーションする方法

塩素、臭素又はヨウ素と反応しやすい誘電体材料にフッ素を含むパッシベーション層を堆積する方法が本明細書に開示される。パッシベーション層は、反応しやすい誘電体層を保護することができ、それにより、パッシベーション層に塩素、臭素又はヨウ素を含む前駆体を用いて堆積が可能となる。 (もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

基板処理装置および半導体装置の製造方法

【課題】ターゲットの角度を調整可能な基板処理装置を提供する。

【解決手段】基板処理装置は、イオンを発生させるイオン源と、該イオン源が発射したイオンビームが照射されるターゲットと、該ターゲットを保持するターゲットホルダと、前記ターゲットからはじき出されたターゲット成分粒子が堆積する位置で基板を保持する基板ホルダと、前記ターゲットの前記イオンビームに対する角度を調整する角度調整部と、を有している。ターゲットホルダに保持されたターゲットの角度を角度調整部により調整し、イオン源が発射したイオンビームを前記ターゲットに照射させて前記ターゲットからはじき出されたターゲット成分を基板ホルダに保持された基板に堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】CMPのストッパ膜として多結晶シリコン膜を用いた場合においても、多結晶シリコン膜の表面に発生するスクラッチを低減させる。

【解決手段】半導体基板11上に形成された多結晶シリコン膜13をストッパ膜としてシリコン酸化膜15を化学的機械的研磨にて平坦化する半導体装置の製造方法において、多結晶シリコン膜13の上層には表面改質膜13aが形成され、化学的機械的研磨のスラリ8には、セリア砥粒21と、界面活性剤と、カチオン性またはアニオン性の官能基を有する樹脂粒子22、23が含有されている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

半導体装置の製造方法

【課題】溝側面に側壁膜を形成する際に、側壁膜表面にエッチングダメージを受けることなく、側壁膜上面の溝開口部からの深さのばらつきを抑制して形成可能な方法を提供する。

【解決手段】半導体基板主表面に形成された溝の側壁に第1の層を形成する工程、溝を保護膜で埋設する工程、保護膜の表面の高さが溝の開口部よりも低い位置になるようにドライエッチング法でエッチバックし、該エッチバックにより露出した第1の層をエッチング除去する工程、とを含む半導体装置の製造方法。

(もっと読む)

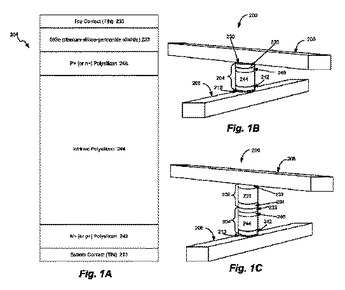

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】外部から印加される電源電圧の仕様に対応した、半導体装置の製造方法を提供する。

【解決手段】チャネルイオン注入工程、ゲート酸化膜形成工程、および、ゲート電極パターニング工程の少なくとも1つの工程を、外部から第1の電源電圧が供給されて動作する第1の半導体装置を製造する場合には第1の電源電圧で動作する素子を形成する工程で行い、外部から第2の電源電圧が供給されて動作する第2の半導体装置を製造する場合には第2の電源電圧で動作する素子を形成する工程で行い、また、第1の半導体装置の製造の場合と第2の半導体装置の製造の場合とで少なくとも拡散領域形成工程を共通に行うものである。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置

【課題】寄生容量を増やさずにソフトエラー率を低減することのできる半導体装置を提供する。

【解決手段】半導体基板の主表面に形成された第1導電型ウェルと、第1導電型ウェルの表面に形成されたトランジスタと、半導体基板の主表面に形成された素子分離絶縁領域と、第1導電型ウェルの表面に前記トランジスタと素子分離絶縁領域を隔てて形成され、底面の深さがおおよそ当該素子分離絶縁領域の底面と等しく、第1導電型ウェルより不純物濃度が高い第1導電型高濃度領域と、第1導電型高濃度領域の表面に形成されたウェルコンタクト電極と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

201 - 220 / 869

[ Back to top ]