Fターム[4M104GG16]の内容

Fターム[4M104GG16]に分類される特許

61 - 80 / 869

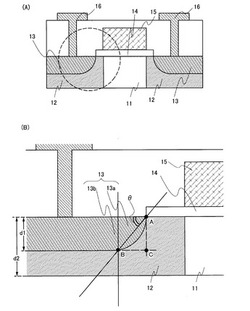

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

電極およびそれを含む電子素子

【課題】優秀な導電性及び大きい仕事関数を有する電極及びそれを含んだ電子素子を提供する。

【解決手段】グラフェン含有層と、前記グラフェン含有層上に形成される仕事関数傾斜層と、を含み、前記仕事関数傾斜層は、前記グラフェン含有層と接触する第1面、及び前記第1面に対向する第2面を有する単一層であり、前記仕事関数傾斜層の仕事関数は、前記第1面から前記第2面に向かう方向に沿って漸進的に増大する電極。

(もっと読む)

大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子

【課題】大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子を提供する。

【解決手段】0.1S/cm以上の電気伝導度を有する導電性物質および低表面エネルギー物質を含み、第1面と、前記第1面に対向する第2面と、を有し、前記第2面の低表面エネルギー物質の濃度が、前記第1面の低表面エネルギー物質の濃度より高く、前記第2面の仕事関数が5.0eV以上であり、かつ前記第2面の電気伝導度が1S/cm以上である大きい仕事関数および高い電気伝導度を有する電極、を具備した電子素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

成膜方法およびリスパッタ方法、ならびに成膜装置

【課題】トレンチおよび/またはホールの間口のオーバーハングを抑制することができる成膜方法およびリスパッタリング方法を提供すること。

【解決手段】処理容器内にプラズマ生成ガスを導入しつつ誘導結合プラズマ生成機構により処理容器内に誘導結合プラズマを生成し、直流電源から金属ターゲットに直流電力を供給し、バイアス電源により載置台に高周波バイアスを印加して、載置台上の被処理基板に金属薄膜を堆積させる工程と、誘導結合プラズマ生成機構によるプラズマの生成と直流電源への給電を停止し、処理容器内にプラズマ生成ガスを導入しつつ載置台に高周波バイアスを印加して、処理容器内に容量結合プラズマを形成するとともにプラズマ生成ガスのイオンを被処理基板に引き込んで堆積された金属薄膜をリスパッタリングする工程とを有する。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

61 - 80 / 869

[ Back to top ]