Fターム[4M104GG16]の内容

Fターム[4M104GG16]に分類される特許

101 - 120 / 869

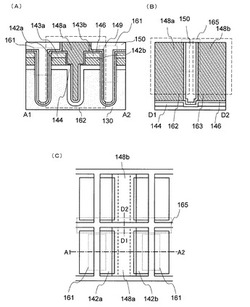

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

拡散バリアー層及びその製造方法

【課題】表面を有する基材アセンブリを提供し、この表面の少なくとも一部の上にバリアー層を提供することを含む、集積回路の製造で使用する方法を提供する。

【解決手段】バリアー層14は、白金(x):ルテニウム(1−x)合金でできており、ここでxは約0.60〜約0.995、好ましくはxは約0.90〜0.98である。バリアー層14は、化学気相堆積によって作ることができ、バリアー層14を形成する表面の少なくとも一部は、ケイ素含有表面でよい。この方法は、キャパシター、蓄積セル、接触ライニング等の製造で使用する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】所望の抵抗値を有する制御ゲートを備えた半導体装置の製造方法を提供すること。

【解決手段】シリコン基板13の表面上に第1の絶縁膜15、電荷蓄積層16、第2の絶縁膜17、およびポリシリコン膜21をこの順で形成する工程と、ポリシリコン膜21上および両側壁全面に金属膜25を形成する工程と、金属膜25が形成されたポリシリコン膜21を加熱してシリサイド化する工程と、金属膜25を除去する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

半導体デバイスの製造方法、基板処理装置および半導体デバイス

【課題】積層構造を備えるゲート電極を同一の処理室内にて形成し、製造コストを低減させて生産性を向上させる。

【解決手段】処理室内に基板を搬入する基板搬入工程と、基板にチタンアルミニウム窒化膜を形成する第1窒化膜形成工程と、基板にチタン窒化膜を形成する第2窒化膜形成工程と、処理室内から基板を搬出する基板搬出工程と、を有し、第1窒化膜形成工程と第2窒化膜形成工程とを同一の処理室内で実施する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

101 - 120 / 869

[ Back to top ]