Fターム[4M106DH16]の内容

半導体等の試験・測定 (39,904) | その他の検査装置 (2,556) | 検出器 (633) | 電気量計 (149)

Fターム[4M106DH16]の下位に属するFターム

Fターム[4M106DH16]に分類される特許

1 - 20 / 101

評価方法

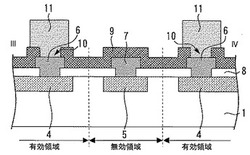

半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体装置の不良解析方法ならびに不良解析装置および不良解析プログラム

【課題】半導体装置の不良解析技術において、解析成功率の向上や解析時間の短縮を図ることができる技術を提供する。

【解決手段】ショートしていると推測される一方の特定配線を特定(S103)し、その相手と推測される隣接配線の抽出(S104)をおこない、両配線間において電圧状態(論理状態)が異なる異電圧時間帯の算出(S107)をし、その異電圧時間帯で発生する発光現象の頻度を調査することにより、上記一方の特定配線に対して、どの隣接する配線がショートしているのかを短時間で確実に推定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】シールリングの内側領域生じたクラックを低コストで検出することができる半導体装置を提供する。

【解決手段】図2に示すように、本実施形態に係る半導体装置は、多層配線層と、内部回路領域3と、多層配線層に形成され、内部回路領域3を囲うシールリング220と、平面視で内部回路領域3とシールリング220とに挟まれた領域に設けられているTEG200と、を含んでいる。TEG200は、多層配線層の少なくとも2層それぞれに設けられ、互いに接続する導体パターン7と、P型ウェル13と、N型ウェル14とによって構成されている。P型ウェル13とN型ウェル14は、平面視で交互に互いに接続された状態で配置されており、P型ウェル13とN型ウェル14のいずれか一つに導体パターン7が接続されている。

(もっと読む)

オゾンガス発生処理装置、酸化珪素膜形成方法、及びシリコン単結晶ウェーハの評価方法

【課題】 オゾンガスでウェーハ表面を処理する際にウェーハの表面に形成される酸化膜厚を薄く調整でき、また、紫外線によりウェーハ表面がダメージを受けないようなオゾンガス発生処理装置、酸化膜珪素膜形成方法、及び、従来よりも安定したC−V特性の測定値を得ることができるシリコン単結晶ウェーハの評価方法を提供することを目的とする。

【解決手段】 紫外線の光源とウェーハ載置部とを有し、酸素含有雰囲気で前記光源より紫外線を照射してオゾンガスを発生させ、前記ウェーハ載置部上のウェーハをオゾンガスで処理するオゾンガス発生処理装置であって、

該オゾンガス発生処理装置は、前記光源と前記ウェーハ載置部上に載置されたウェーハとの間に、前記発生したオゾンガスを通過させかつ前記紫外線を遮光する遮光板を有することを特徴とするオゾンガス発生処理装置。

(もっと読む)

半導体素子の検査方法及び半導体検査装置

【課題】電界効果トランジスタにおける電流コラプスの発生の有無を迅速に判定する。

【解決手段】電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに第1電圧を印加した状態において、電界効果トランジスタ101の第1オン抵抗を算出する第1の工程と、電界効果トランジスタ101をオフ状態にし、前記第1電圧よりも大きい第2電圧を、電界効果トランジスタ101のドレインに印加する第2の工程と、電界効果トランジスタ101をオン状態にするとともに、電界効果トランジスタ101のドレインに前記第2電圧を印加した状態において、電界効果トランジスタ101の第2オン抵抗を算出する。

(もっと読む)

容量測定回路、半導体装置および容量測定方法

【課題】本発明は、特別な装置を用いずに、微細素子の容量を直接測定することができる容量測定回路、半導体装置および容量測定方法を提供する。

【解決手段】本発明に係る容量測定回路1は、少なくとも1つの第1リングオシレータ(測定用リングオシレータ4)と、第1周辺回路部(測定用周辺回路部5)と、第2リングオシレータ(参照用リングオシレータ6)と、第2周辺回路部(参照用周辺回路部7)とを備えている。第1リングオシレータおよび第2リングオシレータに電力を供給する電源と、第1周辺回路部および第2周辺回路部に電力を供給する電源とは異なる。容量測定回路1は、第1出力信号の周波数および第1リングオシレータに流れる電流値より算出した第1容量から、第2出力信号の周波数および第2リングオシレータに流れる電流値より算出した第2容量を差引くことで測定対象の容量を測定することができる。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

ライフタイム値の測定方法及びこれを用いたウエーハの選別方法

【課題】 本発明は、電子線照射後のライフタイム値を簡便に見積もることができ、測定時間を大幅に短縮することができ、デバイス作製の生産性を向上させることができるライフタイム値の測定方法を提供することを目的とする。

【解決手段】 電子線照射後のウエーハのライフタイム値を検査する方法であって、電子線照射前キャリア濃度算出工程、電子線照射前準位密度算出工程、電子線照射工程、電子線照射後キャリア濃度算出工程、キャリア濃度差算出工程、準位密度差算出工程、及びライフタイム値算出工程を有することを特徴とするライフタイム値の測定方法。

(もっと読む)

半導体装置の製造方法及び洗浄装置

【課題】パターニング前工程にて半導体製造基板の歩留りへの影響を受けず、SEMレビューを可能とする半導体装置の製造方法及び洗浄装置を提供する。

【解決手段】製造装置30aにて所定の製造処理が施されたウェハWは、検査装置10にて欠陥が検査された後、評価装置20に搬送される。評価装置20では、検査装置10にて検出された欠陥がSEMレビューされる。そのSEMレビューされたウェハWは、洗浄装置40に搬送され、その表面に有機溶剤が塗布されて洗浄される。その洗浄後のウェハWは、製造装置30bに搬送され、次工程の製造処理が施される。

(もっと読む)

欠陥検査方法および半導体装置の製造方法

【課題】インプリントパターンの欠陥の有無の検査を効率化する。

【解決手段】下地層1上に導電層2を形成し、導電層2上にインプリントパターン4を形成し、インプリントパターン4に電解液6を接触させ、電解液6に電極7を接触させ、導電層2と電極6との間に電圧を印加し、導電層2と電極7との間に流れる電流を計測し、その電流の計測結果に基づいてインプリントパターン4の欠陥の有無を判定する。

(もっと読む)

シート抵抗の測定方法及びシート抵抗測定装置

【課題】製品の半導体チップ毎にシート抵抗を測定することが可能で、また、ウェーハ全面にわたってシート抵抗を測定することが可能なシート抵抗の測定方法を提供する。

【解決手段】半導体装置に形成される寄生トランジスタのコレクタ電流を、エピタキシャル層の不純物濃度及び厚さを変化させて測定するとともに、半導体装置の近傍に形成したTEGにおけるエピタキシャル層のシート抵抗を測定することにより、半導体装置に形成される寄生トランジスタのコレクタ電流とエピタキシャル層のシート抵抗との関係を示す検量線を作成する第1ステップと、測定対象の半導体装置における寄生トランジスタのコレクタ電流を測定するとともに当該コレクタ電流の値を上記した検量線に当てはめることにより、エピタキシャル層のシート抵抗を算出する第2ステップとをこの順序で含むシート抵抗の測定方法。

(もっと読む)

半導体記憶装置の評価方法

【課題】半導体記憶装置のトンネル絶縁膜の電荷分布を評価することが可能な半導体記憶装置の評価方法を提供する。

【解決手段】半導体記憶装置の評価方法は、浮遊ゲート型の半導体記憶装置の評価方法である。時間の対数の変化に対する前記半導体記憶装置のメモリセルの閾値電圧Vtの変化率に、ε*Cr*2k/Tox/qを乗じる。なお、εはトンネル絶縁膜の誘電率であり、Crは前記メモリセルのカップリング比であり、Toxは前記メモリセルのトンネル酸化膜の膜厚であり、kは電荷がデトラップする時の存在確率の減衰率でありk=(2mE/(h/2π)2)0.5と表され、mは電子の質量、 Eは前記トンネル絶縁膜のトラップのエネルギー準位、hはプランク定数、πは円周率である。これにより、前記メモリセルのトンネル絶縁膜中の電子濃度分布を求める。

(もっと読む)

半導体装置の製造方法

【課題】深さが深く幅が狭い溝の深さを把握できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に平面視環状の複数の環状溝2を形成する環状溝形成工程と、環状溝2の下端よりも下層に配置された半導体基板1を介して、複数の環状溝2から選ばれた第1環状溝2aの平面視内側表面と、第1環状溝2aとは別の環状溝2である第2環状溝2bの平面視内側表面との間の抵抗を測定し、実測抵抗値を得る抵抗測定工程と、実測抵抗値を用いて環状溝2の深さを算出する算出工程とを備える半導体装置の製造方法とする。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の設計方法

【課題】TEGパターンより上の層を除去しなくてもTEGパターンを用いた検査を行うことができるようにする。

【解決手段】複数の配線層200,300,400は第1TEGパターン30の上に形成されている。複数の配線層200,300,400には、それぞれ配線242,342,442及び複数のダミーパターン224,324,424が形成されている。電極パッド444は、最上層の配線層400に形成されている。そして平面視において、第1TEGパターン30は、いずれの配線242,342,442及びダミーパターン224,324,424にも重なっていない。

(もっと読む)

プローブカードの検査方法及び検査システム

【課題】短時間で且つ高い信頼性でプローブ針を検査できる検査方法及び検査システムを提供する。

【解決手段】検査システム1は、共通の導電部における複数の被接触領域にそれぞれ複数のプローブ針の先端部を接触させる駆動機構29と、複数のプローブ針22の中からプローブ針の対を複数個構成し、各対をなすプローブ針間に電位差を与えて電気的特性を測定する計測部32Aと、測定された電気的特性に基づいて各プローブ針の良否判定を行う探針検査部32Bとを備える。

(もっと読む)

電子部品の検査方法及び検査装置

【課題】高抵抗性のオープン抵抗の特定を可能とする電子部品の検査方法および検査装置を提供する。

【解決手段】電子部品の検査装置であって、当該検査装置は、電子部品における故障発生が疑われる配線に接続するための電流検出端子106と、電流検出端子106に接続されており、配線に生じた電流を検出する電流検出器105と、電流検出端子106と電流検出器105との間に設けられ、電流を通過させるか否かをゲートの開閉により切り替えるゲーティング装置112と、電子ビームを生成する電子銃101と、電子ビームをパルス化するパルスビーム発生装置111と、パルス化された電子ビームを配線に照射した際に生じた電流を電流検出器105により検出する際に、ゲーティング装置112のゲートの開閉を調整するゲーティング調整装置113とを備える。

(もっと読む)

半導体装置及び半導体チップ

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

DLTS測定用電極及びその製造方法

【課題】測定時において疑似ピークが現れないDLTS測定用電極を提供する。

【解決手段】シリコン基板上に設けられたアンチモンからなるショットキー電極12aと、シリコン基板10の表面10aとショットキー電極12aとの間に設けられたチタンからなる密着膜12bとを備える。本発明によれば、ショットキー電極の材料としてアンチモンを用いていることから、DLTS測定において疑似ピークがほとんど現れず、しかも、測定時におけるリーク電流を抑制することが可能となる。このため、シリコンウェーハに含まれている重金属の種類や濃度を正確且つ高感度に評価することが可能となる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】液晶ドライバ等の半導体集積回路装置においては、その形状が極端に細長いため、長手方向にプロセス特性がばらつくと、所望のデバイス特性が得られない。そこで、実製品ウエハにプロセスモニタ用の検査用素子を各種配置して、それらを測定することによって、プロセス特性のばらつきを監視している。しかし、ウエハ内におけるグローバルなプロセスばらつきは、比較的抽出しやすいものの、チップ内の局所的なプロセスばらつきの高精度の抽出は、大幅に検査用素子密度を上げない限り、困難であることが、本願発明者等により明らかにされた。

【解決手段】本願の一つの発明は、半導体集積回路装置の製造方法において、ウエハ上のチップ領域の近傍に複数のテスト素子領域を異なるピッチで配列し、プローブテストにおいて、それらを電気的に計測することにより、プロセスの局所的ばらつきをモニタするものである。

(もっと読む)

1 - 20 / 101

[ Back to top ]