Fターム[4M112EA18]の内容

Fターム[4M112EA18]に分類される特許

101 - 120 / 571

MEMSマイクロフォンと製造方法

本発明は、二重固体電極を有するMEMSマイクロフォンの改善された製造方法と、改善された性質を有するマイクロフォンを提供する。 (もっと読む)

構造の平面外変位のための停止部を有する可動部を備える微小機械構造およびその製造プロセス

【課題】可動部および固定部が基板上の層の積層体によって形成されたアクティブ構造を備え、であって、可動部および固定部は対向する表面を備え、これらの表面は、システムの適用に応じて、たとえば停止部、検出または作動電極を形成し得るMEMSまたはNEMSシステムの簡略化された製造プロセスを提供する。

【解決手段】基板ならびに基板上に配列された少なくとも2つの層の積層体と、積層体内に形成された可動部および積層体内に形成された基板に対する固定部と、固定部と可動部との間に形成された対向する表面とを備える微小機械構造を製造し、たとえば、積層体に実質的に垂直な方向への可動部の変位を制限する停止手段を形成するプロセスであって、基板と、積層体の材料に対して選択的にエッチングされるのに適した材料からなる積層体との間に少なくとも1つの犠牲層を使用するプロセス。

(もっと読む)

MEMSセンサ及びその製造方法

【課題】 特に、内部配線層への電気的接続性及び内部空間の高さ寸法のばらつきを小さくすることが可能なMEMSセンサ及びその製造方法を提供することを目的としている。

【解決手段】 第1の基板21と、第2の基板22と、前記第1の基板21の表面に形成される第1のSiO2層25と、前記第1の基板21と前記第1のSiO2層25との間に形成される内部配線層24と、前記第1のSiO2層25の表面25aから前記内部配線層24にかけて形成される貫通孔26と、前記貫通孔26内に形成され前記内部配線層24と電気的に接続される電気接続層28と、前記第2の基板22と前記第1のSiO2層25との間に位置し、前記第2の基板22と前記第1の基板21間に形成される内部空間S2の高さ寸法を規制する突出形状の第1の窒化シリコン層33と、を有することを特徴とする。

(もっと読む)

加速度センサの製造方法、1軸加速度センサ

【課題】ピエゾ抵抗素子の形成位置の精度を高め、加速度センサの歩留まりを向上させる。

【解決手段】単結晶シリコンからなる基板の表層に不純物を導入することによってピエゾ抵抗部を形成し、非原型領域のうち、可撓部Fの原型領域の第三端および第四端に隣接し前記第三端と第四端とからそれぞれ一定距離の幅を有する側壁形成領域において、前記基板の表面に、前記基板に対するエッチング選択性を有する側壁14aを形成し、可撓部Fの原型領域および錘部Mの原型領域および枠部Sの原型領域を保護する保護部と、側壁14aとをマスクに用いて前記基板を異方性エッチングすることにより、枠部Sと錘部Mと可撓部Fとを形成するとともに、前記ピエゾ抵抗部からピエゾ抵抗素子P1、P2、P3、P4を形成する。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

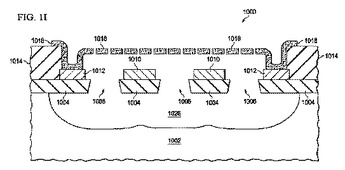

集積回路一体型マイクロホン

集積回路(1000)が、バックサイドキャビティ(1026)が集積回路の基板(1002)内に配置された容量性マイクロホンを含む。基板にエッチャントがアクセスできるように誘電体支持層(1004)を通して基板表面にアクセスホール(1006)を形成することができ、それによってバックサイドキャビティ(1026)が形成される。バックサイドキャビティ(1026)は、容量性マイクロホンの固定プレート(1010)および透過膜(1018)が形成された後で、透過膜およびアクセスホールを通して基板にエッチャントを提供することによってエッチングし得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】慣性センサと半導体電子回路とを有する半導体装置において、慣性センサの感度を向上させる。

【解決手段】第1半導体層、第1絶縁体層及び基板層の順に積層された支持部と、第1半導体層、第1絶縁体層及び基板層の順に積層された可動錘部と、第1半導体層を有し支持部によって可動錘部を支えるための梁部と、梁部に位置する第1半導体層に形成された歪み検出素子と、支持部に位置する第1半導体層及び可動錘部に位置する第1半導体層の少なくともいずれか一方に形成された半導体素子と、を具備する。このように、支持部及び可動錘部が第1半導体層、第1絶縁体層及び基板層を共通に含むので、可動錘部の質量を大きくし、感度の優れた慣性センサを形成することができる。

(もっと読む)

素子構造および素子製造方法

【課題】使用時の電流ばらつきを抑えながら空乏層の接触を防止する素子構造を提供する。

【解決手段】SOI基板の表面(N型層)にP型ドーパントをイオン注入することで、ピエゾ抵抗を形成する。その後、裏面側の支持用基板層のピエゾ抵抗の対向位置をエッチングし、裏面側から全面にN型ドーパントをイオン注入し、N+層を形成する。表面側のN型層基板は、支持用基板層がエッチングされた箇所だけN+層となる。N+層が裏面側の空乏層の広がりを抑止するため、基板の比抵抗を高くしてもピエゾ抵抗の空乏層と接触することがない。例えば、基板の比抵抗を1Ω・cm以上とすれば、ドーパント濃度は1×1016個/cm3以下となり、ピエゾ抵抗のドーパント濃度(例えば1×1018個/cm3)に対して少なくなり、基板の比抵抗のばらつき(1Ω・cm〜10Ω・cm程度)が、ピエゾ抵抗の抵抗値のばらつきに与える影響は非常に小さくなる。

(もっと読む)

半導体圧力センサ及びその製造方法

【課題】製造ばらつきの少ない半導体圧力センサを得る。

【解決手段】シリコン基板10は貫通孔12を有する。シリコン基板10上にポリシリコン膜20が形成されている。ポリシリコン膜20は、貫通孔12の上方にダイヤフラム24を有する。ポリシリコン膜20上に絶縁膜22が形成されている。ピエゾ抵抗効果を有するポリシリコンゲージ抵抗R1,R2,R3,R4が絶縁膜22上に形成されている。ポリシリコン配線W1,W2,W3,W4は、ポリシリコンゲージ抵抗R1,R2,R3,R4をブリッジ状に接続する。ポリシリコンゲージ抵抗R1,R2は、ダイヤフラム24の中央部に配置され、それぞれ並列接続された複数の抵抗を有し、構造及び向きが同じである。

(もっと読む)

加速度センサ

【課題】突起部が固定電極に付着するのを防止することのできる加速度センサを提供する。

【解決手段】凹部41,51と充実部40,50が一体に形成された重り部4,5と、1対のビーム部6a,6b,7a,7bと、可動電極4a,5aと、第1の固定電極20a,21a及び第2の固定電極20b,21bとから成るセンサ部を備え、重り部4,5の固定電極20a,…と対向する側の面と所定の間隔を空けて配置され且つ一面に各固定電極20a,…が設けられる上部固定板2aを有し、各可動電極4a,5aの各固定電極20a,…との対向面には突起部43a,53aが形成され、各固定電極20a,…の突起部43a,53aと対向する部位に、上部固定板2aの前記一面を外部に臨ませるように刳り貫かれた逃がし部20c,…を設けた。

(もっと読む)

半導体圧力センサおよびその製造方法

【課題】半導体圧力センサの製造工程における、貫通穴の形成を抑制し、製造歩留まりの向上を図る。

【解決手段】本発明の半導体圧力センサは、ダイヤフラム部Dを備えた半導体基板3と、前記ダイヤフラム部Dに印加される圧力を抵抗値変化として検出するピエゾ抵抗素子(2a、2b、2c、2d)と、前記ダイヤフラム部表面及び前記ピエゾ抵抗素子表面を含む前記半導体基板表面を覆うアルカリ耐性を持つ第1の絶縁膜8aと、前記第1の絶縁膜の上層に形成され、少なくとも前記第1の絶縁膜の表面を覆う導電性薄膜7と、前記導電性薄膜表面を覆うアルカリ耐性を持つ第2の絶縁膜8bとを具備している。

(もっと読む)

半導体圧力センサ及びその製造方法

【課題】本発明は、半導体圧力センサ及びその製造方法に係り、Si基板の開口部のダイヤフラム側壁すべてをその基板面に対して垂直な面とすることにある。

【解決手段】半導体圧力センサは、単結晶シリコン基板と、前記単結晶シリコン基板を裏面側からエッチングすることによって形成されたダイヤフラム及び4面のダイヤフラム側壁と、前記単結晶シリコン基板の表面側に形成されたリード導体及び歪ゲージ抵抗からなるブリッジ回路と、を備え、前記ダイヤフラムは、面方位が(110)面であり、かつ、平面形状が平行四辺形であり、前記ダイヤフラム側壁は、4面とも面方位が(111)面であり、かつ、2面ずつ互いに平行に向かい合っており、圧力印加に伴う前記ダイヤフラムの撓み量に応じて前記ブリッジ回路の出力値が変動することを利用して、前記ダイヤフラムに印加される被検出対象の圧力を検出する。

(もっと読む)

静電容量型加速度センサ

【課題】小型化を図りつつ高感度化を図れる静電容量型加速度センサを提供する。

【解決手段】フレーム部11、錘部13、一対のトーションビーム12,12、2つの可動電極15,15が設けられたセンサ本体1と、センサ本体1に接合された第1のカバー基板2および第2のカバー基板3と、第1のカバー基板2において各可動電極15,15それぞれに対向して設けられた固定電極25,25とを備えている。各固定電極25,25それぞれが、第1のカバー基板2におけるセンサ本体1側に形成され各固定電極25,25それぞれに対応付けられた接続配線26とセンサ本体1の錘部13の開口窓14内に配置された島部16とを介して当該島部16における第1のカバー基板2側の第1の外部接続用電極であるパッド18と電気的に接続され、各可動電極15,15が第1のカバー基板2側の第2の外部接続用電極であるパッド18,18と電気的に接続されている。

(もっと読む)

半導体圧力センサの製造方法

【課題】基板接合強度及びダイアフラムの耐圧限界を高める半導体圧力センサの製造方法を得る。

【解決手段】半導体基板のキャビティ側の面に、縦横2列で隣接する4つのキャビティの中央にそれぞれ位置させて所定深さの内基準穴を形成してから鏡面加工を施すことによって、その表面高さが最大かつ均一となった接合面を形成する。そして、この接合面を介して半導体基板とベース基板を接合し、これら基板をチップ単位にダイシングして個々の半導体圧力センサを得る。

(もっと読む)

半導体圧力センサの製造方法

【課題】基板接合強度及びダイアフラムの耐圧限界を高める半導体圧力センサの製造方法を得る。

【解決手段】先ず、半導体基板に、圧力感応抵抗素子を形成した面とは反対側の面に位置させて、キャビティを形成する。次に、半導体基板のキャビティ側の面に、基板接合時にベース基板との間に隙間を生じさせる溝をダイシングストリートに沿って形成した後、鏡面加工を施す。この鏡面加工により、半導体基板の厚さがキャビティ側端部及び溝側端部よりも該端部の間に位置する中間部で大きくなる、湾曲形状の接合面を形成する。そして、この湾曲形状の接合面を介して半導体基板とベース基板を接合した後、これら基板をチップ単位にダイシングし、個々の半導体圧力センサを得る。

(もっと読む)

面内ピエゾ抵抗検出センサ

本発明は、一方向(Y1)に沿った向きの変位を測定するための面内MEMS又はNEMS検出デバイスであって、基板に対して懸架された振動質量(202)であって、前記基板の面に垂直な軸(Z)周りに旋回可能な振動質量(202)と、振動質量(202)及び基板に機械的に接続された少なくとも一つのピエゾ抵抗歪みゲージとを備え、ピエゾ歪みゲージ(8)が振動質量の厚さよりも小さな厚さを有し、ピエゾ抵抗歪みゲージ(8)の軸(Y)が、振動質量(202)の旋回軸(Z)及び重心(G)を含む面に直交していて、該面が、測定される方向(Y1)に直交している、面内MEMS又はNEMS検出デバイスに関する。  (もっと読む)

(もっと読む)

圧力センサおよびその製造方法

【課題】圧力センサにおいて2枚の単結晶シリコン基板を張り合わせたものやSOI基板を適用せずに、圧力センサにおいて十分な性能(感度等)を確保すると共に、そのコストをより抑制する。

【解決手段】シリコン基板1の一端面側に形成された酸化膜(またはシリコン窒化膜)2表面に対し膜成長によってポリシリコン膜3が形成される。また、ポリシリコン膜3中には、拡散領域5と、その拡散領域5と接触するようにピエゾ抵抗素子7が形成される。そして、前記シリコン基板1他端面側からエッチングされて形成され前記酸化膜におけるピエゾ抵抗素子7の位置に対して、ダイアフラム101が形成される。

(もっと読む)

物理量センサー、物理量センサーの製造方法、および電子機器

【課題】MEMSセンサーなどの物理量センサー、および、物理量センサーを比較的容易に製造できる物理量センサーの製造方法、および、物理量センサーを備えた電子機器を提供する。

【解決手段】静電容量型加速度センサー100は、固定部としての固定枠部110と、可動錘部120と、固定電極を有する固定電極部(固定腕部)150(150a,150b)と、可動電極を有する少なくとも一つの可動電極部(可動腕部)140(140a,140b)と、を有し、固定電極部150(150a,150b)は、第1積層構造体AISの側面に形成された、固定電極としての第1側面導体膜CQ1(CQ1a,CQ1b)および第1接続電極部L4(L4a,L4b)と、を有し、可動電極部140(140a,140b)は、第2積層構造体層構造体BISの側面に形成された、可動電極としての第2側面導体膜CQ2(CQ2a,CQ2b)および第2接続電極部L5(L5a,L5b)を有する。

(もっと読む)

微小電気機械装置、半導体装置、微小電気機械装置の製造方法、および半導体装置の製造方法

【課題】微小電気機械装置の特性向上および製造工程の簡略化を図る。

【解決手段】微小電気機械装置を、半導体層(1)と、前記半導体層中のチャネル領域の両側に形成されたソース、ドレイン領域(13)と、前記半導体層上に形成されたゲート絶縁膜(19)と、前記ゲート絶縁膜上に形成された空洞(15a)と、前記空洞上に形成されたゲート電極(17)と、を有し、前記ゲート電極は、前記ゲート絶縁膜と接触するよう可動に構成され、前記ゲート電極上に加わる力を、前記ゲート電極と前記ゲート絶縁膜との接触面積により検出するように構成する。このように、上記接触面積によりゲート電極上に加わる力を検出することができる。また、一時的なFET構造を利用することにより、装置および製造工程の簡略化を図ることができる。

(もっと読む)

センサデバイス及びその製造方法

【課題】センサ内部の配線パターンの設計や製造工程を変更せずに、配線パターンを容易に変更可能にするセンサデバイス及びその製造方法を提供する。

【解決手段】センサデバイスは、複数のピエゾ素子231,232と、複数の接続パッド261〜265と、ピエゾ素子231,232と電気的に接続された上層配線240、241と、上層配線240及び241に接続された下層配線251及び252と、下層配線251及び252に対して垂直方向に交差する上層配線242〜244と、上層配線242〜244の下層の下層配線253〜257があり、下層配線253〜257の他端部の上層には、絶縁層を介して接続パッド261〜265が形成される。

(もっと読む)

101 - 120 / 571

[ Back to top ]