Fターム[4M119AA19]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 製造方法の改善 (280)

Fターム[4M119AA19]に分類される特許

161 - 180 / 280

磁気抵抗効果素子の製造方法

【課題】高密度記憶の磁気記憶装置に適用可能で、信頼性の向上が図られた磁気抵抗効果素子を提供する。

【解決手段】磁化方向が実質的に一方向に固着された磁化固着層と、磁化方向が外部磁界に対応して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に設けられた絶縁層と前記絶縁層を貫通する金属層を含むスペーサ層とを有する磁気抵抗効果素子の製造方法において、前記スペーサ層は、第1の金属層を成膜し、前記第1の金属層上に、前記絶縁層に変換される第2の金属層を成膜し、前記第2の金属層を前記絶縁層に変換するとともに前記絶縁層を貫通する前記金属層を形成する第1の変換処理を行い、前記第1の変換処理を通じて形成された前記絶縁層及び前記金属層上に、前記絶縁層に変換される第3の金属層を成膜し、前記第3の金属層を前記絶縁層に変換するとともに前記絶縁層を貫通する前記金属層を形成する第2の変換処理を行って形成する。

(もっと読む)

半導体装置の製造方法

【課題】 簡便で自己整合な方法で形成されたボーダレスコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】 基板上に第1絶縁層を形成する工程と、第1絶縁層の上に素子を形成する工程と、第1絶縁層の上に、素子を覆う第2絶縁層を形成することで、素子の上に第2絶縁層の突出部を形成する工程と、第2絶縁層の上に上面が平坦なレジスト層を形成する工程と、第2絶縁層の突出部が露出するまでレジスト層を削除する工程と、レジスト層をマスクとして素子の上面が露出するまで第2絶縁層をエッチングする工程と、を含み、第2絶縁層及び素子上に配線層を形成する工程を更に備える。

(もっと読む)

複合材の製造方法及び半導体装置の製造方法

【課題】大気中でも安定した複合材を容易に得ることができる複合材の製造方法及び半導体装置の製造方法を提供する。

【解決手段】基体1上に、複数の表面酸化微粒子2を堆積する。表面酸化微粒子2の直径は10nm以下であることが好ましく、例えば0.5nm〜5nm程度である。表面酸化微粒子2は、グラファイト層を形成する際の触媒として機能し得るコバルト等の強磁性体金属微粒子とこの表面を覆う酸化膜から構成されている。次いで、炉内に基体1及び表面酸化微粒子2を挿入し、炉内を高真空にして基体1を510℃程度まで昇温する。この結果、基体1及び表面酸化微粒子2に付着していた異物等が除去される。その後、炉内の雰囲気を炭化水素系ガス雰囲気にする。この結果、表面酸化微粒子2の表面に存在した酸化膜が還元され、更に、強磁性体金属微粒子の表面にグラファイトが析出し、グラファイト被覆微粒子3が強磁性体複合微粒子として得られる。

(もっと読む)

マルチフェロイック電子装置

【課題】 交流磁場で電流を誘起でき、または電気分極の強度と方向を制御できるマルチフェロイック電子装置を提供する。

【解決手段】 マルチフェロイックナノ発電機は、金属電極2に挟まれたマルチフェロイック固体材料1からなる構造を有し、金属電極2に平行に交流磁界5を印加するように配置し、金属電極2間に誘起される電流を利用する。

(もっと読む)

ホイスラー合金を有する積層体、この積層体を用いた磁気抵抗素子、スピントランジスタ及びその製造方法

【課題】 ホイスラー合金が形成される下地層の選択自由度が高く、熱処理温度及び熱処理回数を低減し、ホイスラー合金の高いスピン偏極率を活用できる積層体を提供する。

【解決手段】 MgO層3と接触するように、結晶質のホイスラー合金層1が配置されている。ホイスラー合金層1のMgO層3に対して反対の面側には、非晶質のホイスラー合金層4が配置されている。

(もっと読む)

露光方法、及び半導体装置

【課題】歩留まりを向上させた露光方法、及びその露光方法により形成される半導体装置を提供する。

【解決手段】露光方法は、ハーフトーンマスク30を介して基板を4重極照明で露光することにより、基板に平行な第1方向及び第1方向に直交する第2方向にマトリクス状に配置された複数の柱状部を形成する露光工程を備える。ハーフトーンマスク30は、第1方向に延び且つ第2方向に所定ピッチで配置された第1パターン31と、第2方向に延び且つ第1方向に所定ピッチで配置され、第1パターン31に交差する交差部33をもつように形成された第2パターン32とを備える。

(もっと読む)

電気的反射絶縁スペーサを有するSTRAM

反射絶縁スペーサを有するスピン転移トルクメモリが開示される。スピン転移トルクメモリユニット(30)は、自由磁化層(F6)と、リファレンス磁化層(RL)と、自由磁化層をリファレンス磁化層から分離する電気的絶縁および非磁性トンネリングバリア層(TB)と、電極層(E1,E2)と、電極層および自由磁化層を分離する電気的絶縁および電子的反射層(ER)とを含む。  (もっと読む)

(もっと読む)

補償素子を有するSTRAM

補償素子を有するスピン転移トルクメモリが開示される。スピン転移トルクメモリユニットは、合成反強磁性リファレンス素子と、合成反強磁性補償素子と、合成反強磁性リファレンス素子と合成反強磁性補償素子との間の自由磁化層と、自由磁化層を合成反強磁性リファレンス素子から分離する電気的絶縁および非磁性トンネリングバリア層とを含む。自由磁化層は、1100emu/ccよりも大きな飽和モーメント値を有する。  (もっと読む)

(もっと読む)

非晶質または微結晶質MgOトンネル障壁に用いる優先グレイン成長強磁性シード層

MgOベースの磁気トンネル接合(MTJ)デバイスは、本質的に、強磁性参照層、MgOトンネル障壁層、および強磁性自由層を含む。金属Mgの成膜とその後に続く酸化プロセスまたは反応性スパッタリング法により形成される、MgOトンネル障壁層の微細構造は、僅かながら(001)面直方向組織を有する非晶質または微結晶質である。本発明では、少なくとも強磁性参照層のみが、または強磁性参照および自由層の両方が、トンネル障壁に隣接する結晶質優先グレイン成長(PGGP)シード層を有する2層構造であることが提案されている。この結晶質PGGPシード層は、成膜後アニールの後、MgOトンネル障壁層の結晶化および優先グレイン成長を誘起する。  (もっと読む)

(もっと読む)

磁性材料の加工方法及び磁気ヘッドの製造方法

【課題】主磁極を従来よりも微細にすることができる磁性材料の加工方法を提供する。

【解決手段】基板1の上方に、磁性材料を有する磁性体層31を形成し、磁性体層31の上に、塩化された状態での沸点が磁性材料の塩化物の沸点に比べて高い金属を含むマスク35を形成し、塩素系ガスとの化学反応を含むドライエッチング法によりマスク35から露出している領域の磁性体層31をエッチングする工程により、磁気ヘッドの磁極を形成する工程を含む。

(もっと読む)

磁気抵抗効果素子の製造方法

【課題】真空中で行われるドライエッチングの微細加工の製造工程に特別な変更を加えることなく微細加工時に使用されるマスク材を二重に重ねて積層することで、製造工程中必然的に含まれる酸化過程により保護層の最表層に酸化層が形成されたとしても、MR比の低下を防止し、磁気抵抗効果素子としての性能を高く保持することができる磁気抵抗効果素子の製造方法を提供する。

【解決手段】少なくとも2層の磁性層を含む磁性多層膜からなる磁気抵抗効果素子のドライエッチング方法であって、Taからなる第1のマスクの下層にRu、Rh、Os、Nb、Ir、及びReのいずれか1つである第2のマスクを二重に積層する方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】下部導電層と、MTJ素子を保護する保護膜との密着性を高めた半導体装置を提供する。

【解決手段】この半導体装置90は、半導体基板100の上方に形成された下部電極EB1と、下部電極EB1上の一部に形成され、下部磁性膜6、絶縁膜7、上部磁性膜8および上部電極ET1の順に積層されてなるMTJ素子部と、前記MTJ素子部を被覆する様に下部電極EB1上に形成された保護膜33とを備え、下部電極EB1は、アモルファス化された窒化金属により形成され、保護膜33は、窒素を含有する絶縁膜により形成される。

(もっと読む)

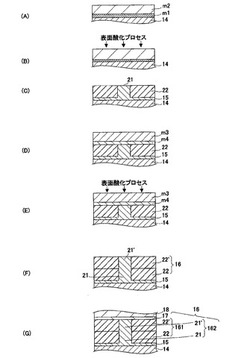

半導体記憶装置の製造方法

【課題】エッチングにより離脱する窒化膜またはCap層の材質を、確実に検出可能な半導体記憶装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、(a)下地層1,2,3,4上にTMR膜5、キャップ層6を順に積層する工程と、(b)TMR膜5、キャップ層6をパターニングして、それらの正規積層構造パターン13およびダミー積層構造パターン16を形成する工程とを備える。そして、(c)正規およびダミー積層構造パターン13,16を覆う窒化膜7を形成する工程と、窒化膜7上に酸化膜8を形成する工程と、(e)酸化膜8および窒化膜7をエッチングして、キャップ層6の上部を露出させる工程とを備える。工程(e)は、エッチングを行いながら、当該エッチングにより離脱した窒化膜7またはキャップ層6の材質を検出する。

(もっと読む)

磁気トンネル接合装置、これを備えるメモリセル、およびその製造方法

【課題】隣接した磁気トンネル接合装置間の干渉現象および電気的な短絡を防止することのできる磁気トンネル接合装置およびその製造方法を提供することである。

【解決手段】所定の間隔を有する複数の開口部を備える絶縁膜を形成するステップと、前記開口部の底面および側壁に第1電極を形成するステップと、前記第1電極上に磁気トンネル接合層を形成するステップと、前記磁気トンネル接合層上に残りの前記開口部を埋め込む第2電極を形成するステップと、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

MRAM及びその改良

【課題】本発明は、磁気抵抗ランダムアクセスメモリ(MRAM)及びその改良に関し、特にMRAM装置における低抵抗セルを容量セルに変換する方法に関する。

【解決手段】MRAM装置における低抵抗セルを容量セルに変換する方法が開示される。低抵抗セルは基板上に複数の層を備える。基板から離れた少なくとも1層は、酸素注入の影響を受けやすい。この方法は、基板から離れた少なくとも1層の表面の少なくとも一部を露出させるために、セルのキャップ層を除去する段階と、セルの周囲に酸素バリアを適用する段階とを含む。前記少なくとも1層は酸化される。酸素バリアは除去される。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑化することなく、配線の信頼性低下を招かない、配線構造を有する半導体装置及びその製造方法を得る。

【解決手段】接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTa/TaN積層バリア層12を介して、NiFe磁性層13をPVD装置のNiFeチャンバを用いたPVD法によって成膜する。次に、同一のPVD装置の同一のNiFeチャンバを用いて、成膜条件を変更することにより、接続孔30及び配線用溝31の底面上及び層間絶縁膜11の表面上におけるNiFe磁性層13を選択的に除去する。さらに、同一のPVD装置のTaチャンバ及びCuチャンバを用いて、接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTaバリア層及びCuシード層を順次形成する。

(もっと読む)

半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有し、容易に製造することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1領域と第2領域を有する半導体基板と、第1領域の半導体基板上方に配置されたMTJと、MTJを覆うように配置され、第2領域上方よりも第1領域上方の膜厚が薄い絶縁膜と、絶縁膜中に配置され、MTJと電気的に接続された導電膜と、第1領域上方の絶縁膜上方に形成され、導電膜と電気的に接続されたビット線と、第2領域上方の絶縁膜上方に形成された配線と、を備える。

(もっと読む)

磁気抵抗素子の製造方法

【課題】 TMR値が高く、RAが低いMTJデバイスを得ること。

【解決手段】 磁気抵抗素子の製造方法は、金属層を第1の厚さに形成する金属層形成ステップと、金属層を不活性ガスのプラズマに晒し、前記第1の厚さよりも小さい第2の厚さにエッチングするプラズマトリートメントを実行するプラズマ処理ステップと、前記プラズマトリートメントを施した金属層を酸化し、トンネルバリアを構成する金属酸化物を形成する酸化ステップと、を有するトンネルバリア形成ステップを有する。

(もっと読む)

半導体装置の製造方法

【課題】MTJ素子の特性を劣化させることなく、良好な絶縁性を有するシリコン窒化膜をMTJ素子の保護膜として形成することができる半導体装置の製造方法を得る。

【解決手段】MTJ素子部(MTJ素子MD1及び上部電極ET1)を含む全面にシリコン窒化膜33を形成する。シリコン窒化膜33の成膜装置として、平行平板型プラズマCVD装置を用いる。そして、成膜ガスとして、NH3を含むことなく、SiH4/N2/ヘリウムガス(He)を用いる。成膜温度は200〜350℃に設定される。さらに、理想的には、Heの流量がSiH4の流量に対し、100〜125倍を呈するようにHeとSiH4の流量比が設定される。

(もっと読む)

161 - 180 / 280

[ Back to top ]