Fターム[4M119AA19]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 製造方法の改善 (280)

Fターム[4M119AA19]に分類される特許

121 - 140 / 280

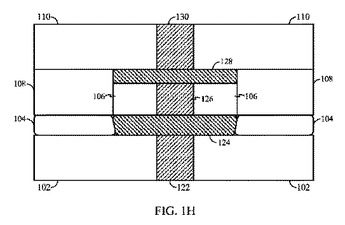

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、配線60と配線65との交点に設けられ、第1及び第2の端部の少なくとも一方にシリサイド層39を有する非オーミック素子30と抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子20とを含むセルユニットCUを具備し、シリサイド層39は、Si元素50とシリサイドを形成する少なくとも1種類の3d遷移金属元素51と、3d遷移金属元素51の原子半径r1より大きい原子半径r2を有する少なくとも1種類の添加元素52とを含む。

(もっと読む)

磁気トンネル接合デバイス

磁気トンネル接合デバイスを製造するおよび使用するシステムおよび方法が開示される。特定の実施形態において、磁気トンネル接合デバイスが、第1自由層と第2自由層とを含む。また、磁気トンネル接合が、スピントルク強化層を含む。磁気トンネル接合が、第1自由層と第2自由層との間にスペーサー層をさらに含み、前記スペーサー層が、1つの材料を含み、第1自由層と第2自由層との間の交換結合を実質的に抑制する厚さを有する。第1自由層と第2自由層とが、静磁的に結合される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】3次元積層デバイスの歩留まりの向上を図れるリソグラフィ工程を含む半導体装置の製造方法を提供すること。

【解決手段】複数の層を基板上に積層してなる3次元積層デバイスであって、前記複数の層の各々がデバイス回路が含まれたデバイス構造を具備してなる半導体装置の製造方法であって、前記複数の層のリソグラフィ工程に使用され、前記デバイス回路に対応するパターンが互いに同じであり、前記原版の欠陥に基づいた品質、前記原版の前記基板への転写性に基づいた品質、または、前記原版の使用回数に関しての品質が順位付けされた複数の原版のうち、一定以上の品質を有する原版を、下層のリソグラフィ工程に使用し、前記複数の原版のうち、前記一定以上の品質を有する原版を除いた原版を、上層のリソグラフィ工程に使用することを特徴とする。

(もっと読む)

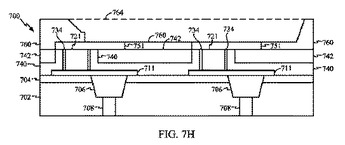

磁気トンネル接合デバイス及び製造

磁気トンネル接合(MTJ)デバイス及び製造方法が開示される。特定の実施形態では、底部電極(110、702)の上方に磁気トンネル接合構造(202)を形成することを含む方法が開示される。また、本方法は、磁気トンネル接合構造の上方及びこれに隣接する拡散障壁層(302、402)を形成することも含む。本方法は、拡散障壁層をエッチングバックして、磁気トンネル接合構造の上方の拡散障壁層を除去することを更に含む。また、本方法は、磁気トンネル接合構造の頂部 を導電層(604、704)に接続することも含む。  (もっと読む)

(もっと読む)

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

半導体素子のパターン構造物形成方法

【課題】磁性物質又は相変化物質を含む半導体素子のパターン構造物の形成方法を提供する。

【解決手段】基板上に、磁性物質又は少なくとも3つの元素を含む合金からなった相変化物質のいずれか一つの物質を含むエッチング対象膜を形成する段階と、少なくともアンモニア(NH3)ガスを含むエッチングガスを使って前記エッチング対象膜をプラズマ反応性エッチングすることによってパターン構造物を形成する段階とを有する。

(もっと読む)

基板処理装置および半導体装置の製造方法

【課題】ターゲットの角度を調整可能な基板処理装置を提供する。

【解決手段】基板処理装置は、イオンを発生させるイオン源と、該イオン源が発射したイオンビームが照射されるターゲットと、該ターゲットを保持するターゲットホルダと、前記ターゲットからはじき出されたターゲット成分粒子が堆積する位置で基板を保持する基板ホルダと、前記ターゲットの前記イオンビームに対する角度を調整する角度調整部と、を有している。ターゲットホルダに保持されたターゲットの角度を角度調整部により調整し、イオン源が発射したイオンビームを前記ターゲットに照射させて前記ターゲットからはじき出されたターゲット成分を基板ホルダに保持された基板に堆積させる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】消費電力を抑制することにより特性を向上させる不揮発性メモリおよび不揮発性メモリの製造方法を提供する。

【解決手段】第1の配線10と第2の配線11とに接続された記憶セル80aを備え、前記記憶セル80aは、複数の層を有し、前記複数の層は、記憶層である抵抗変化膜24と、前記記憶層に接し複数のカーボンナノチューブ23cを含むカーボンナノチューブ含有層23とを有し、カーボンナノチューブ23cが抵抗変化膜24の電極として機能する。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供する。

【解決手段】第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層された積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を順次形成し、次いで、第2磁性材料層53上にマスク層63を形成した後、マスク層63で覆われていない第2磁性材料層53の部分53’を酸化し、次いで、酸化された第2磁性材料層53の部分53’を還元する工程を備えている。

(もっと読む)

磁性媒体の製造法及びスパッタリング装置

【課題】量産時、TMR素子を用いたMARMの完成品間で、MRAMのメモリー特性にバラツキがあり、不良品発生頻度が高かった。このバラツキは、量産時のTMR素子のMR比がウエハー製品間で一定値に維持されず、変動していたことが原因していたので、バラツキを抑制する製造方法を提供する。

【解決手段】高周波成分カットフィルターにより高周波成分をカットした直流電力印加の下で、強磁性体ターゲットをDCスパッタリングすることによってアモルファス状態の強磁性体膜を成膜し、そして酸化マグネシウムターゲットを高周波スパッタリングすることによって結晶酸化マグネシウム膜を成膜する工程及び該工程を実行する制御プログラムを備えた成膜スパッタリング装置200。

(もっと読む)

磁気抵抗メモリ及びその製造方法

【課題】特性の向上、製造コストの低減を可能とする磁気抵抗メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗メモリは、半導体基板30上に設けられる選択トランジスタ2と、選択トランジスタ2の拡散層23,24上にそれぞれ設けられるコンタクトプラグ50A,50Bと、コンタクトプラグ50Aに電気的に接続される下部電極10と、下部電極10上に設けられる磁気抵抗効果素子1と、磁気抵抗効果素子1上に設けられる上部電極19と、を具備し、下部電極10は、その底面の寸法が上面の寸法より長いテーパー状の断面形状を有し、下部電極10の一端が、コンタクトプラグ50A上面に接触し、磁気抵抗効果素子1は、コンタクトプラグ50Aの直上から半導体基板表面に対して平行方向にずれた位置に設けられている。

(もっと読む)

半導体装置

【課題】MTJメモリセルを有するMRAMデバイスにおいて、データ読出動作の高速化および、配線層数の減少による製造コスト低減を図る。

【解決手段】MTJメモリセルは、記憶データのデータレベルに応じて抵抗値が変化する磁気トンネル接合部MTJと、アクセストランジスタATRとを備える。アクセストランジスタATRのゲートはリードワード線RWLと結合される。ビット線BLは、磁気トンネル接合部MTJと直接結合されず、アクセストランジスタATRを介して磁気トンネル接合部MTJと電気的に結合される。磁気トンネル接合部MTJは、ライトワード線WWLおよびアクセストランジスタATRの間に結合される。データ読出時において、ライトワード線WWLの電圧は接地電圧Vssに設定されて、データ読出のための電流経路が形成される。さらに、ライトワード線WWLは、ビット線BLよりも上層側に形成される。

(もっと読む)

磁性媒体の製造法及び成膜装置

【課題】量産時、TMR素子を用いたMRAMの完成品間で、MRAMのメモリー特性にバラツキあり、不良品発生頻度が高かった。このバラツキは、量産時のTMR素子のMR比がウエハー製品間で一定値に維持されず、変動していたことが原因していたので、バラツキを抑制する製造方法及び製造装置を提供する。

【解決手段】低周波成分カットフィルターにより低周波成分をカットした高周波電力印加の下で、酸化マグネシウムを有するターゲットをスパッタリングすることによって酸化マグネシウムの薄膜結晶膜122を成膜し、そして磁性金属(好ましくは強磁性体)のターゲットをスパッタリングすることによって磁性金属薄膜123を成膜する工程及び該工程を実行する制御プログラムを備えた成膜スパッタリング装置。

(もっと読む)

磁性素子の製造法及び記憶媒体

【課題】磁性体層又は反磁性体層をエッチングする際のパーティクルの混入を抑制し、高性能なTMR素子を提供する。

【解決手段】炭化水素類ガス、アルコール類ガス、エーテル類ガス、アルデヒド類ガス、カルボン酸類ガス、エステル類ガス及びジオン類ガスからなる化合物ガス群から選択された少なくとも一種の化合物ガス、及び酸素ガスを有する混合ガス中の全炭素原子数Cnと全酸素原子数OnとがOn/Cn>1の関係を満たし、該混合ガスを用いて形成したプラズマ雰囲気下で、磁性体層又は反磁性体層をエッチングする。

(もっと読む)

磁性素子の製造法及び記憶媒体

【課題】磁性膜又は反磁性膜をエッチングする際に発生するパーティクルの混入を抑制し、高性能なTMR素子を製造する方法を提供する。

【解決手段】炭化水素類、アルコール類、エーテル類、アルデヒド類、カルボン酸類、エステル類及びジオン類からなるガス化化合物群から選択された少なくとも一種のガス化化合物を0.5×1017分子数/分・m2以上、好ましくは2×1017分子数/分・m2以上の分子流速の条件下において形成したプラズマ雰囲気下で、磁性膜又は反磁性膜をエッチングする。

(もっと読む)

磁気素子の製造方法と装置

【課題】エッチング損傷を減少させるべくドライエッチングを用いて磁気素子を製造する。

【解決手段】磁気素子の製造方法と装置を提供する。素子の磁性及び/又は非磁性層はTaのような非有機材マスクを用いN2のような不活性ガスと水素ガスの混合ガスによりエッチングされる。結果として、研究例ではMTJテーパ角はほぼ垂直である。

(もっと読む)

スピントロニック素子のスピンバルブ構造およびその形成方法、ボトム型スピンバルブ構造、ならびにマイクロ波アシスト磁気記録用スピントロニック素子

【課題】スピン消極を引き起こすことなく、また、加熱処理を必要とせずに、[Co/Ni]x積層構造の十分な垂直磁気異方性を確保する。

【解決手段】このスピンバルブ構造は、上部の[Co/Ni]x積層リファレンス層23の垂直磁気異方性を向上させるため、Ta層と、fcc[111]またはhcp[001]構造を有する金属層とを含む複合シード層22を備える。[Co/Ni]x積層リファレンス層23は、CoとNiとの界面の損傷を防止し、これにより垂直磁気異方性を保つため、低いパワーと高圧のアルゴンガスとを用いたプロセスにより成膜する。その結果、薄いシード層を用いることが可能となる。垂直磁気異方性は220℃の温度で10時間にわたって熱処理を行った後であっても維持される。この構造は、CPP−GMR素子やCPP−TMR素子に適用できるほか、スピントランスファー発振器やスピントランスファーMRAMにも適用できる。

(もっと読む)

121 - 140 / 280

[ Back to top ]