Fターム[4M119AA19]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 製造方法の改善 (280)

Fターム[4M119AA19]に分類される特許

261 - 280 / 280

磁気記憶装置の製造方法

【課題】磁気抵抗効果素子を含むメモリセルのサイズを縮小する。

【解決手段】磁気記憶装置の製造方法は、コンタクトプラグ13および第1の絶縁層11上に、磁気抵抗効果素子10を形成する工程と、上部電極層16上に、第1の方向に延在する第1のマスク層18を形成する工程と、上部電極層16を第1のマスク層18を用いてエッチングする工程と、上部電極層16および非磁性層15上に保護膜20を形成する工程と、保護膜20上に第2のマスク層21を形成する工程と、第2の方向に延在するように、第2のマスク層21上にレジスト層22を形成する工程と、第2のマスク層21をレジスト層22を用いてエッチングし、上部電極層16の側部に側壁部21Aを形成する工程と、非磁性層15および下部電極層14を、第2のマスク層21および側壁部21Aを用いてエッチングする工程とを含む。

(もっと読む)

トンネルバリア層の形成方法、ならびにTMRセンサおよびその製造方法

【課題】 膜厚と酸化状態の均一性が改善されたトンネルバリア層の形成方法、ならびにそのようなトンネルバリア層を備えたTMRセンサおよびその製造方法を提供する。

【解決手段】 TMRセンサのトンネルバリア層28を、下部Mg層25/MgO層26/上部Mg層27という3層積層構造にする。MgO層26は、下部Mg層25の表面を自然酸化させて形成する。このため、膜厚と酸化状態の均一性が改善される。また、上部Mg層27を追加したことで、隣接するフリー層29の酸化を防止できる。AlOX からなるトンネルバリア層を備えた従来のTMRセンサと比べて、低いRA値であっても高いMR比が得られる。

(もっと読む)

磁気トンネル接合の封入方法、磁気デバイスの形成方法、および磁気トンネル接合構造

【課題】 トンネル抵抗値の増加やMTJ破壊電圧の低下を伴うことなく熱処理に晒すことができる磁気トンネル接合構造、これを実現し得る磁気トンネル接合の封入方法、およびそれを備えた磁気デバイスの形成方法を提供する。

【解決手段】

反強磁性層12、ピンド層13、絶縁トンネル層14、フリー層15およびキャップ層16を順次積層したのち、素子領域以外の領域をイオンミリング等によって選択エッチングし、MTJ積層構造を得る。次に、無酸素雰囲気中で第1の封入層31を成膜したのち、酸素雰囲気中で第2の封入層32を成膜する。追加埋込酸素を含まない封入層31と酸素リッチな第2の封入層とを二重に積層してMTJ積層構造を封じ込めることにより、外部からMTJ接合を確実に絶縁分離できると共に、後工程で熱処理プロセスに曝されてもトンネル抵抗値の安定性が確保される。

(もっと読む)

磁気メモリセルおよびその製造方法

【課題】 ショートの発生を防止可能なMTJ積層構造を有する磁気メモリセルおよびその製造方法を提供する。

【解決手段】 CMPプロセスに先立つシリコン酸化物層53の形成前に、MTJ積層構造20の上に、シリコン窒化物層またはシリコン酸化窒化物層等の保護層52を別途形成する。その後、CMPプロセスにより全面を平坦化研磨してMTJ積層構造20領域以外のシリコン酸化物層53を選択的に除去した後、エッチングにより、MTJ積層構造20の真上にある保護層52を選択的に除去する。MTJショートが少なく、しかも、ビット線とフリー層との距離が制御されたMRAMセル構造を得ることができる。さらに、従来に比べて耐熱性に優れたMRAMセル構造を得ることもできる。さらに、製造工程において、CMPプロセスのマージンが大きくなるので、製造が容易となる。

(もっと読む)

MSM電流制限素子および抵抗メモリ素子、ならびにその製造方法および操作方法

【課題】MSM電流制限素子、およびMSM電流制限素子を有する抵抗メモリセルを製造することができる製造方法を提供する。

【解決手段】基板を用意する工程と、基板上にMSM下部電極を形成する工程と、MSM下部電極上に、xが約1以上約2以下の範囲内であるZnOx半導体層を形成する工程と、ZnOx半導体層上にMSM上部電極を形成する工程とを有している。このZnOx半導体層を、スピンコート法、DCスパッタリング法、RFスパッタリング法、有機金属気相成長法(MOCVD)または原子層堆積法(ALD)のような様々な薄膜形成技術を用いて形成する。

(もっと読む)

磁気デバイスおよびその形成方法

【課題】磁気デバイスを形成する技術を提供する。

【解決手段】一態様では、磁気デバイスに対して自己整合されるビア・ホールを形成する方法が、以下のステップを含む。磁気デバイスの少なくとも一部分の上に誘電体層が形成される。誘電体層は、磁気デバイスに最も近接して、第1材料を含む下層を有し、下層に対して、磁気デバイスとは反対側の面に、第2材料を含む上層を有するように構成されている。第1材料と第2材料とは異なるものである。第1エッチング段階では、第1エッチャントを使用して、上層から開始し上層を貫通して誘電体層をエッチングする。第2エッチング段階では、下層のエッチングに対して選択的な第2エッチャントを使用して、下層を貫通して誘電体層をエッチングする。

(もっと読む)

磁気抵抗素子

【課題】特別な参照要素を用いずに済む磁気抵抗要素の組を提供する。

【解決手段】本素子は、2つの磁気抵抗要素10,20を備えており、これらの要素は、これらの要素10,20の間を通る磁束が当該要素10,20の軟強磁性層26,27を通って閉じるように、互いに静磁相互作用を及ぼし合う状態に置かれている。書き込み素子15は、各軟強磁性層26,27の磁化を制御するために、要素10,20に組み合わされている。読み出し導体線11,12,13,14は、対応する磁気抵抗を測定することによって軟強磁性層26,27の磁気状態を検出するために、各磁気抵抗要素10,20に組み合わされている。要素10,20の軟強磁性層26,27は、互いに実質的に反平行に方向付けられたままである一方、当該要素10,20の硬強磁性層24は、実質的に平行に方向付けられている。

(もっと読む)

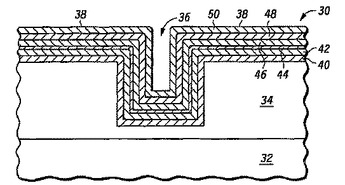

MRAMデバイス用スロット・バイア・ビット線を形成するための方法および構造

【課題】従来の磁気ランダム・アクセス・メモリ(MRAM)デバイスの欠点および欠陥を解消すること。

【解決手段】MRAMデバイスは、下部配線レベルの上に形成された磁気トンネル接合(MTJ)スタック、MTJスタックの上に形成されたハードマスク、およびハードマスクの上に形成された上部配線レベルを含む。上部配線レベルは、その中に形成されたスロット・バイア・ビット線を含み、スロット・バイア・ビット線はハードマスクと接触しており、さらにハードマスクの側壁を部分的に包囲するエッチ停止層と接触している。

(もっと読む)

単結晶エピタキシャル酸化膜の歪制御方法

【課題】 単結晶エピタキシャル酸化物の歪を制御する方法を提供する。

【解決手段】 単結晶エピタキシャル酸化物の歪を制御する方法は、シリコン基板を準備する工程と、Si1−xGex及びSi1−yCyから成るシリコン合金層のグループから選択されるシリコン合金層をシリコン基板上に形成する工程と、シリコン合金層の歪の型を選択し調節するために合金材料の含有量を選択することによってシリコン合金層の格子定数を調節する工程と、ペロブスカイト型マンガン酸化物、単結晶希土類酸化物、マンガンを含まないペロブスカイト型酸化物、2価の希土類酸化物、及び3価の希土類酸化物から成る酸化膜のグループから選択される単結晶エピタキシャル酸化膜を原子層堆積法でシリコン合金層上に堆積させる工程と、所望のデバイスを完成させる工程とを有する。

(もっと読む)

MRAM埋め込みスマートパワー集積回路

集積回路デバイス(300)は、同じ製造プロセス技術を使用して同じ基板上に、MRAMアーキテクチャ及びスマートパワー集積回路アーキテクチャを含む。製造プロセス技術は、フロントエンドプロセス及びバックエンドプロセスを備えたモジュラープロセスである。実施形態では、スマートパワーアーキテクチャは、パワー回路コンポーネント(304)と、デジタルロジックコンポーネント(306)と、フロントエンドプロセスによって形成されたアナログ制御コンポーネント(312)と、バックエンドプロセスによって形成されたセンサアーキテクチャ(308)とを有する。MRAMアーキテクチャ(310)は、フロントエンドプロセスによって形成されたMRAM回路コンポーネント(314)と、バックエンドプロセスによって形成されたMRAMセルアレイ(310)とを有する。ある特定の実施形態では、センサアーキテクチャ(308)は、MRAMセルアレイ(316)によって利用される同じ磁気トンネル接合コアから形成されるセンサコンポーネントを含む。  (もっと読む)

(もっと読む)

インダクタおよび変圧器デバイスをMRAM内に3次元的に埋め込んだ集積回路

集積回路デバイス(300)は、同じ作製プロセス技術を使用して同じ基板上に形成された、磁気ランダムアクセスメモリ(「MRAM」)アーキテクチャ(310)および少なくとも1つのインダクタンス素子(312,314)を含む。インダクタまたは変圧器であってよいインダクタンス素子は、MRAMアーキテクチャのプログラム線として同じ1つの金属層(または、複数の金属層)に形成される。プログラム線層に加えて、利用可能な任意の金属層は、その効率を向上させるためにインダクタンス素子に添加されることができる。MRAMアーキテクチャ(310)とインダクタンス素子(312,314)の同時作製は、基板のアクティブ回路ブロック上で利用可能な物理的空間の効率的でかつ費用効果的な使用を容易にし、3次元集積化をもたらす。  (もっと読む)

(もっと読む)

MRAMデバイスの磁気エレクトロニクス素子を覆う導電層への接触方法

誘電領域を覆う記憶素子層を形成する工程を含む磁気エレクトロニクス素子を覆う導電層への接触方法。第1導電層(26)が記憶素子層(18)を覆うように成長する。第1誘電層(28)が第1導電層(26)を覆うように成長し、第1マスキング層(28)を形成するためにパターン化およびエッチング処理される。第1マスキング層(28)を用いて第1導電層(26)がエッチング処理される。第2誘電層(36)が第1マスキング層(28)及び誘電領域を覆うように成長する。第1マスキング層(28)を露出させるために第2誘電層(36)の一部が除去される。第1マスキング層(28)が第2誘電層(36)に比べて早い速度でエッチング処理されるように、第2誘電層(36)及び第1マスキング層(28)が化学エッチング処理される。このエッチング処理により第1導電層(26)が露出する。  (もっと読む)

(もっと読む)

磁気抵抗ランダムアクセスメモリ装置及びその製造方法

MRAM装置(10)の製造方法では、第1及び第2トランジスタ(14)を上部に備える基板(12)が提供される。動作メモリ素子デバイス(60)が、第1トランジスタ(14)と電気的に接するように形成される。仮想メモリ素子デバイス(58)の少なくとも一部が、第2トランジスタ(14)と電気的に接触するように形成される。第1誘電体層(62)が、仮想メモリ素子デバイスの少なくとも一部と動作メモリ素子デバイスとを覆うように蒸着される。その第1誘電体層がエッチングされて、仮想メモリ素子デバイス(58)の少なくとも一部に対する第1ビア(66)と、動作メモリ素子デバイス(60)に対する第2ビア(64)とが同時に形成される。そして、導電配線層(68)が、仮想メモリ素子デバイス(58)の少なくとも一部から動作メモリ素子デバイス(64)に向かって延びるように蒸着される。  (もっと読む)

(もっと読む)

磁気抵抗ランダムアクセスメモリデバイス構造とその製造方法

バリア層を材料除去停止層として用いる磁気電子メモリ素子構造とその構造の製造方法が提供されている。本方法は、誘電材料層(24)内に少なくとも部分的に堆積されたディジット線(26)を形成するステップを備える。誘電材料層は、相互接続スタック上に設けられる。第1部分(40)及び第2部分(42)を有する導電性バリア層(40,42)が堆積される。第1部分は、ディジット線上に設けられ、第2部分は、空隙内に配置されると共に相互接続スタックに対し電気的に接続される。メモリ素子層(46)が第1部分上に形成され、電極層(48)がメモリ素子層上に堆積される。その後、電極層及びメモリ素子層はパターン化及びエッチングされる。  (もっと読む)

(もっと読む)

ストップ−オン−アルミニウム処理を含むウェーハ処理のためのシステム及び方法

磁気トンネル接合(MTJ)デバイスは、上側磁性層のプラズマ・オーバーエッチング中トンネル接合層が停止層として機能するストップ−オン−アルミナプロセスによって作製することができる。結果として得られたMTJデバイスの側壁は、上側磁性層を下側磁性層から電気絶縁するように機能するトンネル接合層の近傍で非垂直である。プラズマ・オーバーエッチング中に使用されるガスは、ハロゲン含有化学種を含まず、これによりアルミナ・トンネル障壁層に比べて、高度に選択性のある磁性層のエッチングを提供する。ガス内に酸素を導入することで、オーバーエッチングの再現性を高めることができる。最後に、作製プロセス中のフォトレジストの除去に続いて、He及びH2を用いてプラズマ処理した後に洗浄及び焼成することにより収率が高くなる。 (もっと読む)

高感度磁気内蔵電流センサ

電流を非接触検出するためのセンサは、磁気トンネル接合(MTJ)を有するセンサ素子と検出回路とを有しており、センサ素子は磁場に伴って変化する抵抗を有し、また、検出回路は、トンネル接合を通じて流れるトンネル電流を検出するようになっている。センサ素子は、MTJ積層体をメモリ素子と共有していても良い。また、センサ素子は、MRAM技術を含む次世代のCMOSプロセスと容易に統合することができ、よりコンパクトであるとともに、電力消費が少ない。磁束集結体を設けるなどのセンサの感度を高めるための解決策、および、L形状導体素子を形成するなどの同じ電流を用いて高い磁場を生成するための解決策が与えられる。感度が高いため、後処理をあまり使用せずに済み、モバイル機器等の用途においては電力を節約することができる。用途としては、電流センサ、内蔵電流センサ、IDDQおよびIDDT試験を挙げることができ、次世代CMOSプロセスにおいても使用できる。  (もっと読む)

(もっと読む)

磁気メモリ用のデータ保持インジケータ

本発明は、少なくとも1つのデータ保持インジケータデバイス(50)が設けられた磁気抵抗メモリ素子(10)のアレイ(20)を提供する。少なくとも1つのデータ保持インジケータデバイス(50)は、それぞれプリセットされた磁化方向を有する第1の磁気素子(51)と、第2の磁気素子(52)とを備え、第1および第2の磁気素子(51,52)のプリセットされた磁化方向は、互いに異なっている。第1および第2の磁気素子(51,52)は、これらの磁化方向を、検出しきい値を超える外部から印加された磁界の磁界線と向きを揃えるのに適している。本発明によれば、少なくとも1つのデータ保持インジケータデバイス(50)のパラメータが、検出されるべき外部から印加された磁界の検出しきい値を設定するように選択される。少なくとも1つのデータ保持インジケータデバイス(50)は、アレイ(20)の磁気抵抗メモリ素子(10)の前記外部から印加された磁界への暴露を示す状態または出力を有する。  (もっと読む)

(もっと読む)

加工物上にニッケル鉄を無電解析出させるための組成物及びその析出方法

加工物30上にニッケル鉄を無電解析出させる方法及びその組成物を提供する。加工物30上にニッケル鉄を無電解析出させる際に用いられる析出液は、ニッケルイオン源、第一鉄源、錯化剤、還元剤及びpH調節剤を含む。その析出液は、アルカリ金属イオンを実質的には含まない。磁気エレクトロニクス装置で使用されるフラックス集中システムの作製方法は、加工物30を提供するステップと、加工物30上に絶縁材料層34を形成するステップとによって開始される。溝36が絶縁層34に形成され、バリア層40が溝内に析出される。ニッケル鉄クラッド層46がバリア層40上に析出される。ニッケル鉄クラッド層の析出後、溝付近の絶縁材料層34は、原子約1×1011個/cm2未満のアルカリ金属イオン濃度を有する。  (もっと読む)

(もっと読む)

MRAMセルのための磁気異方性を誘導するための斜め堆積

表面を有する基板を提供するステップと、前記基板上に合成磁気モーメントベクトルを有する第1磁気領域(17)を堆積するステップと、前記第1磁気領域上に電気絶縁材料(16)を堆積するステップと、前記電気絶縁材料上に第2磁気領域(115)を堆積するステップを備えた磁気抵抗トンネル接合セルを製造する方法であって、前記第1磁気領域および第2磁気領域の一方の少なくとも一部分が、前記基板の表面に直交する方向に対して非ゼロの堆積角で該領域を堆積することによって形成されて誘導異方性を作る方法。  (もっと読む)

(もっと読む)

レーザ移動を用いて感熱基板上に移植した磁気ランダム・アクセス・メモリ(MRAM)デバイスおよびこれを製造する方法

【課題】 ポリマおよびプラスチック等の低温基板上に磁気メモリ・デバイスを製造する方法を提供する。

【解決手段】 低温基板上に磁気メモリ・デバイス(およびその結果として生じる構造)を形成する方法は、メモリ・デバイスを、分解可能な材料層で被覆された透明基板上に形成し、所定の高圧を生成させる急速加熱を施すステップと、メモリ・デバイスを低温基板に移動するステップと、を含む。

(もっと読む)

261 - 280 / 280

[ Back to top ]