Fターム[4M119GG08]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | コンタクトレイアウト (69)

Fターム[4M119GG08]に分類される特許

1 - 20 / 69

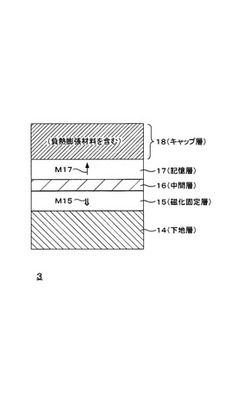

記憶素子、記憶装置

【課題】環境温度によらず、熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、記憶層は正の磁歪定数を持つ磁性層を有するようにし、上記層構造に加えてさらに、負熱膨張材料層が設けられるようにする。

(もっと読む)

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気記憶装置及び磁気記憶装置の製造方法

【課題】 基準素子の抵抗値のばらつきを抑制することが望まれている。

【解決手段】 基板上に磁気抵抗素子及び基準素子が形成されている。磁気抵抗素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、自由磁化層の磁化方向によって低抵抗状態と高抵抗状態との間で抵抗が変化し、第1の方向に長い平面形状を有する。基準素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、磁気抵抗素子の低抵抗状態の抵抗と高抵抗状態の抵抗との間の抵抗を有し、第1の方向と直交する第2の方向に長い平面形状を有する。

(もっと読む)

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、異方性エネルギーを大きくし、微細化しても十分な熱揺らぎ耐性を有するようにする。

【解決手段】記憶素子は、膜面に対して垂直な磁化を有し、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる、膜面に対して垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とにより、MTJ構造を持つ。これに加え、記憶層に隣接する、Cr、Ru、W、Si、Mnの少なくとも一つからなる保磁力強化層と、保磁力強化層に隣接する酸化物によるスピンバリア層を設ける。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

記憶素子及び記憶装置

【課題】書込電流を増大させることなく、高い保持力を有し熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層と、記憶層に隣接し中間層と反対側に設けられるキャップ層と、キャップ層に隣接し記憶層と反対側に設けられる金属キャップ層を有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。そして中間層とキャップ層は酸化物であり、金属キャップ層はPdもしくはPtで構成されているものとする。

(もっと読む)

半導体記憶装置

【課題】セルトランジスタの電流駆動能力の劣化を抑制し、メモリセルごとの信号のばらつきを抑制し、かつ、微細化された半導体記憶装置を提供する。

【解決手段】メモリは、MTJを備える。アクティブエリアは、セルトランジスタごとに分離されており、セルトランジスタのゲートの延伸方向に対してほぼ直交する第1の方向に延伸している。アクティブエリアは、第1の方向に配列されてアクティブエリア列を構成している。第2の方向に隣接する2つのアクティブエリア列は、第1の方向に半ピッチずつずれて配置されている。アクティブエリアの表面上方から見たときに、MTJは各アクティブエリアの一端に重複するように配置されている。第1および第2の配線は、互いに隣接するアクティブエリア列のMTJに交互に重複するように第1および第2の方向に対して傾斜する方向に折り返しながら延伸している。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

磁気記憶素子、磁気記憶装置、磁壁移動方法

【課題】磁性体中の磁壁を安定して移動させる磁気記憶素子、および磁壁移動方法を提供する。

【解決手段】実施形態による磁気記憶素子は、第1電極11と、第2電極12と、前記第1電極11と前記第2電極12との間に設けられ、複数の第1磁性層141および、この第1磁性層141の間に設けられ、第1磁性層141とは構成元素の組成が異なる第2磁性層142を含む積層構造と、前記第1電極11の前記積層構造側の面の反対の面に設けられる圧電体15と、前記圧電体15の前記第1電極11が設けられる位置と異なる位置に設けられ、前記圧電体15に電圧を印加する第3電極13を有する。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

半導体装置

【課題】メモリセルの平面視における面積を増加せずに、磁気抵抗素子の情報の読み書きに用いる電流値を低減しながら、読み書きエラーや磁気抵抗素子間の短絡が抑制された集積回路を有する半導体装置を提供する。

【解決手段】半導体基板の主表面上に配置された、電流の流れる向きに応じて磁化状態を変化させることが可能な、スピントルク書き込み方式の面内磁化型の磁気抵抗素子MRDと、磁気抵抗素子MRDと電気的に接続され、主表面に沿った方向に向けて延びる第1配線BLとを備える。上記磁気抵抗素子MRDは平面視におけるアスペクト比が1以外の値である。上記磁気抵抗素子MRDとスイッチング素子とが電気的に接続されたメモリセルMCが複数並んだメモリセル領域において、平面視における磁気抵抗素子MRDの長手方向に関して、隣接する複数の磁気抵抗素子MRDが、上記長手方向に沿って延在する同一直線上に乗らないように配置される。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

1 - 20 / 69

[ Back to top ]