Fターム[4M119KK02]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | 半導体素子との混載技術 (194) | メモリセル部と周辺回路部との関係 (70)

Fターム[4M119KK02]の下位に属するFターム

メモリセル部及び周辺回路部の同時形成 (28)

Fターム[4M119KK02]に分類される特許

1 - 20 / 42

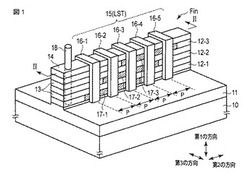

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体記憶装置

【課題】参照セルにおける誤書き込みの発生を抑制し、より高精度にデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置100の参照セルは、第3のビット線BL3に一端が接続され且つ第2のワード線RWLにゲートが接続された第3の選択トランジスタTr3と、第3の選択トランジスタの他端に一端が接続され且つ第3の電圧端子G3に他端が接続された第3の抵抗変化素子R3とを有する第3のメモリセルM3と、第4のビット線BL4に一端が接続された第4の抵抗変化素子R4と、第4の抵抗変化素子の他端と第4の電圧端子G4との間に接続され且つ第2のワード線RWLにゲートが接続された第4の選択トランジスタTr4とを有する第4のメモリセルM4から構成される。さらに第3のビット線BL3と前記第4のビット線BL4との間に接続され、読み出し動作時に電位とを等価にするための第1の電位制御回路Ti1を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】生産コストを抑えながら高いスループットが得られる半導体装置の製造方法と半導体装置とを提供する。

【解決手段】ヨークカバーとなる積層膜として、バリアメタル層、磁性体層およびバリアメタル層が順次形成される。次に、積層膜MLに、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理、一酸化炭素(CO)、アンモニア(NH3)ガスおよびアルゴン(Ar)ガスの混合ガスによる反応性イオンエッチング処理、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理を施すことにより、ヨークカバーYCが形成される。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリセルの読み出しディスターブを防ぎ、大電流で高速に読み出す。

【解決手段】 複数のワード線WLと、複数のビット線BLと、複数のメモリセルMCと、選択されたメモリセルから情報を読み出す読み出し回路SA,LAと、読み出し回路SA,LAが読み出した情報に基づいて、選択されたメモリセルに書き換えを行う書き換え回路WD1,WD2とを有し、読み出し回路SA,LAが選択されたメモリセルから情報を読み出す期間は、書き換え回路WD1,WD2が読み出し回路SA,LAが読み出した情報に基づいて選択されたメモリセルに情報を書き込む期間より短い。

(もっと読む)

磁気トンネル接合デバイスおよび製作

磁気トンネル接合(MTJ)デバイスおよび製作方法が、開示される。特定の実施形態では、底部キャップ層および垂直軸を有する底部金属充填トレンチを含む構造体上に磁気トンネル接合(MTJ)デバイスを形成するステップを含む方法が、開示され、磁気トンネル接合デバイスは、底部電極、磁気トンネル接合層、磁気トンネル接合シール層、上部電極、およびロジックキャップ層を含み、磁気トンネル接合デバイスは、垂直軸からオフセットしているMTJ軸を有する。  (もっと読む)

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】配線間の抵抗値を低減させる、クロスポイント型メモリセルを積層した多層構造の半導体記憶装置を提供する。

【解決手段】半導体基板1と、互いに交差する第1の配線WL及び第2の配線BL並びにこれら第1及び第2の配線の交差部で両配線間に接続されたメモリセルMCを有する1または複数のセルアレイ層MAと、セルアレイ層MAよりも下層の第1配線層M1に形成された第3の配線11と、セルアレイ層MAよりも上層の第2配線層M2に形成された第4の配線12と、第3の配線11及び第4の配線14を接続する積層方向に延びるコンタクト141〜144とを有する。第1配線層M1と第2配線層M2の間には、冗長配線層が形成される。冗長配線層には冗長配線131〜133が形成され、第3の配線11と冗長配線131〜133との間及び第4の配線12と冗長配線131〜133との間は、複数のコンタクト141〜144により接続される。

(もっと読む)

1 - 20 / 42

[ Back to top ]