Fターム[4M119KK16]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | 実装技術 (34)

Fターム[4M119KK16]の下位に属するFターム

パッド電極、ボンディング電極 (14)

Fターム[4M119KK16]に分類される特許

1 - 20 / 20

半導体装置の製造方法

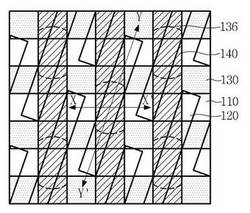

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

磁気メモリ

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気メモリは、第1領域内の第1の磁気抵抗効果素子1Aと、第2の領域の磁気抵抗効果素子1Xとを含む。第1の磁気抵抗効果素子1Aは、磁化の向きが可変な第1の記憶層10と、磁化の向きが不変な第1の参照層12と、非磁性層11と、第1のシフト調整層13と、を含む。第2の磁気抵抗効果素子1Xは、磁化の向きが可変な第2の記憶層10と、磁化の向きが不変な第2の参照層12と、第2の非磁性層11と、第2のシフト調整層13Xと、を含む。第2のシフト調整層13Xの膜厚t2は、第1のシフト調整層13の膜厚t1以下である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

磁気トンネリング接合装置、メモリ、メモリシステム及び電子装置

【課題】磁気トンネリング接合装置を具備する半導体メモリ装置、メモリ、メモリシステム及び電子装置が提供される。

【解決手段】磁気トンネリング接合装置が提供される。この装置は磁性膜を含む第1構造体と、少なくとも2つの外因性垂直磁化構造体を含み、前記外因性垂直磁化構造体の各々は磁性膜及び前記磁性膜上の垂直磁化誘導膜を含む、第2構造体と、前記第1及び第2構造体の間のトンネルバリアと、を包含できる。前記第2構造体は追加的な外因性垂直磁化構造体をさらに含み、その各々が磁性膜及び前記磁性膜上の垂直磁化誘導膜を含んでもよい。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体チップを磁気シールド層で被覆しても、バンプを狭いピッチで配置することができるようにする。

【解決手段】半導体チップ100は磁気記憶素子10を有しており、かつ第1面に電極パッドを有している。磁気シールド層400は、少なくとも電極パッドが露出した状態で半導体チップ100を被覆している。半導体チップ100は、バンプ310を介して配線基板200に実装されている。半導体チップ100と配線基板200は、少なくとも一方が凸部を有しており、当該凸部上にバンプ310が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

携帯情報機器

【課題】情報を迅速かつ確実に消去可能な携帯情報機器を提供する。

【解決手段】機器本体1と、使用時に機器本体1に装着される付帯物2と、機器本体1の付帯物2が装着される部分に設けられ、磁性体の磁化状態により情報を保持する固体磁気メモリ3と、付帯物2を機器本体1に装着したときに固体磁気メモリ3に対向する部分を含む付帯物2に設けられた、磁気シールド4とを含む携帯情報機器を構成する。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

磁気トンネル接合デバイス

磁気トンネル接合デバイスを製造するおよび使用するシステムおよび方法が開示される。特定の実施形態において、磁気トンネル接合デバイスが、第1自由層と第2自由層とを含む。また、磁気トンネル接合が、スピントルク強化層を含む。磁気トンネル接合が、第1自由層と第2自由層との間にスペーサー層をさらに含み、前記スペーサー層が、1つの材料を含み、第1自由層と第2自由層との間の交換結合を実質的に抑制する厚さを有する。第1自由層と第2自由層とが、静磁的に結合される。  (もっと読む)

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

パッケージされた集積回路装置及びその動作方法とこれを有するメモリ保存装置及び電子システム

【課題】減少した信号スキューを提供するマルチチップ・パッケージされた集積回路装置及びその動作方法を提供する。

【解決手段】本発明のパッケージされた集積回路装置は、導電性パッドを上に含む基板と、基板上に複数のチップを含むチップスタックと、1次導電性ラインと、2次導電性ラインと、を備える。1次導電性ラインは、基板上の導電性パッドと、チップスタックの複数のチップのうちの一つの上に設けられた導電性パッドとを電気的に連結する。2次導電性ラインは、チップスタック内の複数のチップのうちの一つの上に設けられた導電性パッドを、その上側にある複数のチップのうちの一つ、及び下側にある複数のチップのうちの一つの上に設けられた対応する導電性パッドに電気的に連結する。

(もっと読む)

磁気記憶装置

【課題】MRAMの情報の記録動作時における安定動作と、記録情報の安定保持とを可能にした磁気記憶装置を提供する。

【解決手段】ダイ110は、基板と、第1および第2配線と、磁気記憶素子と、第1の磁気シールド構造とを有する。第1の磁気シールド構造は、平面視において磁気記憶素子を覆うように形成されている。第2および第3の磁気シールド構造113、114は、厚み方向においてダイ110を挟んでいる。リードフレーム部材112は、ダイ110が実装され、かつ強磁性体を含有する。リードフレーム部材112は平面視においてダイ110の一部のみと重複している。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】複数のMTJメモリセルアレイを同一チップ内に含む半導体集積回路装置の製造工程を効率化する。

【解決手段】システムLSI100は、複数のMRAM回路ブロック110a〜110fを備える。MRAM回路ブロック110a〜110fは、MTJメモリセルが行列状に配置されるMTJメモリセルアレイ10a〜10fをそれぞれ含む。MTJメモリセルアレイ10a〜10fの各々には、書込データに応じて双方向のデータ書込電流を流すためのビット線BLが配置される。MTJメモリセルアレイ10a〜10fのそれぞれにおけるビット線BLの延在方向は、システムLSI100上で同一方向である。

(もっと読む)

半導体メモリ装置

【課題】より小型化(薄型化)および高速化を達成することが可能な異なる種類のメモリを含む半導体メモリ装置を提供する。

【解決手段】この半導体メモリ装置は、ビット線と、ビット線と交差するように配置されたワード線と、ビット線とワード線との間に配置された記憶手段とを有するメモリセルを含む第1メモリと、第1メモリとは種類の異なる第2メモリとを備え、第1メモリと第2メモリとは、同一の半導体基板上に積層して形成されており、ビット線は、主ビット線と、主ビット線に接続され、メモリセルアレイ毎に配置された補助ビット線とを含み、記憶手段は、補助ビット線とワード線との間に配置されており、主ビット線と、補助ビット線とは、同じ方向に延び、かつ、平面的に見て互いに重なるように配置されている。

(もっと読む)

1 - 20 / 20

[ Back to top ]