Fターム[5B011DA07]の内容

Fターム[5B011DA07]に分類される特許

41 - 60 / 91

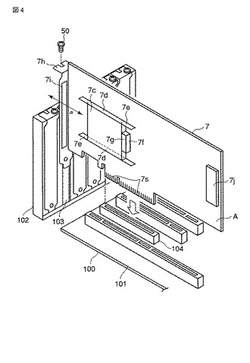

サーバ装置およびバッテリ交換制御方法

【課題】 サーバ装置を停止させることなく、容易にバッテリの交換が可能なサーバ装置およびバッテリ交換制御方法を提供する。

【解決手段】 メイン基板101に対して直行し、かつ接続部材7hが接続孔103に勘合するように装着されたRAIDコントローラボード7の一方の面の長手方向αに開閉蓋7iを解放し挿通することにより着脱可能に装着されたバッテリ7cによってバックアップされるキャッシュメモリがクリアーされていると判別した場合は、バッテリ7cの交換を促す処理を行う。

(もっと読む)

表示端末及び表示端末プログラム

【課題】表示端末の電力の消耗により生じる電池残量に関するユーザの混乱を防ぐことができる表示端末及び表示端末プログラムを提供する。

【解決手段】表示端末では、キー入力操作等のユーザによる操作又は外部からのアクセスが行われた際のイベントが発生した日時が計時装置より取得され、取得された日時がEEPROMに設けられている最終イベント日時記憶エリアに記憶される。そして、表示端末への電力供給が断たれる処理が行われる前に、最終イベント日時記憶エリアから最終のイベントが発生した日時を取得し(S21)、表示端末の電気泳動表示部に表示される(S22)。そして、最終のイベントが発生した日時を表示したまま、表示端末への電力の供給が断たれる(S23)。

(もっと読む)

改良型バッテリ状態学習サイクル装置および方法

本発明の実施形態は、データ記憶装置内のバッテリ・バックアップ・ユニット用の改良型バッテリ学習サイクル装置および方法を含む。バックアップ・ユニットは、第1のバッテリパックと、対応する充電容量ゲージと、1つまたは複数の第2のバッテリパックと、対応する充電容量ゲージと、任意の所与時間において、学習サイクルにただ1つのバッテリパックだけを選択するように構成された制御器スイッチとを含む。充電容量ゲージは、学習サイクルの放電段階終了時に、学習サイクル・バッテリパックの放電深度が、学習サイクル・バッテリパックの充電容量と、残りのバッテリパックの満充電容量とを組み合わせると、装置のキャッシュ格納データが物理的データ記憶装置にオフロードされるのに十分となり、データ記憶装置がライトバック・キャッシュ・モードからライトスルー・キャッシュ・モードに切り換わる必要がなくなる放電深度となるものである。  (もっと読む)

(もっと読む)

情報処理装置及び端末並びに充電器

【課題】端末に搭載された二次電池の容量が一旦不足した後は、専用の充電器が無ければ当該端末を使用できないようにする。

【解決手段】充電器3は、プログラムを記憶するプログラム記憶部35を備える。端末2は、接続状態にある充電器3のプログラム記憶部35からプログラムを取り込む。そして、充電器3から取り込んだプログラムを揮発性記憶部203に格納する。端末2は、この揮発性記憶部203に格納されたプログラムに基づいて情報処理を行う。

(もっと読む)

周辺装置

【課題】 PCからのインターフェースを使用して二次電池を充電できる周辺装置において、PCの駆動が二次電池であったとしても、インターフェースを使用して充電した場合でも、周辺装置より先にPCの電源が落ちることが無いようにする。

【解決手段】

PCの駆動が二次電池駆動なのか商用電源なのかにより場合分けを行い、二次電池駆動であったとしても、周辺機器側でPCの二次電池の残量を監視することにより、周辺機器側にPCから電力を供給していた場合でも、周辺機器より先にPCの電源が落ちることが無いように、周辺機器の二次電池の残量を見極めながら、動作状態を変更する。

(もっと読む)

情報処理装置システムおよび充電制御方法

【課題】燃料電池ユニットから電力供給を受ける情報処理装置において、情報処理装置に設けられた二次電池の最適な充電制御を実現する情報処理装置システムを提供する。

【解決手段】充放電可能な二次電池80を具備する情報処理装置18と、情報処理装置18に着脱可能に接続され、化学反応により発電可能な燃料電池を有する電池ユニット10とを具備する情報処理装置システムであって、情報処理装置18は二次電池80を充電する際に、この情報処理装置18が電源オン状態である場合は二次電池80の充電の満充電検出を行わずに充電を実行し、情報処理装置18が電源オフ状態である場合は二次電池80の満充電検出を行い、満充電を検出した場合充電の停止をおこなう。

(もっと読む)

ハンディターミナル

【課題】 主電池からの電源供給が停止した場合にも、RAMに書き込み中のデータを安全に保存することができる、ハンディターミナルを提供する。

【解決手段】 主電池16、RAMをバックアップする副電池17、主電池16から副電池17に切り替える間にCPU1を通常動作させるキャパシタ18を搭載する。そして、主電池16からの電源供給が停止した場合に、CPU1の電源を主電池16からキャパシタ18に切り替える。CPU1はキャパシタ18から電源の供給を受けている間に、RAM12にデータ書き込み中であればデータの書き込みを完了する。その後、キャパシタ18が放電し電圧が低下した後に、CPU1とRAM12の電源を副電池17に切り替え、この副電池17によりCPU1をスリープ状態に維持すると共に、RAM12がデータを保持できるようにバックアップする。

(もっと読む)

電子機器、電子機器の電源制御方法、およびコンピュータが実行するためのプログラム

【課題】表示パネルを、バッテリを電源として駆動する電子機器において、ユーザの希望使用時間中、可及的にユーザビリティを落とすことなく、バッテリを持続させることが可能な電子機器を提供することを目的とする。

【解決手段】パネル31の各輝度間での消費電力デルタを登録した輝度間消費電力デルタテーブル42と、バッテリ25の残量を検出するPower Managerドライバ52と、パネル31の輝度を設定するPower Manager51とを備え、Power Manager51は、ユーザのバッテリ25の希望動作時間と、バッテリ残量と、および輝度間消費電力デルタテーブル42のデータとに基づいて、パネル31の輝度を設定する。

(もっと読む)

情報処理装置および同装置のメモリ制御方法

【課題】マルチプロセッサシステムの稼働状況に応じてメモリデバイスの消費電力を低減することを実現した情報処理装置同一構成の複数のプロセッサを効率的に使い分けることを実現した情報処理装置を提供する。

【解決手段】EC/KBC21は、CPU11が内蔵する複数のコア11a〜11bの稼働数を監視し、このコア11a〜11bの稼働数に応じて、省電力化のためのメインメモリ13の制御を当該メインメモリ13のメモリ構成単位毎に実行する。

(もっと読む)

半導体集積回路及び半導体集積回路が組み込まれた半導体装置

【課題】

本発明の課題は、独立して電圧の設定が可能な電源系統を複数有する半導体装置であって、電源変動の抑止を図った半導体装置を提供することにある。

【解決手段】

外部制御回路からの制御によって電位を制御される第1電源と、前記外部制御回路からの制御によって電位を制御され、前記第1電源とは独立して電位の設定が可能な第2電源と、前記第1電源により駆動される回路から構成される第1電源系統と、前記第2電源により駆動される回路から構成される第2電源系統と、前記外部制御回路から、前記第1電源系統及び前記第2電源系統を同電位で動作させていることを示す電位一致信号を受けて、前記第1電源系統の第1高電位線と前記第2電源系統の第2高電位線との接続動作をする接続回路と、を備えることを特徴とする半導体集積回路。

(もっと読む)

携帯型無線端末

【課題】蓋体部の開閉の繰り返しにかかわらず、本体部および蓋体部からの常に確実なデータ入力が可能な信頼性にすぐれた携帯型無線端末を提供する。

【解決手段】本体部2にデータ入力およびデータ送信の機能を持たせ、蓋体部4にも専用のデータ入力およびデータ送信の機能を持たせる。蓋体部4が閉じられているときに本体部2に設けられた第1電池から蓋体部4に設けられた第2電池への充電路を形成し、蓋体部4が開いているときに充電路を遮断する充電手段を備える。

(もっと読む)

電圧レギュレータ

【課題】複数の内部回路にそれぞれ供給する電圧のずれを低減することが可能な電圧レギュレータを提供する。

【解決手段】電圧レギュレータ100の制御回路1は、第2の電源端子A2の第2の電圧が第1の電源端子A1の第1の電圧よりも高い場合には、第2の可変抵抗R2の抵抗値が第1の可変抵抗R1の抵抗値よりも大きくなるように、少なくとも第2の可変抵抗R2を調整して、第1の出力端子X1の電圧と第2の出力端子X2の電圧とを接近させる。

(もっと読む)

多電源制御方法及び半導体集積回路

【課題】本発明は、多電源制御方法及び半導体集積回路に関し、複数の電源からの電源電圧を用いるドメイン間で高速なデータ転送を行うことを可能とすることを目的とする。

【解決手段】複数の電源からの電源電圧を用いる複数のドメインと、ドメイン間に設けられドメイン間のデータの受け渡しを行う非同期ブリッジ部を備え、負荷に応じて少なくとも各ドメインで用いる電源電圧を動的に変更可能な構成を有する半導体集積回路の多電源制御方法において、少なくとも2つのドメインで用いる電源電圧が同じ場合、1つの電源からの電源電圧を前記2つのドメインに対して供給するように電源パスを切り換え、前記2つのドメイン間のデータの受け渡しを非同期ブリッジ部をバイパスして行うようにデータパスを切り換えるように構成する。

(もっと読む)

電源制御装置及びこれを備えた電子装置並びに電源制御方法

【課題】電源の小型化及びコストの低減を図りつつ、供給対象に適切に電力を供給することができる電源制御装置を提供すること。

【解決手段】少なくとも2台以上の電源装置からの電源供給を必要とする電源供給対象装置に対して、複数の電源装置による電源供給制御を行う電源制御装置であって、各電源装置が電源供給可能な状態であるか否かを監視し、電源供給対象装置が電源供給を必要とする台数の電源装置が電源供給可能となった場合に、当該電源供給可能となった複数の電源装置から電源供給対象装置に電源供給を開始するよう制御する制御手段を備えた。

(もっと読む)

電源装置および電源システム

【課題】電源装置の異常に対応するとともに回路構成の簡易化を図ることが可能な電源装置および電源システムを提供する。

【解決手段】電源装置101は、バスラインBUS1を介して他の電源装置102,103と接続される電源装置であって、電圧を生成する電圧生成回路1と、自己の電源装置の異常を検出して異常検出信号を出力する異常検出回路2と、異常検出回路2から受けた異常検出信号をバスラインBUS1経由で他の電源装置102,103へ出力し、かつバスラインBUS1経由で他の電源装置102,103からの異常検出信号を受けて出力するインタフェース回路3と、異常検出回路2から異常検出信号を受けた場合、またはインタフェース回路3から異常検出信号を受けた場合には、電圧生成回路1を制御して電圧の生成を停止させる異常制御回路4とを含む。

(もっと読む)

携帯端末

【課題】サスペンド処理における緊急用電源の電圧降下量を小さくする。

【解決手段】CPU速度対応テーブル71には、デバイス8,9の動作状態毎に、携帯端末100において設定可能な複数のCPU速度のうち、サスペンド処理における緊急用電源2の電圧降下量が最も小さくて済むCPU速度が予め対応付けられている。主電源1からの電源供給が切断された際には、デバイス8,9の動作状態が判別され、判別されたデバイス8,9の動作状態に基づいて、CPU速度対応テーブル71からデバイス8,9の動作状態に対応するCPU速度が読み出され、読み出されたCPU速度に基づいてサスペンド処理が実行される。

(もっと読む)

電源バックアップシステム及びこれを具えた電子機器

【課題】信頼性が高く、低コストでバッテリをバックアップすることができる電源バックアップシステムの提供。

【解決手段】ACPIシステム100が、メモリモジュール130(メモリ)と、メモリに電力が供給されていることを示す電源確定信号および節電モードへの移行を指示する5Vのスタンバイ信号を出力する主電源110と、節電モードへの移行の指示がなされたことを示すS3制御信号を出力するACPIコントローラ150と、主電源110からメモリに供給される電力を節電モード時の低消費電力に切り替えるDUAL回路180と、メモリに向けて電力を供給可能な補助電源170と、主電源110からの電源確定信号およびACPIコントローラ150からのS3制御信号の出力状況を監視して補助電源170からの電力供給を制御可能なバッテリ制御部160とを有する。

(もっと読む)

電子機器

【課題】待機時の消費電力を低減することができる電子機器を提供することを課題とする。

【解決手段】第1のバッテリの電圧を変換する電源生成回路(15)と、前記電源生成回路により生成された出力電圧を監視し、前記電源生成回路により生成された出力電圧が安定した電圧を保持するように前記電源生成回路の制御を行う電圧保持制御回路(16)と、前記電源生成回路により生成された出力電圧を監視するための比較基準電圧を生成する電源供給部(17)と、第2のバッテリで駆動され、前記電源生成回路により生成された出力電圧が目標電圧までに達する時間、あるいは複数の電源生成回路の出力電圧の生成開始順序及び出力電圧の生成開始のタイミングを制御する電源シーケンス制御回路(18)と、動作信号を入力すると、前記電源供給部のオン及び前記電源シーケンス制御回路の動作開始を指示する動作指示回路(19)とを有する電子機器が提供される。

(もっと読む)

バックアップ装置

【課題】 2次電池等よりも安価であるが蓄電容量の小さいコンデンサをバックアップ電源として採用しつつ、確実にバックアップ処理を行えるようにする。

【解決手段】 この発明が適用されたデータ通信装置10は、主電源電圧Vaを検知するための電圧検知回路36と、バックアップ電源としてのコンデンサ18の両端間電圧Vbを検知するための電圧検知回路38と、CPU20を含む負荷回路42に印加される電圧Vcを検知するための電圧検知回路40と、を有している。CPU20は、電圧検知回路36および40の出力信号AおよびCに基づいて、主電源電圧Vaの供給が断たれたことを認識する。そして、バックアップ処理に必要な電気エネルギがコンデンサ18に蓄えられていることを、電圧検知回路38の出力信号Bから認識すると、当該バックアップ処理として、相手方装置との通信履歴データをCFカード16に書き込む。

(もっと読む)

マイクロコンピュータ

【課題】マイクロコンピュータにおいて、低消費電力化を実現することができる技術を提供する。

【解決手段】内部電源1で動作するCPU101と、内部電源2で動作する保持用RAM104とを具備する。内部電源1と内部電源2とを供給してCPU101のクロックが動作する通常動作モードと、内部電源1と内部電源2とを供給してCPU101のクロックが停止するスリープモード又はソフトウェアスタンバイモードと、内部電源1を遮断して内部電源2を供給してCPU101のクロックが停止するディープスタンバイモードとを有する。そして、ディープスタンバイモードから通常動作モードへの復帰時のブートアドレスを選択するアドレス切換器102を具備し、かつ選択されるブートアドレスの一方は外部に接続されたROM114であり、他方は保持用RAM104であることを特徴とする。

(もっと読む)

41 - 60 / 91

[ Back to top ]