Fターム[5B015JJ43]の内容

Fターム[5B015JJ43]に分類される特許

1 - 20 / 25

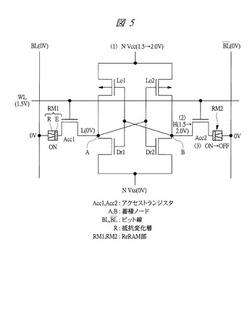

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

不発揮性SRAM及びその操作方法

【課題】SRAMの読み書き機能と不揮発性メモリの不揮発記憶特性をあわせ持つ不発揮性SRAMセルを提供する。

【解決手段】二つの出力ノードを設けるラッチと、前記二つの出力ノードのうちの一つとビットラインペアのうちの一つとの間に接続されるアクセストランジスタからなるSRAMセルにおいて、前記二つの出力ノードのうちの一つと電圧ラインとの間に不揮発性メモリ素子を接続することにより、不揮発性SRAMセルを構成する。

(もっと読む)

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体記憶装置

【課題】トリミングデータはチップ毎に固有のランダムなデータであるため、外部装置により複数チップを同時測定している場合、チップ個別の制御が必要となり、テスト時間・テストプログラム開発工数等のテストコストやテストプログラム複雑化によるヒューマンエラー増大を招く。

【解決手段】チップ内部でトリミング値を算出して不揮発性メモリに記憶し、必要に応じてトリミングデータを取り出して、リファレンスセルのVtレベルやオシレータの周波数を調整する。チップ毎に固有のランダムなトリミングをチップ内部で行えるので、外部装置により複数チップを同時測定している場合でも、チップ個別の制御が不要となる。このため、テスト時間・テストプログラム開発工数等のテストコストを削減でき、テストプログラム複雑化によるヒューマンエラーを低減できる。

(もっと読む)

不揮発性記憶素子及びその制御方法

【課題】故障率及び消費電力を充分に小さくすることができる不揮発性記憶素子を提供する。

【解決手段】複数のメモリセルが配列された不揮発性記憶素子100であって、複数のメモリセルのそれぞれは、端子Aと端子Bとを有するインバータ部と、端子Aとビット線140との導通及び非導通を切り替える選択トランジスタ120と、端子Bとビット線141との導通及び非導通を切り替える選択トランジスタ121と、一端が端子Aに接続された固定抵抗130と、固定抵抗130の他端と信号線144との導通及び非導通を切り替える制御トランジスタ122と、一端が端子Bに接続され、固定抵抗130より高抵抗又は低抵抗となることが可能な可変抵抗131と、可変抵抗131の他端と信号線144との導通及び非導通を切り替える制御トランジスタ123とを備える。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

CMOSプロセスに相変化メモリを組み入れた不揮発性SRAMセル

【課題】不揮発性SRAMセルを提供する。

【解決手段】CMOS技術により形成された2つのクロスカップル型インバータを有するSRAMセルと、記憶セルに不揮発性特性を追加するためにSRAMセルと一体化された第1及び第2のカルコゲン素子とを提供する。PCM抵抗は、SET状態及びRESET状態にプログラムされ、電源投入時には、SRAMセルがPCMセルに含まれるデータを有する。

(もっと読む)

半導体装置

【課題】簡単な構成で多機能化を図った記憶回路を有する半導体装置を提供する。

【解決手段】複数のメモリセルのそれぞれは、第1と第2記憶ノードに交差接続された入力と出力がそれぞれ接続された第1と第2インバータ回路と、第1と第2記憶ノードと第1と第2入出力端子との間にそれぞれ設けられた第1、第2スイッチMOSFETと、第1記憶ノードと第3記憶ノードの間に設けられた第3スイッチMOSFETとを有する。第1と第2記憶ノードは、第1と第2入出力端子からの第1記憶情報が書き込み/読み出し可能にされる。第3記憶ノードは、第2記憶情報に対応して電源電圧又は接地電位が定常的に供給される。第3記憶ノードの記憶情報は、第3スイッチMOSFETをオン状態にして第1、第2記憶ノードに伝えられる。第1、第2スイッチMOSFETを介して第1と第2端子から読み出し可能にされる。

(もっと読む)

不揮発性半導体記憶素子、及び不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置が備える不揮発性半導体記憶素子を標準的なCMOSプロセスで製造するトランジスタを用いて構成する。

【解決手段】標準的なCMOSプロセスによるトランジスタ二個を一組とし備える記憶部200は、ソース・半導体基板間に発生するバンド間トンネル電流が流れる際に発生する正孔と電子を、半導体基板とゲート酸化膜の境界付近にある結晶欠陥にトラップさせる。結晶欠陥に正孔又は電子をトラップしたトランジスタは閾値が変化するので、記憶部200が備えるNMOSトランジスタ201とNMOSトランジスタ202の閾値の変化によるドレイン電流の差をSRAM部100が備えるセンスアンプ回路で検出することにより記憶されたデータの読み出しを行う。

(もっと読む)

プログラマブルROM

【課題】回路複雑化やコスト増なく、SRAMをプログラマブルROMとして使用する。

【解決手段】本発明の例に係るプログラマブルROMは、第1及び第2電源端子の間に直列に接続される第1電界効果トランジスタP1及び第2電界効果トランジスタN1と、ゲートがワード線WLに接続され、第1ビット線BLと第1及び第2電界効果トランジスタP1,N1のドレインとの間のデータ転送に使用される第3電界効果トランジスタN3と、第1及び第2電源端子の間に直列に接続される第4電界効果トランジスタP2及び第5電界効果トランジスタN2と、ゲートがワード線WLに接続され、第2ビット線bBLと第4及び第5電界効果トランジスタP2,N2のドレインとの間のデータ転送に使用される第6電界効果トランジスタN4とを備える。第1及び第4電界効果トランジスタP1,P2の閾値は、互いに異なり、その大小関係は、ROMデータに応じて決定される。

(もっと読む)

半導体記憶装置

【課題】 電源立ち上げ時において、揮発性メモリの通常動作で必要とされる設定情報の設定を、簡単な構成で、処理時間及びCPU負荷を低減できる半導体記憶装置を提供する。

【解決手段】 揮発性の第1データ記憶領域21に対する通常動作の実行に必要な設定情報を記憶する揮発性のモードレジスタを備える揮発性半導体記憶装置20と、不揮発性の第2データ記憶領域12と設定情報を有する不揮発性の設定情報記憶領域を備える不揮発性半導体記憶装置10を備え、不揮発性半導体記憶装置10が、電源立ち上げ検知手段30と、電源立ち上げ後、通常動作前に、揮発性半導体記憶装置20に対し、設定情報を自動的に送出する設定情報送出手段13と、を備え、揮発性半導体記憶装置20が、電源立ち上げ後、通常動作の実行前に、不揮発性半導体記憶装置10から設定情報を受け付けてモードレジスタに記憶する設定情報記憶手段を備えて構成される。

(もっと読む)

半導体記憶装置及び当該半導体記憶装置を具備する電子機器

【課題】電源が切れても記憶状態を保持することができ、且つ揮発性メモリと同程度のコストで製造でき、且つ読み出しまたは書き込みの速度が揮発性メモリと同程度の半導体記憶装置を提供することを課題とする。

【解決手段】メモリセルを選択するためのトランジスタと、メモリセルの記憶状態を保持するためのラッチ回路を有し、ラッチ回路を構成するインバーター回路の高電位電源側にはダイオードが接続され、ラッチ回路に容量素子が接続される構成とする。ラッチ回路を具備する半導体記憶装置において、電源が切られた状態でもラッチ回路に接続された容量素子が電位を保持し、そしてラッチ回路を構成するインバーター回路の高電位電源側に接続されたダイオードが容量素子に保持された電荷のリークを防ぐことが出来る。その結果、不揮発性を有する半導体記憶装置を安価に提供することができる。

(もっと読む)

半導体記憶装置

【課題】メモリセルの面積を増大させたり、CMOSプロセスを追加させることなく、信頼性の高い不揮発性メモリを実現すること。

【解決手段】6個のMOSトランジスタP1、P2、N1、N2、T1、T2よりなるSRAMセルと、第1トランスファMOSトランジスタT1のゲートと電気的に接続される第1ワード線と、第2トランスファMOSトランジスタT2のゲートと電気的に接続される第2ワード線と、を備える。駆動回路は、第1PMOSトランジスタP1に係る書き込み動作の際、N型ウェル2、第1、第2PMOSトランジスタP1、P2のソースに絶対値が接合耐圧以下の正電圧を印加するとともに、第1ワード線W1に正電圧を印加し、第2ワード線W2の接地電圧を印加し、かつ、第1データ線D1に接地電圧を印加する。

(もっと読む)

1 - 20 / 25

[ Back to top ]