Fターム[5B017BA01]の内容

Fターム[5B017BA01]に分類される特許

281 - 300 / 396

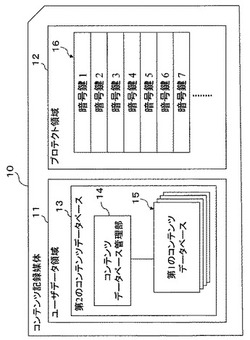

コンテンツ記録媒体

【課題】従来規格から最大格納コンテンツ数を拡大した場合に、機器に求められる処理能力も拡大する。

【解決手段】ユーザデータ領域11とプロテクト領域12を備えるコンテンツ記録媒体10において、ユーザデータ領域11には複数の第1のコンテンツデータベース15と1つのコンテンツデータベース管理部14を含む第2のコンテンツデータベース13を格納し、コンテンツデータベース管理部14では全ての複数の第1のコンテンツデータベース15で管理されるコンテンツの属性情報を当該コンテンツと対応付けた上で管理し、プロテクト領域12には暗号鍵16を格納する。

(もっと読む)

RFIDタグ

【課題】RFIDタグ内のメモリへのアクセス制御の新しい方式を提供する。

【解決手段】RFIDタグ1は、ISO15693に準拠した第1信号処理回路22と、ISO14443に準拠した第2信号処理回路24と、複数のバンクに分割されたメモリ40を備える。RFIDタグ1の制御回路30は、外部装置2との間でISO15693で通信を行っている場合は、外部装置2に対し、メモリ40のうちバンク1のみへのアクセスを許可し、ISO14443で通信を行っている場合は、外部装置2に対しバンク1〜4へのアクセスを許可する。

(もっと読む)

情報記録媒体およびその記録装置、記録方法、記録プログラム

【課題】 Discに記録したデータを恒久的に確実に保存する方法が存在せず、ユーザや機器の不慮の操作によって本来は恒久的にDiscに記録しておきたかったデータが削除される危険性がある。

【解決手段】 上記の課題を解決するため、本発明では特定のデータをファイナライズやDiscの初期化に依らず、また機器やOSによらず修正不可能な状態で光Discにデータを記録可能であることを特徴とし、例えば、前記削除や更新ができないデータはファイルシステム情報として設定されたり、前記削除や更新ができないデータは通常のファイル操作、装置では書込不能であることを特徴とする。

(もっと読む)

情報入力サーバ、非公開情報蓄積サーバ、情報入力システムおよび情報入力受付方法

【課題】 情報入力サーバが、入力項目ごとに入力情報の保存場所を変えたり、公開/非公開の識別をしたりする。

【解決手段】 非公開情報の入力に関する入出力項目定義および公開情報の入力に関する入出力項目定義を含む入出力項目定義情報211と、入出力項目定義情報211を取得する入出力項目定義取得部110と、取得した入出力項目定義情報211に基づき、非公開情報および公開情報の入力フォームを作成する入力フォーム作成部121と、各入力フォームに基づいて、端末装置10により入力されたデータを受け付け、受け付けたデータのうち、公開情報を公開情報DB130へ出力する受付部120と、受付部120により受け付けたデータのうち、非公開情報を非公開情報DB220へ出力する非公開情報出力部150と、公開情報DB130に格納された公開情報を、ネットワーク経由で閲覧させる情報公開部140とを備える構成とした。

(もっと読む)

動作履歴保護装置及び動作履歴保護プログラム

【課題】本発明は、システム全体の性能劣化を抑制しつつ、プロセスの動作履歴をバッファオーバーフロー攻撃等から安全に保護することを目的とする。

【解決手段】 制限付権限プロセス処理部200は、オペレーティングシステムの各種機能を利用することができる特権レベルよりも低い制限付権限レベルであり、各種機能の一部のみを利用することができる制限付権限レベルに基づいて動作する制限付権限プロセスを制御する。カーネル特権プロセス処理部300は、特権レベルに基づいて動作するカーネル特権プロセスを制御する。制限付権限プロセス処理部200は、制限付権限プロセスの動作の履歴を制限付権限プロセス処理部200に記録し、カーネル特権プロセス処理部300は、制限付権限プロセス処理部に記録される動作の履歴のうちの特定動作の履歴をカーネル特権プロセス処理部300に記録する。

(もっと読む)

メモリアクセス制御回路、方法およびアプリケーション格納方法

【課題】マルチアプリケーションに対応していないOSであっても、安全性の高いメモリアクセス制御を実現する。

【解決手段】アプリケーションが格納されるメモリ領域のアドレス情報を含むアプリケーション参照リストを有し、アプリケーション参照リストへアドレス情報を登録する割付け部121と、割付け部121による登録後、アプリケーション参照リストへの変更を禁止するラッチ部122と、アプリケーション参照リストに基づいて、アドレス情報が割付けられる複数のアプリケーション参照領域123と、アプリケーションの実行の制御を行うシステム111による指示に基づいて、アプリケーション参照領域123の切り替えを行う切替部124とを有することで、マルチアプリケーションに対応していないOSであっても、安全性の高いメモリアクセス制御が実現できる。

(もっと読む)

プログラム生成方法およびプログラム

【課題】 メモリ空間を保護するプログラムをソフトウェア開発者に大きな負担をかけることなく生成する。

【解決手段】 本発明のプログラム生成方法は、ソースプログラムと、ソースプログラム内の関数をドメイン毎に分類したメモリ保護ポリシーとを入力し、大域変数と前記大域変数を利用するドメインとを対応づけた情報を生成し、前記大域変数を利用するドメインを上位および下位ドメインに分割し、前記上位ドメインに対応するアクセス制御表において前記大域変数に対してのアクセス制限を読み書き許可に設定する命令を前記ソースプログラムに追加し、前記下位ドメインに対応するアクセス制御表において前記大域変数に対してのアクセス制限を読み出し許可に設定する命令を前記ソースプログラムに追加する。

(もっと読む)

プログラム保護機能を持つプロセッサ

【課題】保護対象プログラムの動作解析が困難となり、命令コードの読出し/書き換えを禁止することで実現していたプログラムの保護レベルを向上させることができるプログラム保護機能を持つプロセッサを提供する。

【解決手段】復号化されて平文となった保護プログラムは命令実行のための命令読み出しのみ可能としてプログラム保護を行うプロセッサコアモジュール100であって、保護プログラムの命令を実行中であるか否かを検出する検出手段200と、検出手段200で保護プログラム実行中であることが検出された場合は、実行中の命令のトレース情報生成を停止する停止手段400とを備えるプログラム保護機能を持つプロセッサ。

(もっと読む)

ダイレクト・メモリ・アクセス制御方法及びダイレクト・メモリ・アクセス・コントローラ

【課題】 他のチャネル用のメモリ領域へのアクセスを防止できるDMA制御方法及びDMAコントローラを提供する。

【解決手段】 使用するメモリ領域の始端アドレスSAと終端アドレスEAとを各チャネルに対して設定しておき、DMA転送が開始されてアクセスアドレスが終端アドレスEAに達した場合に、アクセスアドレスを始端アドレスSAへ戻して、アクセスを継続する。各チャネルに設定された始端アドレスSAと終端アドレスEAとの間のみをアクセスできる。3ページ分のデータを第1チャネルに貼り付ける際に、3ページ目の貼り付け時にメモリ領域が不足する場合((a),(b))、3ページ目のDMA転送時に、1ページ目及び2ページ目と同じ転送回数が設定される。この際、アクセスアドレスが終端アドレスEAに達した場合に、始端アドレスSAへ自動的に戻ってアクセスが継続されるので((c))、第2チャネルにアクセスされることがない。

(もっと読む)

ICカード用LSI

【課題】 LSI搭載メモリへの不正アクセスによるデータの暴露や改竄を防止するため、確実なメモリアクセス制御を実現する。

【解決手段】 ROM13のプログラム領域をメモリアクセス権限により2つに区分し、CPU12からの分岐命令発生信号を検知した場合のみアドレスデコード回路23で分岐先アドレスをデコードし、デコードした分岐先アドレスがROM13のいずれのプログラム領域に属するかをモード設定回路24で判断して該当するモード信号を設定し、設定されたモード信号に従ってアクセス制御回路26が各メモリ13,14,15へのアクセス制御を行う。

(もっと読む)

入出力制御装置,入出力制御方法,プロセス制御装置及びプロセス制御方法

【課題】誤動作による入出力の誤出力を防ぐことを目的とする。

【解決手段】プロセッサが相対的に安全性の高いモードで演算するための入出力値を第1の記憶領域に記憶し、プロセッサが相対的に安全性の低いモードで演算するための入出力値を第2の記憶領域に記憶し、安全性のモードに応じて、第1の記憶領域への転送,第1の記憶領域からの転送,第2の記憶領域への転送、或いは、第2の記憶領域からの転送を制限するように構成した。

(もっと読む)

セキュアハードウェアデスクトップバッファ構成

複数の仮想マシンは、グラフィックスハードウェアとディスプレイを含むホストコンピュータ上で実行される。仮想マシンは、ディスプレイデータをそれぞれの仮想デスクトップバッファに書き込む。ホストコンピュータのディスプレイに出力するため、仮想マシンが選択される。グラフィックスハードウェア上の構成バッファはその選択された仮想マシンに対してイネーブルされる。その選択された仮想マシンと関連する仮想デスクトップバッファのコンテンツは、グラフィックスハードウェアによって、その構成バッファにコピーされる。その構成バッファのコンテンツは、グラフィックスハードウェアによってレンダーされ、表示される。加えて、構成するバッファへの読み取りアクセスは、グラフィックスハードウェアに制限される。その結果、悪意あるソフトウェアアプリケーションがパーティションを越えてディスプレイデータを取り込むことを防止できる。  (もっと読む)

(もっと読む)

摩耗防止を備えたメモリ制御手段を有する記憶システムとメモリの管理方法

【課題】不揮発性メモリの磨耗に解決策をもたらす。

【解決手段】各周期の間、クロック信号またはランダム制御信号が発生すると、メモリ制御手段2が複数の保存領域のうちの一つの内容を空領域Poへと転送し、その保存領域がその後に続く周期のための空領域となるということを、予め設定された周期の回数の後に前記保存領域のそれぞれの内容が一つの空領域に転送されることになるような所定のパターンで行う。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】アクセス制限がなされているサービスメモリ領域へのアクセスを迅速に行う。

【解決手段】 1つのサービスによってアクセスされるサービスメモリ領域は、1個以上のデータブロックで構成され、サービスを定義する所定の定義情報が格納されている定義ブロックが対応付けられている。各定義ブロックの定義情報の中に、そのサービスの実行が制限されていないことを示すPIN設定無効情報またはサービスの実行が制限されていることを示すPIN設定有効情報が設定され、またPIN設定有効情報が設定されている場合には、そのサービスの実行の認証に必要な暗証コードも設定されるようになされている。このPIN設定情報が参照されてアクセスが制限されているか否かが判定される。

(もっと読む)

データ通信装置

【課題】CPUバスに暗号器や通信インタフェースやメモリがそれぞれ独立に接続している構成で、暗号化動作をする度にCPUバス上においてデータをメモリから暗号器へそして暗号器からメモリへと2回移動する必要があり、暗号化、復号化の度にバスの帯域を占有するため非効率であった。

【解決手段】通信インタフェース14と、通信インタフェースにCPUバス11を介して接続されて通信を制御するCPU12と、データを蓄積するメモリ13と、データを暗号化または復号化する暗号器15とを備える。メモリは、そのアドレス空間について、CPUがデータを直接的に読み書き可能な第1のアドレス空間と、CPUがデータを暗号器における暗号処理部15aを介して読み書き可能な第2のアドレス空間とを有し、CPUは、メモリに対してデータの読み書きを行う際に、第1のアドレス空間と第2のアドレス空間とを選択可能に構成されている。

(もっと読む)

仮想計算機の制御方法及びプログラム

【課題】権限レベルが2段階のマイクロプロセッサを用いた仮想計算機において、ゲストアプリケーションとゲストOS及びVMM間のメモリ保護を確実に行う。

【解決手段】少なくとも一つのCPUとメモリを共有して複数のプログラムを切り替えて実行する仮想計算機の制御方法であって、CPUで実行される第1のプログラムがアクセス可能なメモリ領域を規定する第1のメモリ保護テーブルを設定し、前記CPUで実行される第2のプログラムがアクセス可能なメモリ領域を規定する第2のメモリ保護テーブルを設定し、第1または第2のプログラムの実行開始を検出し(S11)、実行開始を検出した第1または第2のプログラムに対応して第1または第2のメモリ保護テーブルの何れか一方を選択して切り替えて(S17)、前記選択した第1または第2のメモリ保護テーブルを前記CPUのメモリ管理ユニットで参照し、前記選択した第1または第2のメモリ保護テーブルに規定されたメモリ領域を保護させる(S18、S19)。

(もっと読む)

情報記憶装置、その制御方法、およびその制御プログラム

【課題】 記憶した情報の存在を他人に知られることを回避して情報の保護を十分に図れ、利便性の向上が図れる情報記憶装置を提供する。

【解決手段】情報記憶装置としてのUSBメモリは、ホスト側機器と情報の入出力を可能に接続する情報入出力部31と、入力した情報を記憶するデータ格納メモリ32と、データ格納メモリ32の全記憶領域のうち情報が記憶されている実体記憶領域を秘匿し情報が記憶されていない空き領域のみをホスト側機器に認識させる旨を指示する仮想認識指示情報を設定入力させる設定入力部33と、情報入出力部31、データ格納メモリ32、および設定入力部33を制御するCPU34とを備える。CPU34は、仮想認識指示情報が設定入力された場合に、データ格納メモリ32の空き領域のみをホスト側機器に認識させるための仮想管理情報を生成し、情報入出力部31を介してホスト側機器に仮想管理情報を提供する。

(もっと読む)

データベース管理方法及びデータベースシステム

【課題】利用者に与えられた権限の範囲内での無差別的な情報取得行為からデータベース中のデータを防衛できるようにする。

【解決手段】本来の用途(業務)では決して参照されることの無いダミーデータをデータベース中に含ませる。このダミーデータを地雷データと称す。この地雷データへのアクセスが発生した場合、データベース管理装置は、不正なデータベースアクセスと判断し、処理を中止して、該当利用者端末へエラーを返す等、あらかじめ定義された内容の対処を行うことで、データベース利用者の権限逸脱行為を防止する。

(もっと読む)

非接触通信担体

【課題】長寿命にして秘密情報のセキュリティ性に優れた非接触通信担体を提供する。

【解決手段】非接触通信担体1Aを、基体2と、当該基体2上に搭載されたIC素子3と、当該IC素子3の入出力端子3a〜3dに接続された第1及び第2のタグ側アンテナ4,5とから構成し、IC素子3には、第1のタグ側アンテナ4が接続された第1の通信回路6と、第2のタグ側アンテナ5が接続された第2の通信回路7と、メモリ領域8と、メモリ領域8を複数の小領域8a,8bに分割して設定する領域切替手段9とを備える。タグ側アンテナ4,5としては、互いに通信可能なキャリア周波数が異なるアンテナを用いる。

(もっと読む)

計算機システム

【課題】

従来の制御装置では、可用性を担う部分装置と安全性を担う部分装置に分けた構成とするのが一般的であり、装置物量の増大を招いていた。

【解決手段】

通常制御モードと安全制御モードが切り替わるときに、共有リソースに対するプロセッサ側および入出力装置側からのアクセス制御状態を変更することで、同一の計算機システム上において両方の制御モードを共存させる。そのために、複数のタスクを実行可能であり、前記複数のタスクで利用する共有リソースを備え、複数の制御モードを有し、前記の各制御モードのもとで1つ以上のタスクを実行する計算機システムにおいて、前記制御モード毎に前記各タスクから前記共有リソースへのアクセスに対するアクセス制御状態を適用し、かつ前記制御モードの切り替えに同期して前記アクセス制御状態を切り替える構成とする。

(もっと読む)

281 - 300 / 396

[ Back to top ]