Fターム[5B017CA11]の内容

Fターム[5B017CA11]の下位に属するFターム

Fターム[5B017CA11]に分類される特許

141 - 160 / 207

端末装置及びそのデータ管理方法

【課題】メモリに格納されているデータが盗難されるのを防止できるとともに、復元することも可能な端末装置及びそのデータ管理方法を提供する。

【解決手段】メモリと、通信部と、前記通信部を介して前記メモリのアクセス要求信号が来たとき認証処理を行う認証処理部と、前記認証処理部が否認結果を得たときに、前記メモリの所定データを前記通信部を介して所定の保存部へ退避させる退避処理部と、前記所定データを退避させた後に前記所定データを前記メモリから消去する消去処理部を有する。

(もっと読む)

マイクロコントローラにおけるデータの安全な取扱いのための方法および装置

マイクロコントローラにおけるデータを、外部データバスおよび/または外部メモリからのデータの読み取りに対する許可なき試行からだけでなく、端末内部で実行される悪意のソフトウェア処理からも保護するための装置および方法が提供される。本発明の例示的実施例は強化されたメモリ管理部(MMU)をある程度利用してセキュリティの向上を達成する。強化されたMMUは、マイクロコントローラ上で実行されている1つのソフトウェア処理が同じマイクロコントローラ上で実行されている異なるソフトウェア処理に関連するデータにアクセスすることを防止する。さらに、外部データバスを介して送信され、または外部メモリに記憶されたデータが暗号化され、これにより、許可なきユーザがそのデータから利用可能な情報を領得する機会を減らす。  (もっと読む)

(もっと読む)

電子カメラ

【課題】認証されない使用者へ記録データが流出することを防止する電子カメラを提供する。

【解決手段】電子カメラ1は、認証動作において撮像した使用者の瞳(虹彩)の画像信号が不揮発性メモリ3に格納されている登録内容と合致すれば(認証OK)カメラモードを起動し、合致しなければ(認証NG)カメラモードを起動しない。電子カメラ1は、認証NGの場合にメモリカバー8cの開扉がメモリカバー開扉センサ14で検出されると、記録媒体8に高圧発生回路13bによる高電圧を印加する。これにより、記録媒体8が破壊されて読み出し不能にされる。

(もっと読む)

半導体デバイスおよび半導体デバイスへの攻撃を防止する方法

本発明は、半導体デバイスに対する不正アクセスを検出する手段を具える半導体デバイスおよびその方法に関するものであり、本発明の半導体デバイスは、不正アクセスの検出後に半導体デバイスの初期化を実行し、不正アクセスに関する情報項目を初期化前に半導体デバイスによって格納することができ、格納された権限なきアクセスに関する情報項目は、半導体デバイスの初期化後にもとのままである。格納された情報項目が、半導体デバイスを電源から切断した後の所定期間の間もとのままであると有利である。  (もっと読む)

(もっと読む)

指紋認証機能付きデータ記憶装置

【課題】配信されたデジタル音楽データ、デジタルデータおよび音声デジタルデータの著作権保護を可能とし、保存データ機密性を高める。

【解決手段】アナログ音声入力部とアナログ音声信号の出力部を具備し、特定使用者の指紋データを予め装置内部に記録する手段と、使用者の指紋画像を読取る手段と、読取った指紋画像と前記予め装置内部に記録されている特定使用者の指紋情報とを照合する手段を具備し、その照合の結果に従い上記使用者が装置内部に記憶されているデータ閲覧または更新の正当な権利保有者であることが確認された場合のみ、アナログ音声信号の入出力を可能にするアナログ信号制御部と、また各種電子機器に接続され、上記のように正当な権利保有者であることが確認された場合のみ、各種電子機器とのデータ通信の入出力を可能にするUSB制御インタフェースとを具備することを特徴とする指紋認証機能附きデータ記憶装置。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置に記憶されるデータで表されている情報を第三者により不正に取得されないようにする。

【解決手段】 メモリセル11は、保持させる電荷量を違えることにより、単一の記憶セルで2値よりも多い多値の値を記憶させることができる。データロジック14は、入力された各桁が2値である記憶データを、メモリセル11の各々で2値の値として桁毎に記憶させる。更に、データロジック14は、記憶データの読み出しの要求が正規のものであるか否かの判定を行い、正規のものである場合には、メモリセル11で保持されている電荷量から2値の値への対応付けを行い、正規のものでない場合には、メモリセル11で保持されている電荷量から上述の多値の値への対応付けを行う。そして、この対応付けがされた値を各桁で並べて得られるデータを、当該要求に係る記憶データとして出力する。

(もっと読む)

電圧グリッチ検出回路とその検出方法

【課題】電圧グリッチ検出回路とその方法を提供する。

【解決手段】基準データを貯蔵するための少なくとも一つのメモリセルを備えるモニタリングメモリアレイと、モニタリングメモリアレイから出力された前記基準データを受信して、作動制御信号に応答して受信された基準データを増幅して、前記基準データに基づいてデータを出力するモニタリング感知増幅器と、基準データを貯蔵するための少なくとも一つのラッチを備えるデータ貯蔵回路と、モニタリング感知増幅器から出力された前記データと前記データ貯蔵回路から出力された前記基準データとを受信して比べて、比較結果に基づいて検出信号を出力するための比較回路と、を備える電圧グリッチ検出回路。

(もっと読む)

プロセッサ、メモリ、コンピュータシステムおよび認証方法

【課題】低コストで、コンピュータへの不正アクセス等の不正行為を防止することのできるプロセッサを提供する。

【解決手段】演算手段と一体に形成され、第1メモリ認証用情報および第2メモリ認証用情報を保持するプロセッサ側メモリ認証用情報保持手段と、第1メモリから取得した第1メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第1メモリ認証用情報とを比較して第1メモリを認証し、さらに第2メモリから取得した第2メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第2メモリ認証用情報とを比較して第2メモリを認証するメモリ認証手段と、メモリ認証手段による認証結果に基づいて、第1メモリおよび第2メモリへのアクセスを制御するアクセス制御手段とを備えた。

(もっと読む)

ICカード用LSI

【課題】 LSI搭載メモリへの不正アクセスによるデータの暴露や改竄を防止するため、確実なメモリアクセス制御を実現する。

【解決手段】 ROM13のプログラム領域をメモリアクセス権限により2つに区分し、CPU12からの分岐命令発生信号を検知した場合のみアドレスデコード回路23で分岐先アドレスをデコードし、デコードした分岐先アドレスがROM13のいずれのプログラム領域に属するかをモード設定回路24で判断して該当するモード信号を設定し、設定されたモード信号に従ってアクセス制御回路26が各メモリ13,14,15へのアクセス制御を行う。

(もっと読む)

半導体装置、及び半導体装置における制御方法

【課題】解析装置や計測装置が接続されても情報が解析されないようにした半導体装置、及び半導体装置における制御方法を提供すること。

【解決手段】負荷検知回路40は、端子DQを介して負荷部100の負荷値を検出する。基準負荷出力部50から、プローブの負荷に対応する基準負荷が出力される。比較回路60は、検知した負荷値が基準負荷と一致するか否かを判断し、一致していると制御信号を出力する。入出力バッファ30はこの制御信号が入力されると、メモリセル10から端子DQへのデータの出力を停止、又は特定の論理を出力する。

(もっと読む)

不揮発性メモリモジュールを有する回路装置、およびこの不揮発性メモリモジュールに対する攻撃を記録する方法

例えばサイドチャネル攻撃のようなEM(電磁)照射攻撃、または例えば電流トレース解析もしくはDPA(電力差解析)のような暗号解析であって、とくに秘密キーの発見を狙いとするこのような攻撃または解析を、確実に回避することができるようにするため、少なくとも1個の光源による少なくとも1個の不揮発性メモリモジュール照射を、検出および/または記録および/または警告する電子データ処理用の回路装置(100)、とくに集積回路および方法を、一層進歩させるために、メモリモジュール(10)に対する少なくとも1回の読み出しアクセス用のアクセスタイミングを生じさせることを提案する。とくに少なくとも1個のDAW(Disable All Wordlines)モードのような、少なくとも一つのテストモード(T)において、メモリモジュール(10)に対する少なくとも1回の追加読み出しアクセスを追加し、このテストモード(T)により、その時点でメモリモジュール(10)がなんらかのエネルギーを有する光に被曝されているか否かを検出できるようにする。  (もっと読む)

(もっと読む)

秘密情報を含む集積回路の試験

未許可のアクセスに対して安全を確保されなければならない情報を含む機能回路(12a−c)を備えた集積回路(10)。この集積回路は、機能回路(12a−c)に結合された試験アクセス回路(14,16)と、この試験アクセス回路(14、16)に結合された複数のヒューズ・エレメントを備える。ヒューズ・エレメント(18)は、複数のヒューズ・エレメントにおける第1のヒューズ・エレメント(18)が断線状態であり、複数のヒューズ・エレメントにおける第2のヒューズ・エレメント(18)が非断線状態の場合だけ、試験アクセス回路(14,16)を経由して機能回路(12a−c)を一貫してアクセスできるようにする回路構成に接続される。その結果、第1のヒューズ・エレメント(18)の全てを選択的に断線した後に、集積回路を試験することができる。試験の後、第2のヒューズ・エレメントの少なくとも一部が断線される。その結果、どのヒューズ・エレメントが第1のヒューズ・エレメントであり、どのヒューズ・エレメントが第2のヒューズ・エレメントであるか知らない人は、集積回路を、安全が確保された情報にアクセスする危険がある試験アクセスが可能な状態に戻すのに困難に直面する。  (もっと読む)

(もっと読む)

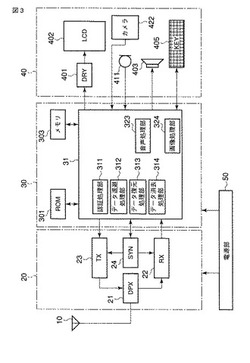

情報処理装置および情報処理システム

【課題】セキュアなプログラムやデータ等を内蔵する半導体チップ等の情報処理装置に対して、認証コードを知らない第三者が次々に通信対象装置を取り替えて繰り返し認証コードを発行して不正アクセスを試行しようとすることに対するセキュリティ性を高める。

【解決手段】通信対象装置400に対して出力するアクセス許可要求信号Saを生成するアクセス許可要求信号生成手段Aと、アクセス許可要求信号を含む第1の通信信号群の通信対象装置に対する出力を制御するもので、アクセス禁止信号Scを入力したときに第1の通信信号群の何れかまたは全ての出力を遮断する出力制御手段Bと、通信対象装置から入力するアクセス拒否信号Sbの有効・無効を判別し、有効と判別したときに出力制御手段にアクセス禁止信号を出力するアクセス拒否信号判別手段Dとを備える。

(もっと読む)

外部からの不正操作に対するセンシティブな電子装置データモジュールのハードウェア保護装置

回路担体にハードウェア保護装置が統合される。これによって回路担体において回路基板の形式で統合されたセンサシステムが得られ、このセンサシステムは従来の「ハイテク」回路基板テクノロジによって製造されかつ電子装置モジュール製造の従来の装着ラインにおいて装着され処理されうる。  (もっと読む)

(もっと読む)

不揮発性メモリアクセス装置及び電機機器

【課題】 EEPROMのライトプロテクト機能を、2個以上のマイコンで同一の処理を行うことにより、どのマイコンがマスターになっても、ライトプロテクト機能を有効に活用する。

【解決手段】 例えば、DVD側マイコン12が、テレビ側マイコン13に、IICバス11の使用権とEEPROM15のライトプロテクト機能の制御権とを渡した場合、DVD側マイコン12は、外部機器25が接続されたときにはIICバス11を開放する機能、及び外部機器25の接続及び取り外しを判定する判定機能を無効とし、出力制御ライン12cを介するDVD制御系の各種デバイス16の制御は無効としない。

(もっと読む)

ICタグの装着方法

【課題】 被装着物に装着したICタグが用済みになったときや取り外しによる悪用を防止するため、不正な取扱いがなされたときICチップを破壊する機能を設けたICタグの装着方法を提供する。

【解決手段】 ICタグ1を構成するICチップ15にその内部回路に接続して電圧印加端子17を設け、不正な取扱いがなされたとき高電圧あるいは逆電圧を電圧印加端子17に印加してICチップ15を電気的に破壊する。

(もっと読む)

情報処理装置

【課題】 情報処理装置を他人へ譲渡、貸与、廃棄、修理により第三者へ一時提供する等の場合に、情報処理装置の使用者の個人情報の漏洩を防止することができる情報処理装置を提供する。

【解決手段】 情報処理装置200は、筐体に取り付けられた外部からアクセス可能なスイッチであり、ユーザにより押されたときに押されたことを制御回路201に通知する廃棄スイッチ202と、廃棄スイッチ202が押されたことが通知された時、情報処理装置200に記録されているユーザ情報を削除する制御回路201とを備える。

(もっと読む)

メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法

【課題】データが不正な手段により書き換られたことを検出できるフラッシュメモリの制御方法、メモリコントローラ及び当該メモリコントローラを備えるフラッシュメモリシステムを提供することを目的とする。

【解決手段】 フラッシュメモリを記憶媒体として利用するホストシステムからの命令に応答して、フラッシュメモリにデータを書き込む書き込み手段と、前記ホストシステムからの命令に応答して、前記書き込み手段によってフラッシュメモリに書き込まれていたデータを読み出す読み出し手段と、前記ホストシステムからの命令に応答して、前記読み出し手段によって読み出されたデータを所定のビット毎に区切って順次加算してチェックサム値を求めるチェックサム算出手段と、から構成される。

(もっと読む)

不揮発性メモリに格納されたデータの整合性管理

本発明は、複数の不揮発性記憶セルを伴うメモリの書き込みコントローラ(10)、複数の不揮発性記憶セルを伴うメモリの読み出しコントローラ、書き込み/読み出し兼用コントローラ、複数の不揮発性記憶セルを伴うメモリを備えるソリッド・ステート・デバイス[solid state device]、不揮発性メモリに2進データを書き込むプログラマ・デバイス[programmer device]、不揮発性記憶セルを備えるメモリに少なくとも1つの入力ビットを備えるデータを書き込む方法、およびメモリの不揮発性記憶セルに格納された少なくとも1つの入力ビットを備えるデータの整合性を管理する方法に関する。本発明は、不揮発性メモリの内容に対して発生した変更を検出する信頼性の高い方法を提供する。本発明の基本的な考え方は、不揮発性メモリに格納された情報を少なくとも1つのチェック・ビットで拡張することである。このチェック・ビットは、1つのコード・ビットまたは複数のコード・ビットのそれぞれに割り当てられる。こうした割り当ては、好ましくは入力ビットおよびコード・ビットを格納するメモリ・セルの割り当てに反映される。  (もっと読む)

(もっと読む)

データ保護のための機密保護方法

相補の機密保護トレースを備える集積回路(IC)機密保護装置、およびそのような装置の製造方法が開示される。機密保護装置は、パターン発生器(30)および複数の機密保護トレース(34、36)を備える。機密保護トレース対(34、36)の配置は、第2のトレース(36)が第1のトレース(34)に対して実質的に平行となるよう配置されるようなものである。パターン発生器(30)は2つの信号を生成し、第2のトレース(36)に印加される第2の信号は、第1の機密保護トレース(34)に対して実質的に相補である。第2の(相補の)信号のタイミングおよび振幅は、正味の誘導電流が実質的に零となるよう生じる。1つ以上の信号が信号発生器から受信され、機密保護トレースを通過した後の同一の信号と比較される。この結果を分析し、ICの機密保護が破られたか否かを決定する。  (もっと読む)

(もっと読む)

141 - 160 / 207

[ Back to top ]