Fターム[5B017CA11]の内容

Fターム[5B017CA11]の下位に属するFターム

Fターム[5B017CA11]に分類される特許

41 - 60 / 207

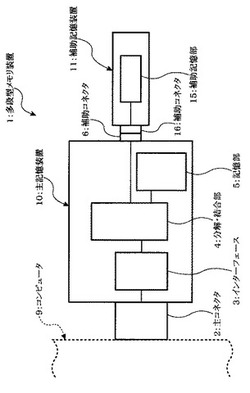

多段型メモリ装置、メモリ装置、記憶方法及び記憶処理用プログラム

【課題】情報漏洩の阻止性能を高めることができ、かつ、使い勝手を向上させることの可能な多段型メモリ装置、メモリ装置、記憶方法及び記憶処理用プログラムの提供を目的とする。

【解決手段】多段型メモリ装置1は、主記憶装置10と、主記憶装置10に対して取り外し可能に接続される補助記憶装置11とを備え、主記憶装置10が、主コネクタ2、インターフェース3、入力した情報を分解し、また、分解された情報を結合する分解・結合部4、分解された情報の一部を記憶する記憶部5、及び、補助コネクタ6を有し、補助記憶装置11が、分解された情報の残部を記憶する補助記憶部15と補助コネクタ16を有する構成としてある。

(もっと読む)

半導体記憶装置

【課題】煩雑な手続きを経ず、しかも複数の利用者で共有等した場合であっても情報の漏洩や改ざんから保護することができる半導体記憶装置を提供すること。

【解決手段】半導体記憶装置は、複数に分割されてデータを保持可能とされたセキュリティ領域を有する第1記憶部104と、セキュリティ領域にアクセスするための情報であって、複数のセキュリティ領域ごとに関連付けられた管理情報を保持する第2記憶部105と、第1記憶部にアクセスするために入力された入力情報を第2記憶部に保持された管理情報と照合し、入力情報と一致する管理情報に関連付けられたセキュリティ領域へのアクセスを可能とする制御コントローラ107と、を備える。

(もっと読む)

電力供給装置、メモリ装置、処理装置、メモリ装置判定方法、ソフトウェア処理システム、処理プログラム、並びに処理プログラムを記録した記録媒体

【課題】ソフトウェアを有するソフトウェアデバイスに対し、このソフトウェアデバイスが不正コピーされたものかどうかを判定し、かつ、不正コピーされたものである場合にはその使用を阻止するソフトウェア処理システム等を提供する。

【解決手段】ゲーム機20では、メモリ装置1が有するゲームプログラムを読み出して実行するゲーム機2のCPU6が、電力制御部7にアクセスしてメモリ装置1に電力を供給させる。次いで、CPU6が負荷制御部3およびメモリ4にアクセスして、メモリ4が有する電力消費データを読み出し、負荷制御部3は負荷を変化させる。その後、電力制御部7にてメモリ装置1に供給する電力が測定され、かつ、当該測定結果が記憶される。次いで、CPU6が再び電力制御部7にアクセスして、上記測定結果を読み出し、読み出した上記電力消費データと比較してメモリ装置1が正規品か否かを判定する。

(もっと読む)

攻撃に対するマイクロ回路の保護方法及びデバイス

【課題】マイクロ回路への攻撃に対して、攻撃によって妨げられることなくマイクロ回路の保護機能を実行することを目的とする。

【解決手段】攻撃に対するマイクロ回路保護方法であって、攻撃が検出されたか否かを判定するステップ(205)と、攻撃が検出された場合に、保護機能を実行するステップ(210、510)と、攻撃が検出されなかった場合に、保護機能を擬似的に実行し、保護機能と実質的に同一の方法でマイクロ回路の外部から検知可能なおとり機能を実行するステップ(215、515)とを有することを特徴とする。ある実施形態では、おとり機能は、保護機能の消費電力と実質的に同一の消費電力を有し、保護機能は、不揮発性メモリの第1のアドレスに所定のデータを書き込むステップを有し、おとり機能は、不揮発性メモリの第1のアドレスと異なるアドレスに書き込むステップを有する。

(もっと読む)

セキュリティ機能を有する携帯端末

【課題】ユーザが幅広い複数の用途に対応すべく自らで検知後処理項目を選択できるようにする。

【解決手段】携帯端末1は、ユーザがセキュリティ要件の事象が発生した場合に行う検知後処理項目の変更操作をキー入力部3により行うと、その変更操作に応じて検知後処理項目を変更し、その後、セキュリティ要件の事象が発生すると、その変更した検知後処理項目に対応する検知後処理を実行する。ユーザは検知後処理項目の変更操作を行うことでセキュリティ要件の事象が発生した場合に行う検知後処理項目を自由に選択することができ、幅広い複数の用途に対してセキュリティを適切に確保することができる。

(もっと読む)

セキュリティモジュール

【課題】セキュリティモジュールからの秘密情報の漏洩を防止する。

【解決手段】セキュリティモジュールの物理的遮蔽1(筐体フレーム)により形成される密閉空間を、間仕切り3とセキュリティチップ4とモールド5から成る隔壁により2分割して2つの気密室6,7を形成する。セキュリティチップ4はモールド5内に埋め込まれており、モールド5にはスリットが設けられている。気密室6,7は同じ気圧で且つ外気圧より低圧(真空等)/高圧となっている。これより、筐体フレームに孔が開けられると、どちらか一方の気密室6,7の気圧が外気圧と同じになり気密室6,7間に気圧差が生じることにより発生する応力が隔壁に加わることで、セキュリティチップ4が破壊される。

(もっと読む)

情報処理装置

【課題】セキュリティレベルの高い半導体装置を提供する。

【解決手段】セキュアLSI1は、プログラムの暗号化を行う暗号化部2と、外部メモリ100との間でプログラムやデータの入出力を行うための外部I/F50とを備えている。暗号化部2において、鍵生成・更新シーケンサ30が、実行が許されないと判断したシーケンスについて、秘密鍵演算処理部20の動作を禁止する。外部I/F50では、プログラム処理部51とデータ処理部55とが別個独立に構成されている。

(もっと読む)

認証装置、認証方法、コンピュータプログラム

【課題】除算を用いた認証処理において除数の秘匿性を高めた認証装置を提供する。

【解決手段】除算に用いられる除数Dを記憶可能な揮発性の第1除数記憶部13と、外部から入力される入力数値Zを第1除数記憶部13に記憶される除数Dで除算したときの剰余R1を生成する剰余生成部10と、基準パスワードR2を記憶する基準パスワード記憶部11と、剰余生成部10で生成された剰余R1と基準パスワード記憶部11に記憶された基準パスワードR2とを比較して、一致すると、認証したこと表す認証信号を出力するパスワード判定部12と、を備える認証装置1である。除数Dは、剰余生成部10により剰余R1が生成される前に第1除数記憶部13に記憶され、パスワード判定部12により認証信号が出力されると第1除数記憶部13から消去される。

(もっと読む)

不揮発性記憶媒体制御装置、不揮発性記憶媒体制御方法、及び不揮発性記憶媒体制御プログラム

【課題】不揮発性記憶媒体への暗号ブロック連鎖モードの暗号データの書き換え時、書き換え処理速度と当該記憶媒体の書き換え寿命を向上させる。

【解決手段】不揮発性記憶媒体のデータ書き換え時、以下の処理を行う。(1)読み出した第1の暗号化データを復号して第1のデータとし、(2)データを構成するデータ要素の配置情報に基づき第1のデータの構成を復元し、(3)第1のデータ処理後の第2のデータを配置情報に基づき変更して第3のデータとし、(4)第3のデータと第1のデータから差分データ要素を特定し、(5)差分データ要素を含むブロックのうち、先頭位置に最も近いブロックより前方のブロックは第1の暗号化データから対応する暗号文ブロックを抽出し、前記ブロック以降のブロックは第3のデータの対応ブロック以降を暗号化して連結し、(6)第1の暗号化データと比較し、変化があるページまたはブロックのみ不揮発性記憶媒体に書き込む。

(もっと読む)

半導体記憶装置

【課題】 チップサイズの増大を抑制しつつ、任意のプロテクト領域を設定することが可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、独立してデータ消去可能な最小単位であるブロックを複数有する不揮発性メモリと、前記不揮発性メモリのバッファとして機能する揮発性メモリと、各々の前記ブロックに対して実行可能な動作を制限するプロテクト情報を保持することが可能なプロテクト用SRAMと、外部から入力されたブロックアドレスに対応する前記プロテクト情報を、前記プロテクト用SRAMから読み出して設定することが可能なレジスタと、前記レジスタに設定された前記プロテクト情報に基づき、前記ブロック対して要求された動作を制限するか否かを決定する制御部と、を具備する。

(もっと読む)

電子機器装置の不正行為防止方法

【課題】例えば製品の廃棄後であっても、高度なセキュリティ性を確保することが可能な電子機器装置の不正行為防止方法を提供する。

【解決手段】少なくとも動作プログラムが格納される不揮発性メモリ(ROM12)と、動作プログラムを消去する消去プログラムが格納されるメモリ(RAM11)と、を有するカードリーダ1の不正行為防止方法であって、上位装置からのメモリ消去コマンドを受信したとき、消去プログラムにより動作プログラムを消去する第1ステップと、消去プログラムを消去する第2ステップと、が含まれる。

(もっと読む)

ハードウェアデータ保護装置

装置が記憶デバイスコントローラと記憶デバイスとの間に接続され、コンピューティングシステムとオペレーティングシステムに独立なコンピューティングスシステムのユーザにとって透過的な方式でデータ記憶デバイス保護を提供する。装置は、1つの記憶デバイスの内容を読み出し専用にすることによって、その実行および、権限のないまたは意図していないユーザのデータ変更を防止することによって、ユーザを悪意のあるコードから保護する。装置の全ての動作は、インストールされたオペレーティングシステムとは独立して、コンピューティングシステムおよびユーザには見えない。装置は、スイッチまたは他の手段によって無効にされうる。これが起きた場合には、その効果は、仮に装置がコンピューティングシステムから物理的に除去されたとした場合と同じになる。  (もっと読む)

(もっと読む)

試験動作モードの間に集積回路のデジタル情報を保護するための方法及び装置

【解決手段】

実施形態は試験容易化設計(DFT)又は他の試験モード攻撃からICを保護する。レジスタ又はラッチ、RAM内に記憶されている一時的な機密、及び/又はROM及び/又はPROM内に記憶されている永続的な機密が保護される。ICの情報を保護するための1つの実施形態は、試験モードに入ることと、試験モードの動作に入ることに応答して、試験モード命令を受け取るよりも前に各レジスタをリセットすることとを含む。集積回路の実施形態は、集積回路を試験モードに設定し且つ試験モードの間は集積回路を制御するように動作する試験制御論理と、一連のレジスタと、試験制御論理及び一連のレジスタに結合され試験制御論理からリセット命令を受け取り且つ試験モードに入るための命令に応答してリセット命令を一連のレジスタに供給するように動作する機能リセット制御器とを含む。

(もっと読む)

情報削除機能付きLSI

【課題】半導体チップ単体での耐タンパ性を高めた情報削除機能付きLSIを提供することを目的とする。

【解決手段】情報削除機能付きLSI311は、制御回路12で処理される情報が格納される記憶手段であるメモリ13と、メモリ13に格納される前記情報を消去する消去手段である消去回路14と、消去回路14に電力を供給する発電手段である発電機構15と、外部からの情報の変化を検出してメモリ13に格納される前記情報を消去すべきことを判断して消去回路14に指示する検出手段である検出回路16と、を備える。

(もっと読む)

半導体記憶装置及びコンピュータシステム

【課題】メモリ容量の削減を伴うことなく、セキュリティ強度を高めることが可能な、半導体記憶装置を得る。

【解決手段】半導体記憶装置3は、メモリ5と、ホスト機器2からメモリ5へのアクセスを制御するメモリコントローラ4とを備える。メモリコントローラ4は、制御部20と記憶部21とを有する。メモリ5は、コンテンツデータD1が記憶された第1領域R1と、コンテンツデータD1に関連するデータD1A1〜D1A3が記憶された第2領域R31〜R33とを有する。記憶部21には、第2領域R31〜R33への所定アクセス順序が記憶されている。制御部20は、ホスト機器2から第2領域R31〜R33へのアクセスにおけるアクセス順序が、所定アクセス順序に一致していることを条件として、ホスト機器2から第1領域R1へのアクセスを許可する。

(もっと読む)

不揮発性メモリ装置及びLSI装置

【課題】不正コピーを阻止しつつ、長寿命化を図る。

【解決手段】入力されたセキュリティコード****とセキュリティコード保存メモリ22内のセキュリティコード****とが一致した場合、CPU1から入力された論理アドレス○○○○とアドレスメモリ21内の物理先頭アドレス****とに基づいて、正しい物理アドレス※※※※(=****+○○○○)を算出し、この正しい物理アドレス※※※※及び入力された読出/書込命令に基づいて、正しい物理アドレス※※※※に対応するデータ△△△△をフラッシュメモリ部10から読出/書込みする。このように、セキュリティコードが一致した場合にアドレスメモリ21から物理先頭アドレスを読み出すので、不正コピーを阻止できる。また、入力される論理アドレスと、メモリ部10の物理アドレスとが異なるため、メモリ部全体の書き換え頻度を均等にでき、長寿命化を図り得る。

(もっと読む)

データ完全消去機能付記憶装置、その方法及びそのプログラム

【課題】外部の消去装置を用いることなく、記憶装置単体でデータの消去をする。

【解決手段】データを記憶する記憶装置におけるデータ消去装置が、データを消去する指示及びデータを消去する方法を受け付けるスイッチ部を有する。受け付けたデータを消去する方法が論理的データ消去方法である場合は、記憶媒体にデータを書き込むことでデータ消去を行う。前記受け付けたデータを消去する方法が物理的データ消去方法である場合は、記憶媒体を物理的に破損させることでデータ消去を行う。

(もっと読む)

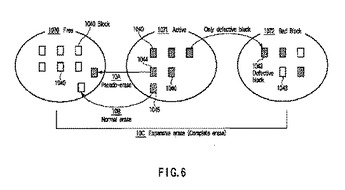

情報処理装置及び不揮発性半導体メモリドライブ

不揮発性半導体メモリドライブの制御部は、論理ブロックアドレスそれぞれと不揮発性半導体メモリの物理アドレスそれぞれとの対応関係を示すアドレス管理テーブルを初期化して不揮発性半導体メモリの記憶領域をユーザデータが書き込まれていない状態に設定する第1消去モードと、前記アドレス管理テーブルを初期化して前記記憶領域をユーザデータが書き込まれていない状態に設定し、且つ前記記憶領内に含まれる、不良ブロック以外の各ブロックをイレーズする第2消去モードと、前記アドレス管理テーブルを初期化して前記記憶領域をユーザデータが書き込まれていない状態に設定し、且つ前記記憶領内に含まれる、不良ブロックを含むブロックそれぞれをイレーズする第3消去モードとを有する。  (もっと読む)

(もっと読む)

取り外し可能ディスクドライブ格納システム上の追記型モードの実装のための装置

【課題】データをアーカイブするための、ネットワーク格納システムにおける改良されたモジュラードライブベイを提供すること。

【解決手段】本発明によるモジュラードライブベイは、1つ以上の取り外し可能ディスクドライブであって、該1つ以上の取り外し可能ディスクドライブは、アーカイブデータを格納するように動作可能であり、該1つ以上の取り外し可能ディスクドライブは、WORM制御を用いてデータを不変に維持するように動作可能である、1つ以上の取り外し可能ディスクドライブを含み、各取り外し可能ディスクドライブは、データカートリッジケースと、コネクタと、組み込み式メモリとを含む。

(もっと読む)

メモリ監視方法

【課題】不正行為によってデータが消失してall 0になった場合でも、CRC等の誤り検知符号の計算結果を異常として出力することができるメモリ監視方法を提供する。

【解決手段】本発明のメモリ監視方法は、機密データ及び誤り検知符号が格納されたメモリ15と、電子機器装置1の各種動作に必要な作業データが格納される作業メモリ11とを備えた電子機器装置1において、電子機器装置1の電源立ち上げ時に、メモリ15内に格納されている誤り検知符号を、作業メモリ11に格納し、一方で、常時メモリ15に格納されている機密データの誤り検知符号の計算をしていき、計算をした結果算出される誤り検知符号と作業メモリ11に格納された誤り検知符号とを比較する。

(もっと読む)

41 - 60 / 207

[ Back to top ]