Fターム[5B018LA03]の内容

記憶装置の信頼性向上技術 (13,264) | 電源 (239) | 電圧比較、検出 (84)

Fターム[5B018LA03]の下位に属するFターム

バックアップ電圧検出 (15)

電源断の予告信号 (24)

Fターム[5B018LA03]に分類される特許

21 - 40 / 45

メモリシステム

【課題】動作信頼性を向上させるメモリシステムを提供すること。

【解決手段】データを保持可能な不揮発性のメモリセルを備えた半導体メモリ3と、バックアップ電源2と第1外部電源(電源C)とが供給されるバックアップ制御回路6とを具備し、前記バックアップ制御回路6は、前記半導体メモリ3が前記メモリセルへのデータの書き込み中に前記第1外部電源が遮断された際に前記バックアップ電源2から与えられる電圧を前記半導体メモリ3に供給し、前記書き込みが終了した後前記バックアップ電源2から与えられる前記電圧の供給を停止する。

(もっと読む)

データ処理装置

【課題】補助電源の容量を増大させることなく、バックアップされないメモリのデータを確実に退避させるデータ処理装置を提供する。

【解決手段】 電源回路9からの電源供給が遮断(電源電圧の低下が検出)されても、電源遮断時間の間は、RAMモジュール10やASIC20への電源供給が継続されることを利用し、この間に、RAMモジュール10に格納されているデータを、バックアップ電源回路33からバックアップされた第2低電圧BDLの供給を受けるSDRAM11,12に退避させる。

(もっと読む)

メモリ判定システム、メモリ判定方法およびメモリ判定プログラム

【課題】メモリの運用を中断することなく、ハードウェアに起因する障害であるかの判別を行うことのできるメモリ判定システム、メモリ判定方法およびメモリ判定プログラムを得ること。

【解決手段】メモリの出力にコレクタブルECCエラーが発生したら(ステップS201:Y)、電圧制御回路は電圧制御線を使用してメモリの印加電圧を許容範囲内で所定時間変動させる(ステップS203)。この時間内に再びコレクタブルECCエラーが発生したら(ステップS204:Y)、固定障害が発生したと判定する(ステップS206)。それ以外はソフトウェアの障害と判定する(ステップS208)。本発明では、メモリを運用しながらエージングが可能である。

(もっと読む)

電源状態検出装置

【課題】最後にユーザが車両の電源状態を変化させた際のバッテリ10の電圧がEEPROM2の書き込み可能電圧より低く、その後に電源制御部6がリセットされた際にも実際の車両の電源状態と電源制御部6で認識される電源状態とを一致させることのできる電源状態検出装置を提供する。

【解決手段】EEPROM2の書き込み可能電圧より低い電圧に書き込み可能電圧を有するRAM7を備える。このような電源状態検出装置によれば、RAM7を備えているので、バッテリ10の電圧がEEPROM2の書き込み可能電圧より低い際に車両の電源状態が変化されてもRAM7に車両の電源状態に関するデータを記憶させることができる。このため、この後に電源制御部6がリセットされても、電源制御部6はRAM7に記憶させたデータから車両の電源状態を認識することができ、実際の車両の電源状態と電源制御部6で認識された車両の電源状態とを一致させることができる。

(もっと読む)

半導体記憶装置

【課題】少なくともフラッシュメモリ部分を過電流から保護して、ラッチアップなどによる故障を未然に防止すること。

【解決手段】複数のフラッシュメモリ2と、ホスト装置100に接続するためのコネクタと、複数のフラッシュメモリ2とホスト装置100との間のデータ転送のためのキャッシュメモリ4と、複数のフラッシュメモリ2とホスト装置100との間のデータ転送を制御するドライブ制御回路3と、外部電源電圧を内部電源電圧に変換する電源回路5とが基板上に搭載され、少なくともフラッシュメモリ2を過電流から保護するヒューズ10を基板上に設ける。

(もっと読む)

データ処理回路及び通信携帯端末装置

【課題】マイクロコントローラの動作が動作保証範囲内で特定の動作条件から逸脱して性能劣化したときマイクロコントローラ内部のデータに対する不正アクセスの抑制に寄与する。

【解決手段】書換え可能な不揮発性メモリ(146)及び不揮発性メモリの制御と外部インタフェース制御とを行うコントローラ(147)を有するデータ処理回路の動作が第1の動作条件から逸脱したか否かを検出する第1検出器(152)と、データ処理回路の動作が前記第1の動作条件よりも厳しい第2の動作条件から逸脱したか否かを検出する第2検出器(154)を採用し、第1検出器が前記第1の動作条件からの逸脱を検出することに応答して前記コントローラにリセットを指示する。コントローラは、前記第2検出器が前記第2の動作条件からの逸脱を検出することに基づいて内部状態をバックアップすると共に、前記不揮発性メモリの記憶領域に対する外部からのアクセス制限を行う。

(もっと読む)

マイコン装置

【課題】電源電圧が基準電圧よりも低下したときに、揮発性メモリ内のデータを不揮発性メモリに速やかに退避できるマイコン装置を提供する。

【解決手段】CPU7と揮発性メモリ9と不揮発性メモリ11とがバス接続されてなるマイコン装置1Bにおいて、電源電圧Vddと第1基準電圧Vref1とを比較し、電源電圧Vddが第1基準電圧Vref1よりも低下した時に割込要求信号を出力する第1コンパレータ3と、電源電圧Vddと第2基準電圧Vref2とを比較し、電源電圧Vddが第2基準電圧Vref2よりも低下した時に割込要求信号を出力する第2コンパレータ4と、第1コンパレータ3からの前記割込要求信号と第2コンパレータ4からの前記割込要求信号に応じて起動し、バス13経由で揮発性メモリ9内のデータを不揮発性メモリ11に転送するDMA転送手段5とを備える。

(もっと読む)

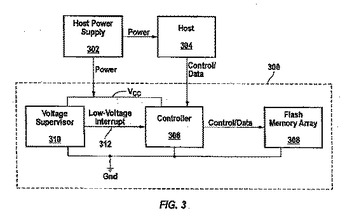

不揮発性メモリのための改良された書き込み中断機構

コントローラと、コントローラによって制御される不揮発性メモリアレイとを有する不揮発性メモリ(NVM)装置で、NVM装置に給電する電圧源の出力を電圧監視回路で監視する。電圧監視回路はNVM装置の一部をなす場合と、これに結合される場合とがある。電圧監視回路は、NVM装置に給電する電圧源の出力が所定値を下回るのを検出すると「低電圧」信号をアサートするように構成される。コントローラは、「低電圧」信号がディアサートされている間はメモリアレイにデータを書き込み、「低電圧」信号がアサートされている間はデータの書き込みを保留するように構成される。「低電圧」信号がアサートされると、コントローラは処理中の書き込みサイクル/プログラム操作がある場合はこれを完了し、「低電圧」信号がアサートされている間はさらなる書き込みサイクル/プログラム操作を阻止する。  (もっと読む)

(もっと読む)

メモリ信頼性を向上させるシステム及び方法

【課題】メモリ信頼性を向上させるシステムを提供する。

【解決手段】メモリ・セルが動作する電圧とメモリ・セルをアクセスする論理回路素子が動作する電圧との間の相対的な変動から生じる不安定性と書込み性問題を減少させるシステムは、電圧が許容可能な動作範囲内にないときにメモリ・アクセスを禁止する。第1の電圧で電力を受ける論理回路素子を有するパイプライン方式のプロセッサ及び第2の電圧で電力を受けるSRAMセルのセットを備える。クリティカル状態検出器は、第1の電圧と第2の電圧をモニタするように、かつこれらの電圧の比が許容可能な範囲内であるかどうかを決定するように設定される。電圧が許容可能な範囲内にないときに例外が発生され、例外ハンドラは、SRAMセルへのアクセスを禁止するためにプロセッサ・パイプラインをストールする。電圧が許容可能な範囲に戻ると、パイプラインをレジュームし、例外の取り扱いを終了する。

(もっと読む)

電源回路、フラッシュメモリシステム及び電源供給方法

【課題】フラッシュメモリシステムが誤動作してしまうことを確実に防止する。

【解決手段】電圧調整回路11は、外部から供給される電源電圧(Vin)とこの電源電圧(Vin)によってコンデンサC2に充電される充電電圧(C2電圧)のいずれか高い方の電圧をフラッシュメモリシステムに供給する動作電圧に調整して出力する。電圧検出回路12は、充電電圧が第1の設定値より低くなったときに、充電電圧が第1の設定値より低くなったことをメモリコントローラに通知する警告信号(DET_VDD)を出力する。電圧検出回路13は、充電電圧が第1の設定値より小さい第2の設定値より低くなったときに、トランジスタQ1をオンさせる信号を出力する。トランジスタQ1がオンすると、コンデンサC2に充電されている電荷の放電が開始され、コンデンサC2の充電電圧は負荷変動の影響を受けることなく降下する。

(もっと読む)

電子回路内のデータメモリへのアクセスを制御するための方法及び装置

本発明は、とりわけ自動車用のタコグラフにおいて、第1のメモリ領域と第2のメモリ領域とを有する電子回路内のデータメモリへのアクセスを制御するための方法に関している。データ保全性を高めるため、本発明では、第1のメモリ領域(2)は比較的高い安全性をもって保護されるべきデータを記憶するために設けられており、第2のメモリ領域(3)は比較的低い安全性をもって保護されるべきデータを記憶するために設けられており、供給電圧(UV)が測定され、供給電圧が予め定められた第1の電圧閾値(UVS1)を下回っている場合には、前記第1のメモリ領域(2)へのアクセスが遮断される。本発明はまた、データストア(4)を有する電子回路(5)を備えた、上記方法を実行するための装置、とりわけ自動車用のタコグラフにも関している。  (もっと読む)

(もっと読む)

データバックアップシステム及び電力低下検知装置

【課題】電源に停電又は瞬断等が発生して電力が低下した場合に、不揮発性の記憶手段を備えない装置のデータをバックアップすることができるデータバックアップシステム、及びこのシステムの構成要素をなし、電源の電力の低下を検知する電力低下検知装置を提供する。

【解決手段】分電盤1の最も近傍に設置された電力低下検知装置10が、交流電圧の振幅の低下を検知して電力の低下を検知し、電力低下通知を複合機30及び電気機器50へ送信する。これに応じて、不揮発性の記憶手段を備えない電気機器50はバックアップするデータを電力低下検知装置10へ送信し、これを受信した電力低下検知装置10が複合機30へデータを転送し、複合機30に備えられた不揮発性の記憶手段にバックアップする。

(もっと読む)

情報記録装置

【課題】電源切断後の不揮発性の記録媒体への情報記録を確実に行うことのできる情報記録装置を提供する。

【解決手段】電源切断後の不揮発性の記録媒体への情報記録を確実に行うため、電源供給部と、不揮発性記録部と、電源供給部からの電力供給を受けて不揮発性記録部への情報の記録を行う制御部と、を具備し、制御部が、電源供給部が供給する電力を監視し、当該電力が予め定めた記録限界のしきい値を下回るまで、情報の記録を実行する情報記録装置である。

(もっと読む)

半導体ディスク装置の異常監視・記録方法、プログラム、半導体ディスク装置、および記憶システム

【課題】半導体ディスク装置内の異常発生による半導体ディスク装置やシステムの停止時間を最小限にすることができる半導体ディスク装置の異常監視・記録方法、プログラム、半導体ディスク装置、および記憶システムを提供する。

【解決手段】この半導体ディスク装置1Aは、電源ユニット18や冷却ファンユニット19の駆動状況を内部モニタ14Aで監視し、その監視結果を常時不揮発性のEEPROM20に記録する。それらの箇所に異常が発生したことによりシステムが停止した場合には、記録された監視結果に基づいて故障原因を把握できるため、修理のために要する半導体ディスク装置1Aやシステムの停止時間を短縮することができる。

(もっと読む)

メモリコントローラおよびフラッシュメモリシステム

【課題】フラッシュメモリシステムに供給される電源電圧が所定の電圧より低くなったときに、フラッシュメモリに対する処理を停止させるメモリコントローラおよびフラッシュメモリシステムを提供する。

【解決手段】電源電圧が予め設定された第1の電圧より低くなったときに処理を停止し、その後、電源電圧が予め設定された第2の電圧より高くなったときに処理を再開する。更に、処理を停止してから処理を再開するまでの間に予め設定された第3の電圧の電圧より低くなった期間がある場合は、電源電圧が第2の電圧より高くなっても、停止していた処理を続行せずに処理を中止する。

(もっと読む)

データ保持装置

【課題】ポータブル機器に使用されるデータ保持装置において、電源断あるいは瞬断が発生した場合においても、データの破壊が発生しない、小型で優れた特性を持つデータ保持装置を提供することを目的とする。

【解決手段】EEPROMまたはフラッシュメモリの電源をバックアップ電源より供給し、その電源供給線に電源切り離しスイッチを設け、そのスイッチを、メインバッテリの電圧低下検出信号と、EEPROMまたはフラッシュメモリから出力されるREADY/BUSY信号の、両方を条件として制御することにより、バックアップ電源の消費電力を抑えながら、電源断あるいは瞬断で、データが破壊しないデータ保持装置が得られる。

(もっと読む)

プラント用ネットワーク機器及びそのデータ修復方法

【課題】バックアップ電源がないため保守作業が不要で機器構成が簡単かつ長寿命で、しかもプラントから受信するデータを確実に保存でき、データの信頼性が高いプラント用ネットワーク機器及びデータ修復方法を提供する。

【解決手段】プラントから送信されるデータが伝わるバス9に、コンピュータ1を介してデータを記録保存する大容量メモリ4と、コンピュータ3に電源を供給する平滑コンデンサを有する電源回路3と、電源遮断を監視する電圧監視回路2とを接続している。また、バスには論理回路を接続し、この論理回路6を介してデータの記録保存をする高速メモリ5を備えて構成することを特徴とするものである。大容量メモリ4と高速メモリ5には、不揮発性メモリを使用する。電圧監視回路2で電源遮断を電源遮断の監視し、電源遮断の時に高速メモリ5に一時的に記録したデータを、電源の復電時に高速メモリ5からデータを大容量メモリ4に格納修復する。

(もっと読む)

データ処理装置

【課題】 停電等の電源異常時および地震等の衝撃を受けた時のいずれにおいてもデータ保護を行うことができるデータ処理装置を提供する。

【解決手段】 このデータ処理装置は、データ処理を行うCPU1と、CPU1によって書き込みおよび読み出しが行われるRAM3およびHDD装置10を具備する。CPU1は、RAM3への書き込みデータと同じデータを不揮発メモリ4に書き込み、RAM3からの読み出しデータと同じデータを不揮発メモリ4に書き込む。加速度検出手段7は外部から加えられる衝撃の強さを検出する。電源電圧検出手段8は電源電圧を検出する。CPU1は加速度検出手段7によって検出された衝撃の強さが第1の一定値を越えた時、HDD装置10の書き込みを禁止すると共に、不揮発メモリ4の書き込みを禁止する。また、電源電圧検出手段8によって検出された電源電圧が第2の一定値以下となった時、不揮発メモリの書き込みを禁止する。

(もっと読む)

記憶制御装置および記憶制御方法

【課題】 電源電圧降下による不揮発性メモリでのデータ破壊を、安価かつ簡単な構成で防止できるようにする。

【解決手段】 不揮発性の記憶装置EEPROM217にデータ書き込みまたは読み出しを行う記憶制御装置において、電源インターフェース218より供給された電源電圧13Vから電源電圧3.3Vを発生して、EEPROM217およびCPU203に供給する。一方、電圧検出回路220が、電源電圧13Vの実際の電圧値を検出し、CPU203に送る。CPU203は、検出時間がずれた2つ電圧値を基にして電圧変動度合を算出し、算出された電圧変動度合と電源電圧13Vの実際の電圧値とに基づいて、EEPROM217に対するデータ書き込みまたは読み出しを許可するか否かを判断する。

(もっと読む)

メモリバックアップ回路およびこれを用いた電子機器

【課題】 停電検出回路の単一故障によるバックアップ動作不良を回避し、バッテリの長寿命化を実現する。

【解決手段】 例えばディスクアレイ装置のメモリバックアップ回路に、外部電力を入力し回路に必要な直流電圧を出力する直流電源回路と、前記外部電力の入力状態を監視する第1の停電検出回路と、前記直流電源回路の出力電圧を監視する第2の停電検出回路と、前記外部電力の消失時に揮発性メモリへ電力を供給するバックアップ電源と、前記第1または第2の停電検出手段から停電検出信号を受けた場合に前記揮発性メモリのバックアップ制御を実施するメモリ制御手段と、前記第2の停電検出手段のみが電圧低下を検出した場合に前記バックアップ電源の電力を所定期間前記メモリ制御手段へ供給するスイッチ手段とを設ける。

(もっと読む)

21 - 40 / 45

[ Back to top ]