Fターム[5B018QA05]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 稼働時 (637) | 電源異常時、電源切断時 (333)

Fターム[5B018QA05]に分類される特許

101 - 120 / 333

データ記憶制御装置及びデータ記憶制御方法

【課題】ハイバネーション処理等の効率化を図ることが可能なデータ記憶制御方法を提供すること。

【解決手段】データ記憶制御方法は、複数の仮想メモリ領域に対応した複数の仮想アドレスと第1記憶手段の複数の物理メモリ領域に対応した複数の物理アドレスとの対応関係を管理したアドレス管理テーブルに基づき、各仮想アドレスにより各物理メモリ領域に記憶されたデータへのアクセスを制御する仮想記憶に適用される方法であって、前記アドレス管理テーブルにより所定数の仮想メモリ領域に対応付けられた所定数の不連続な物理メモリ領域に記憶されたデータを所定数の連続した物理メモリ領域へ書き込み、前記アドレス管理テーブルにより前記所定数の仮想メモリ領域の各仮想アドレスと前記所定数の連続した物理メモリ領域の各物理アドレスとを対応付け、前記所定数の連続した物理メモリ領域に書き込まれたデータを圧縮し、圧縮データを第2の記憶手段へ書き込む。

(もっと読む)

ディスクキャッシュシステム、ディスクキャッシュ再利用方法およびディスクキャッシュ再利用プログラム

【課題】メモリ上のディスクキャッシュそのものを再起動後のOSが引き継ぐことができるようにする。

【解決手段】主記憶装置100上に展開されたOS200の再起動手段201がOS200を再起動する前に、ディスクキャッシュ情報作成手段202がディスクキャッシュ情報301を作成し、ディスクキャッシュ情報退避領域300に格納する。OS200が再起動されメモリの初期化が開始されるとディスクキャッシュ保護手段203が呼び出され、ディスクキャッシュ情報301に含まれるメモリフレーム管理情報804に基づいて、ディスクキャッシュ806として利用されているメモリフレーム805は初期化せず保護し、他は初期化する。ディスクキャッシュ情報復元手段は204はディスクキャッシュ情報301に基づいて、再起動前に利用していたディスクキャッシュの情報をOS200内に復元する。

(もっと読む)

メモリシステム

【課題】DRAMログの容量サイズを削減し、不正な電源断の際にも管理情報の整合を保つ。

【解決手段】ログ記憶エリアに蓄積記録されるタイプBログが設定値を超えた場合、タイプBの管理情報に関しては、マスターテーブルを更新し、ログ記憶エリアへの記録動作を中止し、コミット実行条件が成立したときに、コミットではなく、スナップショットを実行する。

(もっと読む)

コンピュータ装置、データ記憶方法、および、記憶処理プログラム

【課題】揮発性記憶部に、一定期間の間、データを一定に保持するために必要な処理が行われなくても、当該揮発性記憶部に記憶されたデータの消失を防止可能な技術を提供することを目的とする。

【解決手段】コンピュータ装置1は、DRAM4と、保持能力値取得部6と、個数決定部7と、制御部8とを備える。保持能力値取得部6は、DRAM4の保持能力値を決定する。個数決定部7は、保持能力値に基づいて、記憶対象のデータが、DRAM4に記憶されるべき個数を決定する。制御部8は、記憶対象のデータを、個数決定部7で決定した個数だけDRAM4に記憶する。

(もっと読む)

フラッシュメモリのデータ消失防止装置及びフラッシュメモリのデータ消失防止方法

【課題】フラッシュメモリにおいてデータ消失を発生し難くすることができるフラッシュメモリのデータ消失防止装置及びフラッシュメモリのデータ消失防止方法を提供する。

【解決手段】フラッシュメモリ6の対をなす2ブロックのうちの一方を、通常のデータ書き込み時において用いるローテーションブロックとして使用し、もう一方を、ローテーションブロックと同じデータを書き込みミラーブロックとして使用する。そして、使用中のローテーションブロックに書き込みエラーが発生した際には、その後のデータ読み書きをミラーブロックにおいて実行し、書き込みエラー発生後のデータ読み書きを継続する。また、電源再投入後の初期化時、ミラーブロックに書き込んだデータ群をローテーションブロックにコピーし、ミラーを再構築する。

(もっと読む)

電子制御装置

【課題】分割ブロック単位で一括消去を行ってから書込が行われる不揮発データメモリの一括消去回数を削減する。

【解決手段】各種の制御定数が格納される不揮発データメモリとして、ブロック単位で一括消去が可能なフラッシュメモリが使用され、各分割ブロックは複数のデータ格納領域に仕分けされており、どれかのデータ格納領域において空セクションが無くなると、予め一括消去された他の分割ブロックの該当データ格納領域の先頭セクションに新たなデータが書込まれ、元の分割ブロックの中の他のデータ格納領域に書込まれていた最新のデータは、新たな分割ブロックの該当データ格納領域の先頭セクションに転送格納され、一つの分割ブロックに異なるデータ格納領域を混在させ、各データ格納領域は書込み頻度に対応した複数のセクションによって構成することによって分割ブロックの個数を削減し、しかも一括消去回数を削減することができるようにした。

(もっと読む)

フラッシュメモリの動作保護装置及びフラッシュメモリの動作保護方法

【課題】フラッシュメモリに対するドライバのアクセスを保護することができるフラッシュメモリの動作保護装置及びフラッシュメモリの動作保護方法を提供する。

【解決手段】フラッシュメモリ6がデータ消去単位として持つ複数のブロック7〜10のうち特定の1つ(本例は、Dブロック10)を、ローテーションに使用しない固定ブロック10として使用し、この固定ブロック10に、アプリケーション11を動作させるのに最低限必要な初期動作情報として製品固有値14や初期値15を保存する。そして、電源リセット等によりドライバ13がアクセス先を見失った際には、固定ブロック10に保存された製品固有値14や初期値15をローテーションブロックに書き込み、これらデータによってドライバ13を動作させることによって、ドライバ13を継続動作させる。

(もっと読む)

メモリ装置および計算機

【課題】プログラムとデフラグとを並行して実行した場合に、不揮発性メモリに格納されたデータに発生する不整合を未然に防止する。

【解決手段】メモリとデフラグ部とメモリ保護部とバッファメモリとCPUとMMUとが接続され、バッファメモリは、デフラグのコピー元とコピー先とのメモリのアドレスとコピー先フラグとを含み、デフラグ部は、デフラグ部の状態フラグを備え、メモリページ切り替えのタイミングで、デフラグのコピー元とコピー先とのメモリのアドレスをバッファメモリに格納しデフラグし、メモリ保護部は、CPUからメモリの参照または更新の命令と対象メモリのアドレスを受信し、状態フラグが非アイドル状態の場合、デフラグのコピー元とコピー先と、コピー先フラグと、命令と、命令の対象アドレスとに基づいて、参照または更新の命令の対象アドレスを再決定するか、CPUに失敗を通知する。

(もっと読む)

情報処理装置、初期化要求機構、及び、テレビ受像機

【課題】不揮発回路と揮発回路が混在するシステムにおいて、初期化が必要な揮発回路の存在を不揮発回路に通知する初期化要求機構を提供する。

【解決手段】初期化要求機構は、電源検知部とレジスタとを備える。電源検知部は、揮発回路によって構成される周辺回路を駆動する電源がオフになったことを検知すると、電源がオフになったことを示すレジスタ値をレジスタに記録する。初期化要求機構は、レジスタに、少なくとも一つ以上の電源がオフになったことを示すレジスタ値が記録されている場合、周辺回路の初期化が必要であることを示す初期化要求割込を、不揮発回路によって構成されるプロセッサに送信する。プロセッサは、初期化要求割込を受信すると、プロセッサが保持しているプロセスの実行状態に合わせて周辺回路を起動する。

(もっと読む)

半導体記憶装置、ホスト機器及び半導体記憶システム

【課題】半導体記憶装置において、電源断や書き込みエラーで既に書き込みを完了していたセル共有部分のデータが破壊されないようにすること。

【解決手段】ホスト機器200Aにデータバッファ250を備える。既に物理ブロックの一部にデータが書き込まれており、更にその物理ブロックにデータを書き込む際に、データバッファにその物理ブロックの書き込み済みのデータが保持されているかどうかを識別する。データが保持されている場合にはそのまま書き込み、エラーがあれば物理ブロック単位での再書き込みを行う。又データバッファにデータが保持されていない場合には、新物理ブロックの確保を要求した後にデータの書き込みを行う。こうすれば、書き込み途中に電源が遮断されたりエラーが生じても、以前に書き込みを完了していたデータが破壊されることはなくなる。

(もっと読む)

キャッシュメモリバックアップ装置、方法およびプログラム

【課題】主電源からの電力の供給が停止した場合におけるキャッシュメモリに格納されたデータを退避するのに要する時間を削減することによりバックアップ電源の容量を削減するとともに、バックアップ電源のメンテナンスを容易化すること。

【解決手段】キャッシュメモリバックアップ装置は、揮発性のキャッシュメモリと、キャッシュメモリと同一又はそれ以上の容量を有し、キャッシュメモリに格納されたデータを退避するための不揮発性メモリと、キャッシュメモリに対する主電源からの電力の供給が停止した場合にキャッシュメモリ及び不揮発性メモリに電力を供給するキャパシタとを備える。

(もっと読む)

メモリシステム

【課題】不正な電源断を簡便かつ確実に検出することが可能なメモリシステムを提供する。

【解決手段】システム起動後最初の差分ログがNANDログ203に記録される前に、システムが動作中であることを示すActiveログをNANDログ203に記録し、正常なシステム停止時に、システムが停止することを示すStandbyログを差分ログに続いてNANDログ203に追記記録し、システム起動時、NANDログ203内のActiveログおよびStandbyログの記録状態に基づき、前回正常なシステム停止が行われたか不正な電源断が行われたかを判断する。

(もっと読む)

情報記録装置、半導体記憶装置のファイル管理方法

【課題】使用可能なデータ領域を確保しつつ、ファイルの書き込み処理中に電力供給が中断された場合であってもファイルの破壊を回避可能な半導体装置のファイル管理方法及び情報記録装置を提供する。

【解決手段】本発明の情報記録装置4は半導体装置3とファイル管理装置2を有する。半導体装置3は複数のブロックを有するデータ領域13と、データ領域の管理情報を格納するシステム領域11、12と、システム領域の管理情報を更新するための更新管理情報を一時的に記憶する書き込み情報保留領域14と、を備える。ファイル管理装置2は、データ領域の空きブロックに更新ファイルを書き込み、更新ファイルの書き込み後の更新管理情報を書き込み情報保留領域に書き込み、書き込み情報保留領域に書き込まれている更新管理情報に基づきシステム領域の管理情報を更新し、書き込み情報保留領域の更新管理情報を削除する。

(もっと読む)

不揮発性記憶装置、情報記録システム、及び情報記録方法

【課題】管理情報へのアクセス集中やメモリ特性の悪化に対して、メディア内で管理情報をユーザデータよりも安全に記録、保存し、データエラーを防ぐようにする。

【解決手段】ホスト装置から入力される前記ユーザデータ及び前記管理情報に対する処理内容を記述したコマンドを受信し、前記受信したコマンドがいずれに対するものであるかを判別する。その判別の結果に応じて、前記ユーザデータ及び該ユーザデータをファイルシステム上で管理するための管理情報を記憶する不揮発性メモリ手段に対する制御方式を切り換える。そして、切り換え後の制御方式に従い、前記ユーザデータ又は前記管理情報を前記不揮発性メモリ手段に記録する。

(もっと読む)

半導体集積回路、半導体集積回路の内部状態退避回復方法

【課題】内部状態の退避および回復時の時間を短縮し、消費電力を削減する。

【解決手段】スキャンチェーンは、スキャンパステストのときに、第1回路に含まれる複数の第1フリップフロップと、第2回路に含まれる複数の第2フリップフロップとを鎖状に接続してシフトレジスタとして動作する。バックアップ制御回路は、第1フリップフロップに保持される内部状態を示すデータを、第2フリップフロップをバイパスしたスキャンチェーンを介してメモリ回路に格納する退避動作と、メモリ回路から内部状態を示すデータを読み出して第2フリップフロップをバイパスしたスキャンチェーンを介して第1フリップフロップに再設定する回復動作とを制御する。入力選択回路は、スキャンパステストのテストデータと、メモリ回路から読み出した内部状態を示すデータとのうちの一方を選択してスキャンチェーンに供給する。

(もっと読む)

半導体メモリ装置

【課題】不揮発性メモリにおける電源遮断時の異常を迅速に解消できるようにする。

【解決手段】半導体メモリ装置1を、フラッシュメモリ等の不揮発性メモリ2と、データの書き込みおよび消去等の制御を行う制御部3と、データの入出力を行うためのインタフェース4とにより構成する。不揮発性メモリ2の記憶領域を第1および第2のバンクB1,B2に分け、各バンクB1の状態を表すフラグをバンクB2に、バンクB2の状態を表すフラグをバンクB1に書き込む。

(もっと読む)

不揮発性記憶媒体書込み回路、不揮発性記憶媒体書き込み方法、及びプログラム

【課題】一連の情報を書き込んでいる途中でAC電源が遮断された場合であっても、電源ユニットの仕様や、負荷の大小によらず、不正値の書き込みを防止する。

【解決手段】制御部7は、一連の情報を一旦データバッファ8に格納し、データバッファ8への一連の情報の書込み完了後、供給電源遮断検出回路4により供給電源の遮断が検出されれば、不揮発性メモリ9への書込みを停止し、不正値が書き込まれるを防止する。一方、供給電源遮断検出回路4により供給電源の遮断が検出されていなければ、データバッファ8の内容を全て不揮発性メモリ9に書き込む。このとき、不揮発性メモリ8への書き込み中に電源ユニット2からの供給電源が遮断されても、蓄電回路5に蓄電されている電力が供給されるので、不揮発性メモリ9には一連の情報が全て書き込まれる。

(もっと読む)

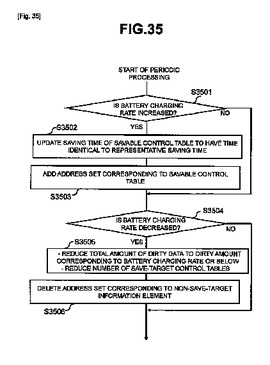

揮発性メモリと不揮発性メモリとを備えたストレージシステム

【課題】揮発性メモリにおける退避対象を確実に不揮発性メモリに退避できるようにする。退避処理に要する時間をなるべく短くする。

【解決手段】バッテリの充電状況が定期的又は不定期的に把握され、把握された充電状況に応じて、揮発性メモリに記憶されているどの情報要素を、電断発生時の退避対象とするかが制御される。揮発性メモリに記憶されている複数の情報要素のうち特定の情報要素が、その特定の情報要素に関する状況に応じて、退避処理の際の非退避対象とされる。

(図35)  (もっと読む)

(もっと読む)

売上データ処理装置及びプログラム

【課題】売上データ処理装置において、主電源遮断時のデータのバックアップに使用される補助電源の消耗を低減させる。

【解決手段】本発明に係るECRによれば、CPU10は、他に実行すべき処理のない空き時間にハイバネーション用メモリ14に記憶されているデータの消去処理を実行し、AC電源31からの電源供給が遮断された際に、補助電源からの給電によりハイバネーション用メモリ14に記憶されている未消去の残存データの消去処理を実行しメインメモリ13に記憶されているデータをハイバネーション用メモリ14に退避させる。

(もっと読む)

情報処理システム、システムコントローラ及びメモリ制御方法

【課題】XDR DRAMを用いた情報処理システムにおけるSTR処理の所要時間を短縮する。

【解決手段】XDR DRAM13はRST(リセット)信号入力に応じてデータリセットを行うDRAMである。システムコントローラ11は、システムの初回の電源投入の際に、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13に対してリセット信号を出力し、XDR DRAM13をリセットする。XDR DRAMに格納されたデータを保持したままシステムの電源を切る場合、システムコントローラ11は、メモリコントローラ12からレベルシフタ24を介して入力されるRST信号に応じて、XDR DRAM13の電源投入を維持しながら、メモリコントローラ12の電源を切る。

(もっと読む)

101 - 120 / 333

[ Back to top ]