Fターム[5B018QA05]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 稼働時 (637) | 電源異常時、電源切断時 (333)

Fターム[5B018QA05]に分類される特許

81 - 100 / 333

記憶媒体

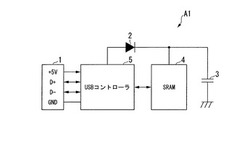

【課題】データの漏えいを防止できる安価な記憶媒体を提供する。

【解決手段】記憶媒体が、コンデンサと、コンデンサに蓄えられた電力を基にデータを記憶する揮発性メモリとを具備する。コンピュータのUSBポートにUSBメモリが装着されると、USBコントローラ5は、USBコネクタ1を介してコンピュータから電力を受け取り、当該電力をコンデンサ3及びSRAM4に供給する。そして、コンピュータのUSBポートからUSBメモリが取り外されると、コンデンサ3は、SRAM4への電力の供給を開始する。SRAM4は、コンデンサ3から電力が供給されている間データを継続して記憶するが、コンデンサ3の電力がなくなると電力の供給が停止するので、記憶しているデータが消える。

(もっと読む)

情報処理方法、情報処理装置、およびプログラム

【課題】メモリコラプションに対処しつつ、データの書込み処理に要する時間を短縮する。

【解決手段】ステップS34では、データ領域の全ての更新ブロックの物理ブロック番号が参照されてデータ領域の更新ブロックとして認識される。そして、ステップS35で、データ領域の更新ブロックとして認識された全ての物理ブロックが一括して消去される。これにより、物理ブロックにデータを書込み毎に消去する場合に比較して、処理時間を短縮することができる。本発明は、EEPROMのように、データを書き込む場合、記録領域に既に記録されているデータに上書きすることができず、既に記録されているデータを消去してから新たなデータを記録しなければならない記録媒体に対して、データを書き込む場合に適用することができる。

(もっと読む)

電子制御装置

【課題】バックアップ対象となる情報が多いシステムにおいても、データ破壊に対する検出精度が高く、かつ局所的な処理負荷増大を防止した形で、データの損失を抑えた電子制御装置を提供する。

【解決手段】主電源復帰時に、中央演算処理装置10は、揮発性メモリ11が記憶したバックアップデータのSUM値を算出して、このSUM値を主電源遮断時に同様に算出したSUM値と比較し、一致しない場合であっても揮発性メモリ11の固有データと不揮発性メモリ12の固有データとが一致する場合、バックアップデータを初期化せずに保持する。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】全消去検出回路の出力と書き込みマークの有無に基づいて書き込み状態を制御回路によって判定することによって、正確に書き込み途中の電源遮断等の異常を検出することのできる信頼性の高い不揮発性記憶装置及びその書き込み判定方法を提供する。

【解決手段】不揮発性メモリから書き込み単位のデータを読み出す際に、全消去検出部によって読み出しデータが消去済みであるかどうかを判定すると共に、デスクランブル処理部によりデスクランブルされさらに誤り検出訂正部によって誤り訂正を行った後のデータの書き込み済みフラグ領域がフラグ書き込み済みであるかどうかを判別し、スクランブルパターン発生部によって生成される前記書き込み済みフラグ領域に対応するスクランブルパターンが、前記所定のビットパターンを消去済みの状態とは異なる状態にスクランブルする。

(もっと読む)

電力損失を制御するための方法及びデバイス

【課題】不揮発性メモリを有するデバイスにおける電力損失を制御するための方法及び装置を提供すること。

【解決手段】電力損失を制御するための方法及びデバイスがここに説明される。1つの実施形態において、この方法は、コントローラにより制御された電力遮断コマンドを出すことを含む。この方法は、メモリデバイスがバックグラウンド動作を実行しているかどうかを判断することを含む。この方法は、メモリデバイスがバックグラウンド動作を実行している場合に、バックグラウンド動作を安全に一時停止すること、又は、バックグラウンド動作を完了することを含む。この方法は、供給電力を安全に除去することを含む。

(もっと読む)

記憶装置、データ処理方法およびデータ処理プログラム

【課題】復電処理中に停電が発生した場合に、キャッシュデータのロストを精度よく防止することを課題とする。

【解決手段】復電処理内のイレース実行中に停電が発生した場合には、イレースを中断させる。そして、イレースが中断されるまでの間にフラッシュメモリ230から消去されたバックアップデータに対応するキャッシュメモリ220内のデータを、イレースにより消去されなかったバックアップデータが書き込まれているフラッシュメモリ230内の最終ブロックの次ブロックからリード転送(再バックアップ)する。

(もっと読む)

記憶装置、データ保存方法およびデータ保存プログラム

【課題】復電処理中に停電が発生した場合に、キャッシュデータのロストを精度よく防止する。

【解決手段】復電処理におけるフラッシュメモリのイレース実行中に停電が発生した場合には、イレースを停止させる。イレースを停止した時点で、フラッシュメモリが有するテーブル域(制御情報記憶域)の途中までイレースが進んでいる場合には、テーブル域の全域を消去する。テーブル域の全域の消去が完了した後、テーブル域から消去されたデータをキャッシュメモリからフラッシュメモリへ再退避する。また、イレースを停止した時点で、フラッシュメモリが有するキャッシュ域までイレースが進んでいる場合には、フラッシュメモリからイレースされたデータをキャッシュメモリからフラッシュメモリへ直ぐに再退避する。

(もっと読む)

共通論理ブロックに関連付けられている物理ブロックを解決するための方法および装置

【課題】論理ブロックに関連付けられている複数の物理ブロックのうちどれが、より最近に論理ブロックに関連付けられた物理ブロックであるかを判定する。

【解決手段】判定する方法は、第1の物理ブロックに関連付けられている第1の識別子を取得するステップおよび第2の物理ブロックに関連付けられている第2の識別子を取得するステップを含む。これらの識別子を比較して、前記第1の物理ブロックがより最近に論理ブロックに関連付けられたことを第1の識別子が示すかどうかを確認する。この方法は、さらに、第1の識別子が、その第1の物理ブロックがより新しく論理ブロックに関連付けられたことを示すと判定されたときに論理ブロックに関連付けられている内容を第1の物理ブロックに供給するように構成されたオペレーションを完了するステップを含む。

(もっと読む)

セルフリフレッシュ・モードのためのメモリ・デバイス制御

【課題】セルフリフレッシュ・モードのためのメモリ・デバイス制御を提供する。

【解決手段】メモリ回路において、メモリ・コントローラがパワーダウンおよびパワーオフされている間、DDR3 RDIMMなどのメモリ・デバイスがセルフリフレッシュ・モードで安全に動作することを保証するために、メモリ・デバイスのクロック・イネーブル(CKE)入力が、(i)メモリ・コントローラによって印加されたCKE信号と、(ii)パワー・モジュールによって供給された終端電圧の両方に接続される。メモリ・コントローラをパワーダウンするために、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは終端電圧をローに駆動し、パワー・モジュールはメモリ・コントローラをパワーダウンする。通常の動作を再開するために、パワー・モジュールはメモリ・コントローラをパワーアップし、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは、終端電圧をパワーアップする。

(もっと読む)

電子機器制御装置及びそれを備えたテレビジョン受信装置

【課題】メモリへのデータ書き込み中に電源遮断が発生したか否かを確認できる電子機器制御装置を提供する。

【解決手段】電子機器制御装置20の書き換え可能な不揮発性メモリ19には、通常データ領域191と、書き込み開始データ領域192と、書き込み終了データ領域193と、書き込み中断データ領域194と、が備えられる。電子機器制御装置20の制御手段18は、起動時に、書き込み開始データ領域192及び書き込み終了データ領域193から読み出した2つのデータに基づいて、保存すべきデータの通常データ領域191への書き込み処理中に処理が中断されたことを示す書き込み中断データを書き込むか否かを判断する処理を行うと共に、前記書き込み中断データを書き込むと判断した場合に書き込み中断データ領域194に前記書き込み中断データを書き込む処理を行う。

(もっと読む)

車両の制御装置及び制御方法

【課題】バッテリによりバックアップされたメモリに格納されたデータが消失する可能性がある場合に、確実に初期化できる車両の制御装置

【解決手段】SRAM11aと、電源スイッチがオンされた後にバッテリから給電されて起動し、SRAMをモニタして記憶状態が適正であるか否かを判定するSRAMモニタ処理と、SRAMの記憶状態が適正でない場合にSRAMを初期化する初期化処理と、を実行する第一のマイクロコンピュータと、バッテリから常時給電され、電源スイッチがオンされたことを検知するとバッテリから第一のマイクロコンピュータに給電するための給電制御信号を出力する給電制御処理と、起動時にのみ第一のマイクロコンピュータにSRAMを初期化する初期化処理を実行させるための初期化制御信号を出力する初期化処理と、を実行する第二のマイクロコンピュータ12と、を備える制御装置。

(もっと読む)

コンテンツ再生装置

【課題】記憶部に対する履歴情報の書込み回数を低減するとともに、例えば突然の電源遮断の発生や時間計測回路の計時誤差が補正された場合でも、正確な履歴情報を記憶部に記憶させることの可能なコンテンツ再生装置を提供する。

【解決手段】表示部11又は音声出力部15にコンテンツ情報が再生される毎に該コンテンツ情報の履歴情報をそれぞれ記憶する不揮発性記憶部13a及び揮発性記憶部16aと、揮発性記憶部16aに記憶された複数の履歴情報を所定のタイミングで記憶部12に記憶させるとともに、記憶部12に記憶された履歴情報より新たに記憶された履歴情報が不揮発性記憶部13aに存在する場合に、該新たに記憶された履歴情報を不揮発性記憶部13aから取得して記憶部12に記憶させる制御部16とを備えた。

(もっと読む)

データ処理装置、データ処理方法、及びデータ処理プログラム

【課題】データ書込み中のデータに誤りが発生する現象をできる限り救済することができるデータ処理方法等を提供する。

【解決手段】CPU201は、相変化メモリ202及びフラッシュメモリ203に記憶されるデータに対して管理番号、及び、前記入力されるデータの存在を示す符号としての「データあり」を付与し、第一のデータに関する情報として、管理エリア1(301)に記憶し、「データあり」が付与された場合に、前記データと同一のデータを、相変化メモリ202に、データの正当性を示す検証値と共に記憶し、前記第一の記憶手段によって前記データが記憶された場合に、フラッシュメモリ203に当該データと同一のデータを記憶し、フラッシュメモリ203に当該データと同一のデータが記憶された場合に、新たな前記データに関する情報として、前記第一のデータに関する情報に示される管理番号と同一の管理番号、及び、終了フラグNを付与し、第二のデータに関する情報として記憶する。

(もっと読む)

データバックアップ方法及び情報処理装置

【課題】データバックアップ方法及び情報処理装置において、複数系統のデータバックアップ時間に差が生じても、データバックアップ処理を短時間に完了可能とすることを目的とする。

【解決手段】第1の記憶部から第2の記憶部へ転送する総データサイズに相当する前記第1の記憶部内の記憶領域をN(Nは自然数)分割して同サイズのN個の分割領域に対して2N個の第2の記憶部を用意し、各分割領域に対して用意した2個の第2の記憶部の一方には当該分割領域の先頭アドレスから最終アドレスの方向へ順次データをバックアップすると共に、他方には当該分割領域の前記最終アドレスから前記先頭アドレスの方向へ順次データをバックアップし、各分割領域に対するデータのバックアップを、当該分割領域内の全てのアドレスのデータを前記2個の第2の記憶部にバックアップした時点で終了し、前記N個の分割領域に対するデータのバックアップが終了した時点で前記総データサイズのデータのバックアップ処理を完了するようにする。

(もっと読む)

電子機器およびプログラム更新方法

【課題】更新途中で電源が遮断されても電源復帰後に更新を完結させるプログラム更新機能の信頼性を高める。

【解決手段】電子機器に組み込まれたプログラムを部分的に変更するプログラム更新に際して、電子機器が第1電源からの電力によって作動可能な状態において、プログラムの一部であるブロックを差分データに基づいて書き換えるとともに、書換えの進行段階を示す情報を第2電源およびメモリを有しかつ第2電源からの電力によってメモリに対するリードライト動作をするメモリ回路によって記憶し、第1電源からの電力供給の停止に伴って中断された前記プログラムの一部の書換えを、第1電源からの電力供給が再開されたときに、メモリ回路が記憶する情報に基づいて、未完の段階から再開する。

(もっと読む)

記憶装置システムの論理ブロックアドレス割り当て解除管理およびデータハードニング

【解決手段】 記憶装置システムの論理ブロックアドレス(LBA)割り当て解除管理およびデータハードニングを行うことにより、当該システムの性能、効率、および実用性が改善される。選択的に、(例えば、第1のプロトコルに関連付けられた)第1のフォーマット形式のLBA割り当て解除情報は、(例えば、第2のプロトコルに関連付けられた)第2のフォーマット形式に変換される。前記第1のプロトコルの一例はスモール・コンピュータ・システム・インターフェース(SCSI)プロトコルであり、前記第2のプロトコルの一例はアドバンスド・テクノロジー・アタッチメント(ATA)プロトコルである。選択的にLBA割り当て解除ステータス情報はソリッドステートディスク(SSD)などの記憶装置により決定され、イニシエータ、エクスパンダ、またはブリッジなど別の装置に通信される。選択的にSSDに格納されたデータは、例えばSSDの電源がオフになるという決定に応答してハードニングされる。このハードニングは、スーパーキャパシタまたは電池などのエネルギー貯蔵要素から供給される電力により行われる。

(もっと読む)

データ装置

【課題】バッテリ切れに起因して、メディア記録動作が異常終了した際に、メディアの記録状態を保護することができないという課題がある。

【解決手段】外部装置151との間で操作命令を送受信する送受信部102と、駆動バッテリの残容量を検出する残容量検出部107と、記録媒体106へのアクセスを制御する記録媒体制御部103と、記録媒体106上のデータ管理情報領域を判別する管理情報領域判別部104と、駆動バッテリの残容量が所定の閾値以下となった場合において、受信した書込命令中の書込対象アドレスがデータ管理情報領域の場合は、書込命令を実行してその結果を送信し、データ管理情報領域以外の場合は、書込命令を実行せず、外部装置151に対して書込命令を受け付けない旨の応答を送信する制御部110と、を備える。

(もっと読む)

不揮発性メモリを用いた記憶装置

【課題】バッファメモリのライトデータを、複数の不揮発性メモリデバイスを並列にアクセスして書き込む記憶装置に関し、電源遮断時のデータ消失を防止する。

【解決手段】複数の書き込み可能な不揮発性メモリデバイス(3−1〜3−16)を並列にアクセスするメモリコントローラ(2)が、電源遮断時に、特定の不揮発性メモリデバイス(3−A)のみを書き込み対象にし、バッファメモリ(18−1)から、不揮発性メモリデバイス(3−A)に書き込むデータを、書き込み済みでないライトデータに絞り込むことで、書き込み時に消費する電力を、抑えることが可能になる。

(もっと読む)

非接触型携帯可能電子装置および非接触型ICカード

【課題】メモリへのデータ書込みの途中にエラーが発生しても、データ書込みを最初からやり直す必要がなく、書込みデータ長によっては大幅な処理時間の短縮効果が期待できる非接触型携帯可能電子装置および非接触型ICカードを提供する。

【解決手段】非接触型カードリーダ・ライタから送信される電磁波を受信し、この受信した電磁波により動作電圧を生成して動作するもので、非接触型カードリーダ・ライタから送信される書込みコマンドに基づき不揮発性メモリにデータを書込む処理を行ない、その処理結果を非接触型カードリーダ・ライタへ送信する非接触型ICカードにおいて、不揮発性メモリに対するデータの書込み途中にエラーが発生し、書込みが途中まで正常に終了していた場合、その旨のレスポンスに、正常に書込みが終了したデータの長さ、書込みが終了していないデータの長さ、メモリの書込みに失敗したアドレスのうち少なくともいずれか1つを示すデータを付加して非接触型カードリーダ・ライタへ送信する。

(もっと読む)

不揮発メモリ装置、不揮発メモリの書込み方法、及び不揮発メモリ書込みプログラム

【課題】不揮発メモリの書込みエラーが発生しても、トータルの処理時間を変えずに、書込み処理を完了させることができるようにする。

【解決手段】共通のデータバス及びアドレスバスに、特性の異なる第1の不揮発メモリ(MLC−NANDメモリ)102と第2の不揮発性メモリ素子(SLC−NANDメモし)103が接続されている。二重化書込み回路106は、CPU101からの二重化信号(イネーブル信号)に基づいて、第1の不揮発メモリ102と第2の不揮発性メモリ素子103を同時に選択し、第1の不揮発メモリ102へデータを書込むときに、第2の不揮発性メモリ素子103へ二重化したデータを書込む。

(もっと読む)

81 - 100 / 333

[ Back to top ]