Fターム[5B018QA05]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 稼働時 (637) | 電源異常時、電源切断時 (333)

Fターム[5B018QA05]に分類される特許

61 - 80 / 333

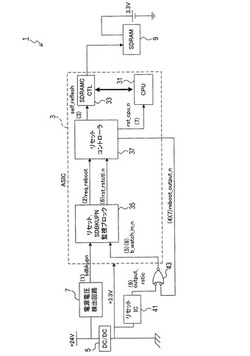

メモリ制御装置

【課題】セルフリフレッシュ機能を有するメモリを制御するメモリ制御装置において、電源電圧が低下した場合でも、メモリの記憶内容を正確に保持すること。

【解決手段】+24Vの電源電圧が低下すると、検出信号sdbkupnがHIGHとなり(1)、それに応じてリブート信号req_rebootがHIGHとなる(2)。すると、信号self_refleshがHIGHとなり(3)、SDRAMコントローラ33を介してSDRAM9にセルフリフレッシュ動作が指示される。また、リブート信号req_rebootに応じて信号reboot_output_nもLOWとなる(4)。すると、信号b_watch_in_n,信号rst_rstctl_n,信号rst_cpu_nが順次LOWとなって、監視ブロック35,リセットコントローラ37,CPU31が順次リセットされる。

(もっと読む)

記憶装置

【課題】メモリの負担軽減化を図ることができる記憶装置を提供すること。

【解決手段】制御部46は、ユーザデータをユーザデータ用ブロックに書き込みを開始する時、管理用ブロックの第1ページに第1フラグを書き込み、ユーザデータの書き込みが終了した場合に、第1ページとは異なる第2ページに第2フラグを書き込む。制御部46は、第1ページ及び第2ページにそれぞれ第1フラグと第2フラグが書き込まれている場合には、当該第1フラグに対応するユーザデータがユーザデータ用ブロックに正常に書き込まれていると判断して、当該ユーザデータが書き込まれているブロックに対して消去処理を行わず、第1ページには第1フラグが書き込まれているものの、第2ページには第2フラグが書き込まれていない場合には、当該第1フラグに対応するユーザデータがユーザデータ用ブロックに正常に書き込まれていないと推定する。

(もっと読む)

データ記憶装置及びデータ記憶方法

【課題】電源の瞬断が発生した場合であっても、データの消失又は破損等が生じることがないデータ記憶装置及びデータ記憶方法を提供する。

【解決手段】データがそれぞれ一括消去される複数の記憶ブロックに対してメモリ管理部21が順次的にデータを書き込み、データの書き込み先を変更する際には有効なデータを次のブロックへコピーするブロック更新処理を行う。最初に書き込みを行う第1記憶ブロック221には、記憶ブロック毎に更新開始ビット、更新終了ビット及び消去終了ビットの3つの情報を管理情報として記憶しておく。メモリ管理部21はブロック更新処理の開始前に更新開始ビットをデータ’0’に設定し、ブロック更新処理の終了後に更新終了ビットをデータ’0’に設定する。またメモリ管理部21は、更新終了ビットがデータ’0’に設定された記憶ブロックの消去処理を行い、消去処理の終了後に消去ビットをデータ’0’に設定する。

(もっと読む)

マイクロコンピュータ及び車両

【課題】データを不揮発性メモリに書き込む際、不揮発性メモリへの書き込み回数の増加を抑制することのできるマイクロコンピュータ及び車両を提供する。

【解決手段】複数のセルを電気的に接続した組み電池とセルの状態を計測する監視回路とを有する電池パックを備えた車両に搭載される、スタティックRAM31を有するマイクロコンピュータ30であって、監視回路から複数の計測した情報をそれぞれの周期で取得し、所定期間の情報を管理情報として編集してスタティックRAMに書き込む際、このスタティックRAMに必要な空き領域が不足しているときは、新たに編集した管理情報と既に保存されている管理情報とを不揮発性メモリに書込む動作を実行し、車両がイグニッションオフされた際は、計測した情報を取得するそれぞれの周期をイグニッションオンのときよりも長い周期で実行するようになされたマイクロコンピュータである。

(もっと読む)

バックアップ制御装置、バックアップ制御方法及びコンピュータプログラム

【課題】より少ない消費電力によって、不揮発性デバイス書き込み方式によるバックアップ処理を可能とすること。

【解決手段】バックアップ制御装置であって、キャッシュデータを格納するメモリと、不揮発性であり、キャッシュデータの全てを格納可能な容量を有する不揮発性メモリと、メモリに格納されたキャッシュデータをバックアップする場合に、メモリに格納されたキャッシュデータを読み出し、読み出したキャッシュデータを不揮発性メモリに書き込む演算部と、を備え、メモリは、演算部がキャッシュデータを不揮発性メモリに書き込みを行っている間は、セルフリフレッシュモードで動作することを特徴とする。

(もっと読む)

制御装置及びこれを備えた電子機器、認証処理装置

【課題】 制御データの安定性を担保して、安定的な動作制御の実現を可能にした制御装置を提供する。

【解決手段】 設定レジスタ13は、ドライバ4,5に対して行われる制御内容に対応したオリジナル制御データ7AをROM7から取得し、設定済制御データとして登録する。誤り検出検査符号作成回路15は、設定済制御データに基づき所定の規則に従って設定済誤り検出検査符号を作成する。比較回路16は、ノイズ検出回路14において設定レジスタ13の電源用電圧が所定の許可条件を逸脱する変動をした場合には、オリジナル制御データ7Aに基づいて前記所定の規則に従って作成されたオリジナル誤り検出検査符号7BをROM7から読み出し、前記設定済誤り検出検査符号との比較を行う。設定レジスタ13は、前記両符号に齟齬が存在すればオリジナル制御データ7Aを改めてROM7から取得して設定済制御データとして再登録する。

(もっと読む)

ディスクアレイ装置およびその制御方法

【課題】 復電時から業務再開までの時間を短縮すること。

【解決手段】 停電時に、メモリコントローラ70は、共有メモリ46のシステム構成情報とディレクトリ情報を不揮発性メモリ32に退避させ、キャッシュメモリ44のデータを不揮発性メモリ32に退避させる。停電からの復電時に、メモリコントローラ70は、イニシャライズ時間が経過するまでの間に、不揮発性メモリ32の情報を共有メモリ46に戻して更新可能とし、マイクロプロセッサ38は、共有メモリ46の情報を基にオンライン処理を実行し、イニシャライズ時間が経過しても、バッテリ36のバッテリ容量が徐々に上昇している過程では、メモリコントローラ70は、バッテリ36のバッテリ容量に応じて、キャッシュメモリ44の記憶領域を段階的に書き込み可能に制御する。

(もっと読む)

記憶装置

【課題】揮発性メモリからアドレステーブルが消失された場合であっても、予備ブロックに対してデータのアクセスを行うことができる記憶装置を提供すること。

【解決手段】データブロック領域と予備ブロック領域とを備える不揮発性メモリ44bと、不良ブロックの先頭アドレスと当該不良ブロックを代替する予備ブロックの先頭アドレスとを対応させて構成されるアドレス対を記憶する揮発性メモリ44aと、アドレス対を参照することによって不良ブロックに代替された予備ブロックにアクセスする制御部45と、を備える。制御部45は、揮発性メモリ44aからアドレス対が消失している場合、予備ブロック領域へアクセスし、予備ブロックの先頭アドレスと当該予備ブロックに記憶されている不良ブロックの先頭アドレスを読み出し、予備ブロックの先頭アドレスと不良ブロックの先頭アドレスのアドレス対を生成し、生成したアドレス対を揮発性メモリ44aに記憶する。

(もっと読む)

ソリッド・ステート・ドライブ装置および平準化管理情報の退避・回復方法

【課題】大容量の平準化管理情報を短時間のうちに不揮発性メモリに退避させることを可能にする。

【解決手段】平準化管理情報記憶部13は、レーン接続バス30を介して8つのレーン21それぞれに含まれるバッファ記憶制御部22のBM220に接続され、各レーン21には、バッファ記憶制御部22とNVMチップ23とを接続するチップ接続バス24が設けられている。各レーン21のバッファ記憶制御部22は、平準化管理情報退避・回復処理部14の指示のもとに、平準化管理情報記憶部13から転送される退避データを、チップ接続バス24を介して、互いに独立に並行してNVMチップ23へ転送する。その退避データの中には、平準化管理情報だけでなく、その平準化管理が平準化管理情報記憶部13に記憶されていたときの先頭アドレスが含まれている。

(もっと読む)

記憶装置と半導体不揮発性メモリの記憶方法

【課題】不揮発性メモリのランダムライトアクセスの高速化を図る。

【解決手段】半導体不揮発性メモリは、複数の消去単位からなる初期割当領域及び初期未使用領域を有する。ホスト側論理アドレスが順次に並ぶ最小管理単位を設定し、入力されたデータをバッファに順次に書き込み、最小管理単位毎の論理アドレスと不揮発性メモリの物理アドレスとのアドレスの変換情報を生成する。バッファの全記憶容量に対して書き込まれたデータを、書き込み予定の第1の消去単位の未書き込み領域に順次に書き込む。第1の消去単位の未書込領域がなくなると、検索された第2の消去単位の有効データを予め準備されている消去済等の第3の消去単位に書き込んで変換情報を更新して新第1の消去単位に置き換える。第2の消去単位を一括消去して新第3の消去単位の生成準備と並行して新第2の消去単位を検索する。

(もっと読む)

半導体記憶装置

【課題】データの消去動作中に電源供給が遮断された場合でも、メモリブロックのデータの消去が正常に行われたか否かの判定を正しく行うことができる半導体記憶装置を提供する。

【解決手段】メモリブロックと異なる消去単位であり、記憶されたデータを消去するメモリブロックのアドレス値を表すアドレス情報と、該メモリブロックの消去動作の状態を表すフラグ情報とを関連付けて記憶する情報格納手段と、メモリブロックに対して消去動作を行う前に、消去動作を行うメモリブロックのアドレス値をアドレス情報に設定するとともに、該アドレス値に関連付けられたフラグ情報に第1の値を設定し、メモリブロックに対する消去動作が完了した後に、該メモリブロックのアドレス値に関連付けられたフラグ情報に第1の値と異なる第2の値を設定する設定手段と、フラグ情報に基づいて、メモリブロックの消去動作が正常に完了したか否かを判定する判定手段と、を備える。

(もっと読む)

フラッシュディスク装置

【課題】データ書き込みの途中で電源が落ちた場合などでも、不完全な書込みデータによりデータ領域が壊れたままの状態とならないようにする。

【解決手段】物理チャンクごとに、データ領域の誤り訂正を行う誤り訂正符号と、物理チャンクに対応する論理チャンクと、書き換えたデータの新旧を表わす更新番号を格納する管理データを備えたフラッシュメモリ21と、前記論理チャンクと物理チャンクを対応付けるアドレステーブル30を格納する不揮発性メモリ12と、前記フラッシュメモリおよび不揮発性メモリを制御する制御手段11と、を備え、起動時のアドレステーブル30の再構成時の処理のときに、前記物理チャンクのデータ領域の誤り訂正処理を行って誤りがない場合のみ、前記アドレステーブル30に同じ物理チャンクがあるときはそれぞれの前記更新番号により新しい番号の物理チャンクにてアドレステーブル30を更新するようにした。

(もっと読む)

車載制御装置

【課題】不揮発性記憶手段へのデータ書き込みが異常となった場合であっても、最新のデータの読み出しを行い、商品性および信頼性の向上を図ることができる車載制御装置を提供する。

【解決手段】EEPROMのバンク2aと、バンク2bとの記憶データを比較し、一致しないと判定されたバンク2aの記憶データのうち、関連性を有さないと判定された記憶データを最新データとしてRAMに読み出す一方、一致しないと判定されたバンク2aの記憶データが関連性を有すると判定された場合であっても、関連性を有すると判定された全ての記憶データが一致しないと判定された場合には、関連性を有すると判定されたバンク2aの記憶データを最新データとしてRAMに読み出すことを特徴とする。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】不揮発性メモリの領域を効率良く使用し、使用領域を小さくして、コストおよび実装面積を低減するデータ処理装置およびデータ処理方法を提供すること。

【解決手段】データ処理プログラムを書き換え可能であるとともに、このデータ処理プログラムによって用いられるデータを、一方の領域と他方の領域に2重に記憶する記憶手段40を有するデータ処理装置100において、データ処理プログラムの書き換え前後で、記憶手段40の一方の領域と他方の領域とを切り換える制御手段110を備えたことを特徴とするもの。

(もっと読む)

マルチプロセッサシステム

【課題】キャッシュ状態のバックアップ時の電力消費を低減するマルチプロセッサシステムを提供することを課題とする。

【解決手段】キャッシュをそれぞれ備える複数のプロセッサを有し、システム停止時に各プロセッサのキャッシュの状態を外部記憶装置に順次保存するマルチプロセッサシステムであって、複数のプロセッサへの給電を管理する給電管理手段を備え、給電管理手段は、システム停止時に、複数のプロセッサの任意のプロセッサのキャッシュの状態の外部記憶装置への保存が完了する毎に、任意のプロセッサの次にプロセッサのキャッシュの状態を保存するプロセッサのキャッシュの状態の外部記憶装置への保存が完了する前に、任意のプロセッサへの給電を停止することを特徴とする。

(もっと読む)

車載電子制御装置およびメモリ制御方法

【課題】冗長性を持たせつつ、かつフラッシュROMにデータを即時記憶させる場合であっても、必要なブロック数の増加を抑制する、あるいは低減する

【解決手段】2つのブロックBL−A,BL−Bを内蔵したフラッシュROM5を有し、車載電子制御装置1の電源オン時に、ブロックBL−A,BL−Bの中から選択されたブロック(以下、第1ブロックともいう)の第1記憶領域MR1に記憶されている記憶データをRAM4に記憶させる。その後に、MIL22が点灯すると、MIL22に対応する永久故障コードを、RAM4の第1記憶領域MR3内の永久故障コード記憶領域MRPと、第1ブロックの第1記憶領域MR1とは別に予め設けられた第2記憶領域MR2に記憶させる。そして、車載電子制御装置1のシャットダウン時に、RAM4の第1記憶領域MR3に記憶されているデータを、第1ブロックと異なるブロック内の第1記憶領域MR1に記憶させる。

(もっと読む)

記憶装置、基板、液体容器、システム及び記憶装置の制御方法

【課題】不揮発性の記憶部に記憶されたデータの破壊を抑止できる記憶装置、基板、液体容器、システム及び不揮発性の記憶部の制御方法等を提供すること。

【解決手段】記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60を制御する制御部30と、を含む。制御部30は、電源異常状態を検出する検出回路32と、不揮発性の記憶部60に対する読み出し又は書き込みのアクセス制御を行い、検出回路32により電源異常状態が検出された場合に、不揮発性の記憶部60に対する読み出し又は書き込みのアクセス制御を停止するアクセス制御部36と、を有する。アクセス制御部36は、アクセスサイクルの開始後に検出回路32により電源異常状態が検出された場合には、そのアクセスサイクルにおける読み出し又は書き込みのアクセス制御については、停止せずに完了する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

記憶装置、基板、液体容器、システム及び記憶装置の制御方法

【課題】不揮発性の記憶部に記憶されたデータの破壊を抑止できる記憶装置、基板、液体容器、システム及び不揮発性の記憶部の制御方法等を提供すること。

【解決手段】記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60を制御する制御部30を含む。制御部30は、ホスト装置10からの電源電圧VDDが供給されるホスト側電源端子TVHに接続される電源端子TV及び、ホスト装置10からのグランド電圧VSSが供給されるホスト側グランド端子TGHに接続されるグランド端子TGの少なくとも一方のフローティング状態を検出する検出回路32と、システムクロックSCKのマスク処理を行うマスク処理部34を有する。そして、マスク処理部34は、検出回路32によりフローティング状態が検出された場合に、システムクロックSCKをマスクする。

(もっと読む)

情報処理装置,プログラム,およびメモリの電源制御方法

【課題】消費電力を低減する。

【解決手段】情報処理装置は、部分的に電源の投入及び切断が可能である部分領域に区分けされており、電源の切断によって記憶されたデータが消失する第1の記憶部と、電源が切断されても記憶されたデータを保持する第2の記憶部と、起動されているタスクに関する使用データであって、第1の記憶部に記憶されている断片化された使用データを再配置する再配置部と、再配置の結果、部分領域の一部に使用データが記憶されており、該部分領域の一部に記憶されている使用データと同一のデータが第2の記憶部に記憶されている場合には、該部分領域の電源を切断する処理部と、を備える。

(もっと読む)

61 - 80 / 333

[ Back to top ]