Fターム[5B045DD01]の内容

マルチプロセッサ (2,696) | メモリシステム、ファイル管理 (299) | 共有メモリ、専用メモリ (190)

Fターム[5B045DD01]の下位に属するFターム

領域管理 (78)

Fターム[5B045DD01]に分類される特許

101 - 112 / 112

プロセッサ

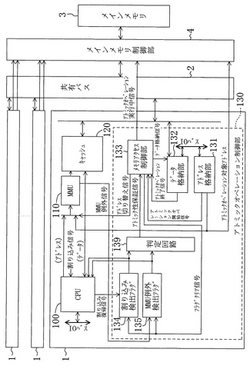

【課題】簡潔な構成で、処理能力の大幅な低下を招くことなく、他のプロセッサの動作や割り込み処理に対するアトミック性を確保する。

【解決手段】アドレス格納部131はアトミックオペレーションでアクセスされるメインメモリ3のアドレスを格納する。データ格納部132にはメインメモリ3から読み込まれたデータやCPU100によるアトミックオペレーションの処理結果のデータを格納する。割り込み検出フラグ134は割り込み復帰命令が実行されたときにセットされる。メモリアクセス制御部133は、アトミックオペレーションが終了するときに、割り込み検出フラグ134等に応じて判定回路139から出力されるアトミック性保証信号に基づき、処理結果データのメインメモリ3への書き込みを停止する。

(もっと読む)

ハイブリッド計算システムにおいて調停されたメモリバスを設けるためのシステムおよび方法

少なくとも1つのマイクロプロセッサを有する計算システムと、少なくとも1つのマイクロプロセッサに結合されるメモリサブシステムとを提供する。メモリコントローラは、メモリサブシステムと少なくとも1つのマイクロプロセッサとの間でメモリトランザクションを管理するよう結合される。少なくとも1つの調停ポートはメモリコントローラに結合され、外部の調停信号を受信するよう構成される。 (もっと読む)

クラスタ型マルチプロセッサシステムの異なるノード上で実行中のプロセス間でのメッセージの明示的な通信のためのシステムおよび方法

この発明の実施例は、クラスタ型マルチプロセッサのマシン境界を超えた、待ち時間が少なくて保護されたユーザモードの通信をサポートする、クラスタ型マルチプロセッサシステムにおける明示的な通信用メカニズムを含む。データ伝送は、固定された、単方向のポイントツーポイント接続を通って達成されてもよく、接続の各々は、概念的な各リンクの両端で伝送メカニズムに直接アクセス可能な、静的に割当てられた接続ごとのメモリバッファとともに、各端で少量の状態で具現化されてもよい。ネットワークインターフェイスの制限された制御、およびデータ伝送に対する責任の双方を、プロセッサにより管理される仮想アドレス空間のコンテキストにおいて実行され得るアプリケーションスレッドに、オペレーティングシステム(“OS”)により促進されて割当てることによって、システムメモリ保護が提供され得る。接続状態へのアクセスを、現在制御中のスレッドに関連するエントリに制限することによって、接続バッファ保護が提供され得る。 (もっと読む)

情報処理システム及び情報処理方法、並びにコンピュータプログラム

【課題】 各サブプロセッサが、メインプロセッサから割り当てられた処理を、システム全体の性能を低下させることなく実行する。

【解決手段】 圧縮画像の復号処理を行なうサブプロセッサは、メインメモリからデータをキャッシュに転送する際、画像の特徴を表すパラメータを基にキャッシュエリアを計算し、キャッシュするメモリ領域を適応的に変化させることにより、後続の処理でキャッシュにヒットする確率を高くする。サブプロセッサにおける画像信号処理のパフォーマンスが向上するとともに、メモリ転送のためのシステムバスのトラフィックを低減し、システム全体の性能の低下を防止する。

(もっと読む)

制御システム、制御装置および方法、記録媒体、並びにプログラム

【課題】OSの制御なしで、マルチプロセッサのリソースをプロセッサ毎に割り当てる。【解決手段】メインプログラムを実行するサブプロセッサユニット12−1が、分散並列処理を実行すると判定した場合、DMAC54−1は、分散並列処理を行うサブプログラムをメインメモリ14に記憶させて、さらに、メインメモリ14に記憶されているステータスを管理するテーブルに格納されているステータスフラグを実行希望に変更する。メインプログラムを実行するサブプロセッサユニット12−1以外のサブプロセッサユニットが、メインメモリ14から、実行希望であるステータスフラグに対応したサブプログラムをロードし、ロードしたサブプログラムを実行することで分散並列処理を行うことができるので、OSの制御なしで、マルチプロセッサのリソースをプロセッサ毎に割り当てることができる。本発明は、制御システムに適用できる。 (もっと読む)

メモリ排他制御装置、画像処理装置、及び画像形成装置

【課題】複数のCPUそれぞれへの不要な割り込み処理を排除するとともに共有メモリ領域への排他制御を行う。

【解決手段】モード毎に動作するCPUが異なる複数のCPU1,2と、これら複数のCPU1,2が共通で使用するメモリ5と、前記各CPU1,2に対応してそれぞれ設けられたASIC3,4のうち後者のASIC4に搭載され、前記各CPU1,2から前記メモリ5をアクセスするためのアクセス権を要求するアクセス権要求回路と、アクセス権の要求があったとき、他のCPUがアクセス権を取得していない場合にアクセス権を設定するアクセス権管理回路と、2以上の前記アクセス権要求回路が同時にアクセス権要求を行った場合に、前記アクセス権要求回路の要求を調停する調停手段とを備えた。

(もっと読む)

データ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法

【課題】 PUがネットワーク手段(接続装置)を介し、複数のMUにアクセスするシステムでは、ネットワーク手段の過負荷が生じ易く、PU内の演算処理がロードデータ待ちし、システムの性能を低下させる要因になっていた。

【解決手段】 複数のPU(処理装置)、複数のMU(記憶装置)がネットワーク手段3で接続されたデータ処理システムであり、PUにはCPUポート(要求元)140より要求情報を受け、これと先行要求情報を比較し、コマンド及びアドレスの所定部が一致すれば、RQ情報に代わり、差分フラグを立てアドレスの差分を出力する削減手段120、RQパケットや差分パケットを作成送信するPパケット手段130とを要求元ごとに備え、MUにはパケットを受信するMパケット手段201、差分フラグがオンで、差分パケットと保持している先行要求情報から今回の要求情報を作成する復元手段202を備える。

(もっと読む)

処理管理装置、コンピュータ・システム、分散処理方法及びコンピュータプログラム

【課題】 ネットワークに接続されている複数の処理装置とこれらの処理装置を管理する処理管理装置とで分散処理を行う際の処理管理装置のオーバーヘッドを回避する。

【解決手段】 傘下の複数の処理装置(SPU)207等を管理する処理管理装置(PU)203が、いずれかのSPUからタスク要求を受け付けたときに当該タスクのサイズ又は種類に適合するクラスタを所定のメモリにリストアップされているクラスタリストより特定し、特定したクラスタに対して当該タスクを割り当てるとともに、そのクラスタとタスクの要求元SPUの少なくとも一方に他方の通信設定情報(通信アドレス等)を伝達することにより、当該クラスタと要求元SPUとの間のネットワーク通信によるダイレクトな実行結果の受け渡しを可能にする。

(もっと読む)

マイクロプロセッサ及び論理装置の為の接続システムの方法及び構造

複数のプロセッサと論理装置とを接続するためのシステムが提供される。このシステムは、それぞれが共有記憶装置に接続された、中央プロセッサユニット・ノードと、再構成可能接続ノードとを含む。このシステムは更に中央プロセッサユニット・ノードと再構成可能接続ノードの間の信号通信に用いる個別の入出力バスを含む。 (もっと読む)

プロセス配置装置、プロセス配置方法及びプロセス配置プログラム

【課題】 性能を低下させるようなコンピュータ資源の消費を行わずにノード間メモリアクセスを削減する。

【解決手段】 プログラムに含まれる1以上のプロセスのうちの各プロセスが、ccNUMAアーキテクチャの何れかのノードに属するCPUと何れかのノードに属するメモリを用いて実行される方式に適用されるプロセス配置装置において、各プロセス毎に、該プロセスを実行するCPUが属するノードである第1ノード及び所定時間内に該CPUがアクセスする回数が最も高いメモリが属するノードである第2ノードを検出するノード検出手段と、各プロセス毎に、前記第1ノードと前記第2ノードが一致するか否かを判断するノード一致判断手段と、各プロセス毎に、前記第1ノードと前記第2ノードとが一致しない場合に、該プロセスを実行するCPUを、前記第2ノードに属するCPUに変更するCPU割当変更手段を備える。

(もっと読む)

共有メモリを用いるプロセッサ間通信方法及び装置

第1のプロセッサ(102)と第2のプロセッサ(104)との間においてメッセージを転送する方法に関する。この方法は、第1のプロセッサ、即ち、マスタ・プロセッサ(102)に対し、空きメッセージ・バッファを要求する工程(106)を含む。第1のプロセッサ(102)は空きメッセージ・バッファ・ポインタを送信する(108)。第2のプロセッサは空きメッセージ・バッファ・ポインタを用い、共有メモリ(112)内の割り当てられたメモリの位置を特定する。続いて、第2のプロセッサ(104)は割り当てられたメモリ領域にメッセージを読み込み、そのメッセージを送信する(110)。メッセージの受信後、第1のプロセッサ(102)は共有メモリ(112)において発見された割り当てられたメモリ領域を、将来使用可能であるように解放する。この共有メモリ方式を用いる無線通信デバイス等の電子デバイスも開示する。  (もっと読む)

(もっと読む)

動的マルチクラスタシステムリコンフィギュレーション

【課題】動的なマルチクラスタシステムのコンフィギュレーションの変更を可能にする方法および装置を提供する。

【解決手段】ある例では、マルチクラスタシステムにおけるプロセッサ群は、仮想アドレス空間を共有する。動的にプロセッサ、I/Oリソース、およびクラスタを導入および除去するメカニズムが提供される。このメカニズムは、リセットのあいだ、またはシステムが動作中に実現されえる。リンクは動的にイネーブルまたはディセーブルされえる。

(もっと読む)

101 - 112 / 112

[ Back to top ]