Fターム[5B046JA04]の内容

Fターム[5B046JA04]の下位に属するFターム

論理シミュレーション (393)

Fターム[5B046JA04]に分類される特許

841 - 860 / 960

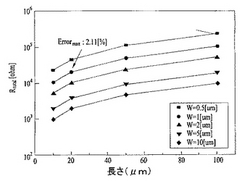

半導体集積回路のシミュレーション方法

【課題】抵抗素子の特性を正確に反映できると共に、それぞれ異なる長さ(L)および幅(W)を有する多様な抵抗素子に共通に適用でき、かつ正確度が高くなるようにする。

【解決手段】多様な長さ(L)と幅(W)を有するそれぞれの抵抗素子に対して印加される電圧を変化させながら抵抗値を測定する段階と、測定された抵抗値を電圧に対する線形関数で表すことで、抵抗素子の電圧による抵抗変化係数(VCR:Voltage Coefficient Resist)を算出する段階と、VCRを用いて特定の長さと幅を有する抵抗素子の抵抗値を算出する段階とを備える。

(もっと読む)

プログラマブルデバイスのユーザプログラミングイベントをプレビューするプログラマブルデバイス及びその方法

プログラマブルデバイス1が、少なくとも一つのタイマ8と、少なくとも一つのタイマ8の経過によってトリガされるイベントEV1及びEV2を備えるユーザプログラマブルタイマリストを記憶するためのメモリ7とを有する。プログラマブルデバイス1は、ユーザによって活性化され得るシミュレーションモードで動作し、シミュレーションモードにおいて、タイマリストに記憶されるユーザプログラミングイベントEV1及びEV2を処理する動作は、イベントをトリガするタイマ8が経過されているかのようにシミュレートされる。  (もっと読む)

(もっと読む)

3次元回路シミュレータ

【課題】 正確な回路特性結果を得ることが可能な3次元回路シミュレータを提供する。

【解決手段】 3次元電子部品73からなる3次元回路の特性を、3次元電子部品情報PIを用いて計算する。各3次元電子部品73の特性を近似ではなく、実際の特性により計算することができる。また、周囲との干渉効果なども考慮することができる。よって、正確な回路特性結果を得ることができる。また、理想素子による回路モデルを用いる必要はないので、複雑な動作機構の素子の場合でも、その回路特性結果を容易に得ることができる。さらに、使用可能な周波数範囲などを限定することなく、特性結果を得ることができる。

(もっと読む)

半導体記憶装置の製造方法及び半導体設計装置

【課題】 設計の容易化、または設計期間の短縮を実現可能な半導体記憶装置の製造方法及び半導体設計装置を提供する。

【解決手段】 例えば、設計したメモリアレーを検証する際に、様々な分布を備えた各種パラメータVN(ΔVBDL),VN(ΔVTN),VN(IJ)の関数によって定式化されるメモリセルの読み出し信号量VS_EFFを用い、この読み出し信号量VS_EFFの値を各種パラメータ毎の分布からランダムに抽出した値を用いて算出し、この算出結果からメモリセルの良否判定を行い、これらの読み出し信号量VS_EFFの値の算出およびメモリセルの良否判定をメモリアレーが備える多数のメモリセルに対して行う。そして、これによって得られた不良ビットの総数などを、メモリアレーの評価基準に用いる。

(もっと読む)

ユーザインタラクティブグラフィカルツールを伴う製品のエディションおよびシミュレーションのデータベースシステム

【課題】モデル化オブジェクトに関連したデータを有するストレージシステムを含む、製品のエディションおよびシミュレーションのシステムを提供する。

【解決手段】本システムは、これらのモデル化オブジェクトの特徴のサブセットの編集に適した複数のソフトウェアツールを含むエディションワークベンチを有するグラフィカルユーザインターフェース400を有する。このエディションワークベンチは、グラフィカルユーザインターフェース400中にユーザインタラクティブなグラフィカルツールを表示する。このグラフィカルツールは、ユーザアクションに対してすぐに、このサブセット中に含まれない特徴に応じたモデル化オブジェクトのシミュレーションをトリガし、このシミュレーションは、このストレージシステムにおけるクエリの結果を使用している。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】既存のGminステッピング法は全ノードに一律の仮想コンダクタンスを挿入するため、仮想コンダクタンスを小さくして最終解を得る繰り返しの処理の過程で得る、この仮想コンダクタンスでの暫定解が次の仮想コンダクタンスの値での初期値として、解からはずれる、といった危険性を防止する。

【解決手段】付加する仮想コンダクタンスの値をノード毎に独立した値をとることができるようにし、さらに、個々の仮想コンダクタンスの値を、回路方程式を解く際のそのノードの安定性を基準に変更する機能を有することにより、回路中で回路方程式の導出が困難なノードに対して集中的に大きな既成コンダクタンスを挿入でき、前記ノード以外は早期に最終的な回路状態にすることができ、これにより、暫定解が続く仮想コンダクタンスの値での暫定解導出の初期値としてより解に近いものとする可能性を高めることができる。

(もっと読む)

ニットデザイン方法および装置

本発明の目的は、毛羽の多い編糸で実際に編成される編地の風合に近い画像を表示することである。毛羽2が多い編糸の編糸画像データ1の少なくとも一部を、編糸画像データ1が延びる長さ方向については一定の長さずつ、幅方向については両側の毛羽領域のメッシュ3,4と、中間の糸本体領域のメッシュ5とに分割する。編地を構成する編目ループ6に対応して各メッシュ3,4,5を変形し、毛羽領域の変形メッシュ7,8と糸本体領域の変形メッシュ9とを形成する。この変形の際に、毛羽領域のメッシュ3,4に対する毛羽領域の変形メッシュ7,8の比率は、糸本体領域のメッシュ5に対する糸本体領域の変形メッシュ9の比率よりも小さくなるようにする。  (もっと読む)

(もっと読む)

回路評価装置及び回路評価方法

【課題】 モデルパラメータの数の増加を抑制し、且つ高精度の回路シミュレーションが実行可能な回路評価装置及び回路評価方法を提供する。

【解決手段】 複数の素子の位置情報を含む回路情報を半導体集積回路のレイアウト情報から抽出する回路情報抽出部101と、複数の素子の特性値のチップ面内ばらつき情報及び位置情報に基づき、特性値の基準値からの複数の素子の特性値の変更量をそれぞれ設定する変更量設定部110と、回路情報及び変更量に基づき作成される変更量付きネットリストを使用して回路シミュレーションを行うシミュレーション部103とを備える。

(もっと読む)

回路シミュレーション方法および装置

【課題】素子分離用絶縁膜の幅の異なるトランジスタのモデルを作成し、微細化された集積回路の設計に有用な回路シミュレーション装置およびモデル化方法を提供する。

【解決手段】本発明では分離幅依存パラメータ補正手段4において、素子分離用絶縁膜幅依存性を有するパラメータの近似式を作成し、作成した近似式を用いて得られた補正パラメータの値を元のパラメータの値と置き換えることにより、素子分離用絶縁膜幅の異なるトランジスタのトランジスタモデルを作成する。これにより、より実測データに近い応力によるトランジスタ特性の変化を考慮に入れた、精度の高い回路シミュレーションが可能となる。

(もっと読む)

設計支援装置、設計支援プログラム及び設計支援方法

【課題】装置の異常現象を任意のタイミングで擬似的に発生させ、異常現象に応じた制御を制御ソフトウェアが行えるか否かの検証を効率よく行なう。

【解決手段】シート搬送装置内のデバイスの異常発生条件を設定し、設定された異常発生条件を満たしたかどうかをシミュレーション動作中に判断し、異常発生条件を満たしたと判断した場合、異常が発生したデバイスに対応する異常時の制御を行う。

(もっと読む)

情報処理装置及びその制御方法、プログラム並びに記憶媒体

【課題】 搬送経路内を搬送される柔軟媒体と搬送経路を構成する構成部品との距離を精度良くシミュレーションすること。

【解決手段】 搬送経路内を搬送される柔軟媒体の挙動をシミュレーションする情報処理装置1900は、前記柔軟媒体と前記搬送経路を構成する構成部品との距離を時系列で演算処理する処理部1902と、処理部1902で演算処理された距離を時系列で表示する表示部1904と、を備える。

(もっと読む)

異常状態発生ノード検出方法

【課題】回路シミュレータが、素子レベルの回路図からハイインピーダンスが発生するノードを検出できるようになる異常状態発生ノード検出方法を提供する。

【解決手段】回路シミュレータに、素子本来の動作モデルとは異なる異常検出用の動作モデルを用意する。異常検出用の動作モデルは、ハイインピーダンスが発生すると該素子の端子に通常の動作モデルを設定したときとは異なる電圧または電流が発生する動作モデルである。素子本来の動作モデルを設定した回路の動作解析により得た各ノード電圧(ステップS202)と異常検出用の動作モデルを設定した回路の動作解析により得た各ノード電圧(ステップS207)を比較し(ステップS208)、その差が閾値以上のノードを、ハイインピーダンスが発生するノードと判断する。

(もっと読む)

解析装置及びプログラム

【課題】余分な解析を行わずに短時間で因子の最適値を自動的に見つけること。

【解決手段】複数因子と該因子の数値条件が入力される入力部1と、前記複数の因子により解析を行う解析計算部2と、解析結果と実測値との誤差を判定する誤差判定部3と、前記複数の因子の数値条件を決定する数値条件決定部4とを備え、前記解析計算部2で前記複数の因子の数値条件を数値順にマトリクス状態にしておき、スタートとして前記複数の因子の任意の数値条件により解析して前記誤差判定部3で実測値との誤差を判定し、次に、前記解析計算部2で前記マトリクス状態におけるスタート時の前記複数の因子の数値条件と1つ異なる周囲の数値条件で解析して前記誤差判定部3で実測値との誤差を判定し、次に、前記数値条件決定部4で前記周囲の数値条件で解析した誤差が一番小さくなる方向の因子の数値条件に進んで前記解析計算部2で解析を行う。

(もっと読む)

タンパク質の立体構造探索方法、立体構造探索用コンピュータプログラムおよび立体構造探索装置

【課題】 タンパク質の確からしい立体構造を効率的に探索することを可能とするタンパク質の立体構造探索技術を提供する。

【解決手段】 タンパク質の連結構造の内、立体構造の探索に使用するための立体構造が既知な部分を決定し、このタンパク質の連結構造を、上記決定された立体構造既知部分を含むフラグメントに分割し、上記決定された立体構造既知部分についてはその立体構造を初期状態として採用し、他の部分については任意の立体構造を初期状態として採用し、動径分布の実験値を真の動径分布とし、逆モンテカルロ法を用いて、与えられた各フラグメントの立体構造から計算によって求められる動径分布が真の動径分布に近づくように、各フラグメントの立体構造を最適化する。

(もっと読む)

クロストーク検証装置およびクロストーク検証方法

【課題】半導体集積回路のレイアウト時に、クロストークの原因となる寄生容量を的確に探し出し、その寄生容量が発生したレイアウト箇所をエラー表示することができるクロストーク検証装置およびクロストーク検証方法を提供する。

【解決手段】設計者がクロストークの影響を分析したいネットを指定するネット指定手段107と、レイアウトパターン101から抽出した寄生容量をデータベース化した寄生容量情報105から、ネット指定手段107によって指定されたネットを接続情報として片側端子にもつ寄生容量を選択する寄生容量選択手段108と、寄生容量選択手段108で選択された寄生容量を1つずつ回路データに付加した回路を生成する回路生成手段109と、回路生成手段109で得た回路を回路シミュレーションする回路シミュレータ111と、その結果を表示するエラー出力手段112とを備える。

(もっと読む)

寄生素子を含む回路のシミュレーション方法

【課題】 寄生素子を含む集積回路のシミュレーションの収束性を向上させることのできるシミュレーション方法を提供することを目的とする。

【解決手段】 寄生素子を含まない回路情報により全ノードの電圧値、電流値を計算し、この計算した過程で電圧値、電流値が安定しているノードを求め、このノードに対して寄生素子を付加して回路情報を再構成し、前記回路情報の再構成前の計算結果を再構成後の初期値として全ノードの電圧値、電流値の計算を行い、ノードに対して徐々に寄生素子を付加し、最終的に全ての寄生素子を含む回路情報で全ノードの電圧値、電流値を求める。この方法によれば、寄生素子を回路情報に徐々に挿入しながら全ノードの電圧値、電流値を計算するとき、回路情報の再構成前の計算結果を再構成後の初期値として計算を継続することによりノードに対して解に近い初期値を与えることができ、収束性を向上できる。

(もっと読む)

自動的に生成されたテストプログラムのための採点機構

【課題】本発明は、テストコードの実行がシミュレートされている間に選択された機能状態の適用範囲で作られる評価をするテストプログラムの生成の自動化を提供する。

を提供する。

【解決手段】データ処理装置のためのテストプログラムは、テストプログラムを形成している集団におけるプログラム命令の順序付けられたリストからなる例の変更について、遺伝子アルゴリズムを使用して生産される。集団は、特定の例が集団の中又は外へ交換されるべきであるか否かについてなされる決定がされているとき、集団全体がデータ処理装置において所定の機能ポイントの刺激に対して採点されることによる測定を使用して評価される。

(もっと読む)

半導体集積回路の遅延計算方法およびセルキャラクタライズ方法

【課題】ゲートレベル遅延計算において、入力端子容量が駆動負荷容量および入力スルー依存性を持つが、現状の遅延計算においては、これらの依存性が考慮されていない。また、入力端子容量も見かけの入力端子容量よりも大きく抽出されるという問題がある。

【解決手段】予め、セルの入力端子容量を関数式で求めておき、遅延計算において、入力端子容量を各インスタンスにおける入力スルーと駆動負荷容量の関数として計算しながら求める。セルキャラクタライズにおいては、入力端子の電圧値が基準電圧に到達するまでの時間に入力端子に流れ込んだ電流の総和を求めることで、実際の見かけの入力端子容量に近い値を求めることが可能になる。

(もっと読む)

デジタル回路ソフトウェアシミュレータ

【課題】デジタル回路、アナログ回路基盤のハンダ付け、基板加工等の工程を踏まずに、パーソナルコンピューター上のソフトウェアで動作を確認し試作基板作成のコストを削減する。

【解決手段】パーソナルコンピューターを用いて、ハードウェア全般で使用される、デジタル回路、アナログ回路の情報を、シミュレートする情報として、ハードディスク内に作成または保管し、プログラムを用いて、入力部品のキーボード入力、表示部品のモニタ表示、基板のシミュレート状況のモニタ表示をするソフトウェアを用いる。

(もっと読む)

回路設計支援方法、回路設計支援システム、装置及びプログラム

【課題】

波形シミュレーションシステムの負荷を軽減する。

【解決手段】

回路の指定位置の信号波形データを計算する複数のシミュレーションシステム毎に異なるフォーマットを有する信号波形データをフォーマット識別データを加えた暗号化された波形データを作成し、波形データベースに記憶させる。そして、クライアントシステムがその波形データベースから複数のフォーマットの暗号化された波形データを読み出し、解読し、複数のフォーマットの信号波形データに由来する複数の波形の軌跡のデータを表示部に拡大縮小して表示させる。

(もっと読む)

841 - 860 / 960

[ Back to top ]