Fターム[5B046JA04]の内容

Fターム[5B046JA04]の下位に属するFターム

論理シミュレーション (393)

Fターム[5B046JA04]に分類される特許

921 - 940 / 960

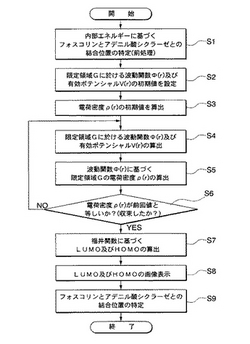

高分子化合物の結合評価方法

【課題】 高分子化合物と評価対象化合物との結合部位を従来よりも効率良く解明すると供に、高分子化合物と評価対象化合物との結合位置の信憑性を従来よりも向上させる。

【解決手段】 高分子化合物に対する評価対象分子の結合を数値計算に基づいて評価する方法であって、評価対象分子と高分子化合物との結合部位を、評価対象分子及び高分子化合物の評価対象分子に隣接する部分を含む所定限定領域における電子状態の不安定な部位として検出する。

(もっと読む)

半導体集積回路における特性検証用ネットリストの生成方法

【課題】 半導体集積回路の遅延シミュレーション等の特性検証において、精度を損なうことがなく、かつデータ量の少ないシミュレーション用ネットリストを生成するための、リダクション方法を提供する。これによって、大規模なブロックに対しても短時間で、かつ高精度に、効率的な特性検証の実行を可能とする。

【解決手段】 リダクションルール提供手段2より与えられるリダクションルール3に従って、レイアウト設計データから寄生素子情報を抽出して得られたLPEネットリスト1を、目的とする特性検証結果への影響を無視できる範囲でリダクションして、特性検証用ネットリスト5を生成する。

(もっと読む)

半導体集積回路の動作検証システム及びその動作検証方法

【課題】 動作検証内容に応じた特性ライブラリを作成することにより高精度の動作検証ができる半導体集積回路の動作検証システム及び動作検証方法を提供する。

【解決手段】回路セル設計レイアウト情報を入力して、仕上がりレイアウトを予測し、ネットリスタ8を用いて、仕上がり予測レイアウト情報に基づいてネットリスト変換を行ない、消費電力についての動作検証に用いる第1ネットリスト4aと、遅延についての動作検証に用いる第2ネットリスト4bと、容量についての動作検証に用いる第3ネットリスト4cとを作成する。回路シミュレータ9により、各ネットリスト4a,4b,4cを用いて、動作検証を行なった結果は、第1〜第3特性ライブラリ5〜7に格納される。

(もっと読む)

半導体集積回路パターンの検証方法、フォトマスクの作成方法、半導体集積回路装置の製造方法、及び半導体集積回路パターンの検証方法を実現するためのプログラム

【課題】パターン検証を効率的に行う。

【解決手段】半導体集積回路パターンの検証方法は、処理基板上で所望する半導体集積回路の設計パターンAに基づいて補正処理を施すシミュレーションを実施し、処理基板上で形成されるシミュレーションパターンCを作成する工程(ST1,2)と、シミュレーションパターンCと設計パターンAとを比較し、第1の差分値Xを検出する工程(ST3)と、第1の差分値Xが第1の所定値V1以上である危険点を抽出する工程(ST4)と、危険点のパターン形状をそれぞれ比較し、第2の差分値Yを検出する工程(ST5)と、第2の差分値Yが第2の所定値V2内であるパターンを1つのグループとする工程(ST6)と、グループ毎のパターンを所定数ずつ抽出し、この抽出されたパターンの危険点の検証を行う工程(ST8,9)とを具備する。

(もっと読む)

半導体集積回路の設計方法、その設計支援装置及び遅延ライブラリ

【課題】光学系の収差により、セルの配置方向でデバイス特性及びパス遅延が変動する現象を設計時に取り込んでタイミング検証を行なえるようにして、設計マージンの精度を高められるようにする。

【解決手段】例えばワークステーションにより構成される設計支援装置100は、CPU101と、主記憶(メインメモリ)102と、出力部103とを有している。LSIの遅延計算には、検証の対象であるLSIのレイアウトデータ201と、検証の対象であるLSIを構成するセル群における各セルの配置方向を含めた遅延ライブラリ202を読み込みながら行なう。これにより、ウェハ上に配置される各セルの配置方向に応じてタイミング検証を行なえるため、設計マージンの精度を向上することができ、半導体集積回路の歩留りを向上することができる。

(もっと読む)

不均質材料のシミュレーション方法

【課題】ゴム弾性体のような、材料特性の異なる複数の材料相が分散配置されたミクロ構造を有する不均質材料の挙動をシミュレートする際、マクロ構造とミクロ構造のシミュレーション演算を整合させて効率よく行う。

【解決手段】不均質材料のミクロ構造を再現したミクロスケールモデルを変形させてシミュレーション演算を行うことにより、超弾性ポテンシャル及び材料定数を定め、不均質材料を含む構造体を再現したマクロスケールモデルを用いて、前記超弾性ポテンシャル及び前記材料定数に基づいてマクロスケールシミュレーション演算を行う。マクロスケールシミュレーション演算結果のうち、不均質材料の配置部分の代表点の歪の結果を取得し、この歪からミクロスケールモデルにおける境界領域の変位を定め、この変位をミクロスケールモデルの境界条件としてミクロスケールシミュレーション2を行う。

(もっと読む)

モノリシックなシリコンベースの光電子回路の設計、シミュレーション、及び検査用の統合的アプローチ

【課題】

【解決手段】 コンピュータを用いた設計(CAD)ツールを使用して、モノリシックな、シリコンベースの電子−光学チップにおける電子及び光学構成部品の統合的設計、検査及びレイアウトを実行する。別々のトップレベル動作ロジック設計が、最終的なシリコンベースのモノリシック構造内に含まれる3つの異なるタイプの要素に対して準備される。(1)デジタル電子集積回路要素;(2)アナログ/混合信号電子集積回路要素;及び(3)光−電子要素(受動及び能動光学要素を含む)である。動作ロジック設計が完了すると、この結果が組み合わされ、共通シミュレートされる。回路中の各タイプの異なる要素について物理的レイアウト設計が開発され、検査される。別々の物理的レイアウトが共通検査され、全体の物理的設計の特性を査定する。共通シミュレーションの結果が、所望の動作パラメータが得られるまでのロジック設計及び/又は物理的レイアウトにおいてなされた変更を用いて、共通検査の結果と比較される。所望の結果が発生すると、最終製品を提供する(テープアウト)ように従来のウエハレベルの組立動作が考慮される。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及び回路シミュレーションプログラム

【課題】一度回路シミュレーションを実行した回路状態を使用して引き続きシミュレーションを実行することで回路解析時間の短縮を図る。

【解決手段】クライアント端末12から送信されるコマンド記述を解釈するコマンド記述解釈手段14と、このコマンド記述解釈手段が解釈したコマンドに基づいて回路シミュレーションを実行するコマンド実行手段19と、回路シミュレーションを実行したときの回路状態を保持する回路状態保持部18と、回路状態をファイルとして保持する回路状態ファイル保持部22と、回路状態保持部18に保持されている回路状態を回路状態ファイル保持部22にファイルとして保持する回路状態出力手段23と、クライアント端末からのコマンドに基づいて回路状態ファイル保持部22に保持されている回路状態ファイルを読み込み現在の回路状態として設定する回路情報/回路状態読み込み手段15とを備える。

(もっと読む)

デバイスシミュレーション装置、デバイスシミュレーション方法及びデバイスシミュレーションプログラム

【課題】 プロセス・シミュレーションの不純物濃度分布及び形状計算結果を、デバイス・シミュレーション構造定義に反映させ、少ないプロセス・シミュレーション回数で効率良くプロファイル設定を行うデバイス・シミュレーション装置を提供する。

【解決手段】 補間濃度分布算出部15は、複数のプロセス・シミュレーションの結果から、不純物濃度分布の差分を求め、その差分情報を処理し補間データを作成する。そして、その補間データをデバイス・シミュレーション用に設定されたメッシュ情報上に展開する。デバイス特性シミュレーション部16は、デバイス・シミュレーションを実行する。出力分12は、実行結果について表示等の出力を行う。

(もっと読む)

半導体装置の評価設計装置、半導体装置の評価設計方法、半導体装置の評価設計プログラムおよび記録媒体

【課題】半導体装置の評価設計を、現実的かつ高精度におこなうこと。

【解決手段】ゲート電極のパターンデータ323bのゲート長情報lgを抽出する。また、ゲート電極のパターンデータ323bと、パターンデータ323bに隣接するゲート電極のパターンデータ323a,323cとの距離情報sg1、sg2を算出する。ゲート電極のパターンデータ323bのばらつきパラメータを、ばらつきパラメータテーブル254から端辺ごとに抽出する。そして、端辺ごとにばらつき情報を算出する。ネットリスト600の記述内のゲート長情報lg(lg=120nm)に、算出されたばらつき情報Dgを加算する。

(もっと読む)

適応評価器、遺伝的アルゴリズムマシン及び適応度計算方法

【課題】 半導体回路のモデルパラメータの最適化抽出方法を提供する。

【解決手段】 遺伝的アルゴリズムマシン900の適応評価器15において、子モデルパラメータファイル44から子モデルパラメータを入力して、入力した子モデルパラメータに基づいてk個のモデル評価値を求めて記憶部17の評価値ファイル32に記憶する評価値計算部21を備えている。また、評価値計算部21が評価値ファイル32記憶したk個のモデル評価値を読み込み、読み込んだk個のモデル評価値が形成するエリアの大きさを算出して記憶部17のエリア値ファイル33に記憶するエリア算出部22を備えている。また、エリア算出部22がエリア値ファイル33に記憶したエリアの大きさを読み込み、読み込んだエリアの大きさに基づいて子モデルパラメータの適応度を計算し、記憶部17の適応度ファイル34に記憶する適応度計算部23を備えている。

(もっと読む)

VIAモデルを有する伝送路解析シミュレータ

【課題】伝送路シミュレーションにおいて、VIAをLCを付加する単純LCモデルとするのでは、高周波において解析結果の精度が低い。これを簡易な手段で実用的精度を得ることを目的とする。

【解決手段】単純LCモデルをベースにして、基板の層構成に合わせて、L、Cを分割構成する。Lは、基板の層構成にあわせて分割し直列接続した形に修正する。Cは、電源層/グランド層(V/G層)の数とランド層の数に合わせて分割する。これにより、VIA内での接続する層の違いや分岐(複数の層へ信号が通過する場合など)のモデル表現が容易になる。さらに、ランド径>逃げ径の関係が成り立つ場合に、余分なC成分をモデルに付加する。逆に、ランド径<逃げ径の関係となる場合、逃げ径〜ランド径迄のL(インダクタ)成分をモデルに付加する。

(もっと読む)

ハーネス設計支援装置および方法並びにハーネス設計支援プログラムおよび同プログラムを記録したコンピュータ読取可能な記録媒体

本発明は、例えばプリンタ,自動車,工作機械,産業用ロボット等のようにハーネスを組み込んだ装置の設計開発に際して、機構動作に伴うハーネスの動きを、処理量の増大を招くことなくリアルタイムで確認できるようにして、ハーネス設計の動的検証が可能な環境を提供し、ハーネス設計の効率化を実現するために、設計対象装置におけるハーネス以外の機構部品についての3次元モデルデータ(22)を予め保持する機構情報保持部(20)と、該ハーネスに関する情報をハーネス情報(23)として設定するハーネス情報設定部(11)と、該ハーネス情報設定部(11)により設定された該ハーネス情報(23)と該機構情報保持部(20)における該機構部品の3次元モデルデータ(22)とに基づいて該ハーネスおよび該機構部品の3次元機構モデルを構築し、該3次元機構モデルにより該ハーネスの動作を該機構部品の動作と連動させてシミュレートするシミュレーション部(12)と、該ハーネスの動作および該機構部品の動作を表示する表示部(30)と、該シミュレーション部(12)によるシミュレーション結果を該ハーネスの動作および該機構部品の動作として該表示部(30)に表示させる表示制御部(13)とをそなえて構成される。  (もっと読む)

(もっと読む)

波長変換器配置設計方法およびその装置

【課題】 短時間で波長変換器の配置設計を実行することのできる波長変換器配置設計方法およびその装置を提供する。

【解決手段】 設計パラメータ入力部2と、波長変換器を配置するための初期値を入力する波長変換器配置初期値入力部3と、入力された設計パラメータと前記波長変換器配置初期値とに基づいてRWAシミュレーションを実行するRWAシミュレータ部4と、RWAシミュレーションの結果から波長変換器再配置指標を抽出する波長変換器再配置指標抽出部5と、得られた波長変換器再配置指標に基づいて、波長変換器を再配置する波長変換器再配置部6と、再配置前の波長変換器の配置と再配置後の波長変換器の配置とを比較して、波長変換器配置変動値を求めることにより、配置の変動を判定する波長変換器配置変動判定部7と、前記波長変換器配置変動値が収束するとき、その波長変換器配置を出力する波長変換器配置出力部8とを備えた。

(もっと読む)

コンピュータ支援によって、特定のパターンを有する織編物サンプルをシミュレートするパターン付きの織編物品を製作する方法およびシステム

【課題】コンピュータ支援によって、特定のパターンを有する織編物サンプルをシミュレートするパターン付きの織編物品を製作する方法。

【解決手段】織編物サンプルの1セットの二次元画像データを格納するステップと、織編物品を製作するための加工糸であり、パターンを確定するためにテクスチャーを変更可能な加工糸を選択するステップと、織編物品のためにデザインされた糸の向きに対応する方向に沿って画像データを読み出し、織編物サンプルのパターンの位置を決定するステップと、二次元画像データから一次元線データのセットを生成するステップと、糸製造装置(25)において糸を加工するパラメータを代表する糸加工制御データを格納するステップと、糸製造装置(25)を制御することにより糸を製造するステップと、製造された糸を使用して、パターン付きの織編物品を製作するステップとを含む。

(もっと読む)

半導体集積装置の設計方法、設計プログラム、および記録媒体

【課題】 性能や消費電力を最適化するバスを決定する際、大局的なバス構成、方式、および動作周波数の最適化が可能となる半導体集積装置の設計方法、設計プログラム、および記録媒体を提供する。

【解決手段】 本発明の半導体集積装置の設計方法では、半導体集積装置のシミュレーション処理(ステップS1)を行い、トランザクションデータをトランザクションデータ記憶処理(ステップS2)にて記憶する。その後、トランザクションデータ解析処理(ステップS3)にてトランザクションデータを解析し、その解析結果から生成される最適なバスのビット幅、エンコーディング方式、または動作周波数などを静的または動的に制御する制御部を生成する(ステップS4)。

(もっと読む)

最適化エキスパートシステム

エキスパートシステムを作成し、動作させるための方法、装置、および、システム。 (もっと読む)

電子回路の設計方法および装置

アナログおよび混成信号回路を含む、電子回路を設計する方法および装置であって、実施形態の一例では、階層的設計およびサイジング・フローを、1つ以上の評価モデル(例えば、性能および実現可能性モデル)と共に用いて、あるレベルにおいて得られた結果が階層の他のレベルでも有効であり関連性を保つようにする。別の態様では、例えば、階層の種々のレベルと関連付けられた1つ以上の既存の性能モデルに基づいて性能を評価する後処理ステップによって、設計の歩留まりを考慮して階層的サイジングを実行する。これらの方法はコンピュータ・プログラムにて具体化され、このプログラムを実行するように適合化されたコンピュータ・システムにて実行される。 (もっと読む)

自動化システムのシミュレーションのための方法及び装置

本発明は自動化システムのシミュレーションのための方法及び装置(10)に関する。著しく異なる計算速度で動作するシミュレーション構成要素が全シミュレーションに結合され得るように自動化システムのシミュレーションを可能にするため、外部タイミングソースを用いてクロック可能な制御構成要素(11)及び外部タイミングソースを用いてクロック可能な少なくとも1つのシミュレーション構成要素(12、13、14)による方法が提案され、その際制御構成要素(11)及び少なくとも1つのシミュレーション構成要素(12、13、14)に対し制御構成要素に依存しないタイミングコーディネータ(17)により調整されたクロックシステムが準備される。  (もっと読む)

(もっと読む)

プロセス変動バンドを用いた集積回路レイアウト設計法

異なる処理条件の結果として、半導体のウェハ上に作成された複数の対象物の変動を算出することによる集積回路のレイアウトおよび設計解析のためのシステム。本変動は各機能の不具合を判断するため、または処理中に生じる変動の影響度によりレイアウト設計をランクづけするために解析される。一実施例において、本変動は、対象物が常に印刷する最小領域を判断する内端、および対象物が特定の処理条件下で印刷する最大領域を判断する外端をもつPVバンドにより示される。  (もっと読む)

(もっと読む)

921 - 940 / 960

[ Back to top ]