Fターム[5B054CC01]の内容

Fターム[5B054CC01]に分類される特許

1 - 20 / 97

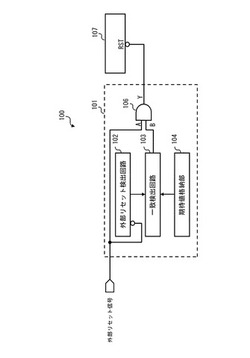

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】ユーザがバッテリを取り外すことが出来ない情報処理装置において、不具合が起きた場合に、容易に強制終了させること。

【解決手段】二次電池と、情報処理装置に所定の処理を実行させるための機能が割り当てられている複数のスイッチと、前記複数のスイッチの内の電源スイッチの操作に応じて情報処理装置の電力管理を行う電力管理コントローラと、前記二次電池から供給される電力を用いて前記情報処理装置を構成するコンポーネントに動作電源を供給する電源回路と、前記電力管理コントローラからの要求に応じて前記電源回路を制御する電源コントローラとを具備し、前記電源コントローラは、前記複数のスイッチの内の2以上のスイッチに結合され、前記2以上のスイッチに対する所定の操作に応答して、前記電力管理コントローラへのリセット信号を制御することによって前記電力管理コントローラに初期化処理を実行させる。

(もっと読む)

電源供給制御装置およびヘッドホン

【課題】リセットスイッチを設けずに、少ない部品点数でもって、情報処理装置の暴走に対処する。

【解決手段】電源を情報処理装置に対して供給する場合に一の状態を継続するスイッチを有し、スイッチが一の状態とされると、電源が情報処理装置に供給されると共に、情報処理装置の第1のポートが予め設定された所定の論理レベルとされ、第1のポートが所定の論理レベルとされたことを情報処理装置が検出して第2のポートを予め設定された所定の論理レベルとする。スイッチが一の状態から他の状態となると、第1のポートが所定の論理レベルと異なる論理レベルとされ、情報処理装置が第1のポートの論理レベルの変化を検出して終了処理を行い、終了処理の後に第2のポートを所定の論理レベルと異なる論理レベルとして、電源供給がオフとされる。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

端末装置並びにフリーズ検出方法及び端末装置の制御方法

【課題】細かい設定をすることなく、自動的にフリーズ状態を検出し、リセット処理等を行う端末装置の提供。

【解決手段】端末装置は、電源からCPUに供給される電流値を測定する電流測定部と、前記CPUをリセットするリセット制御部と、前記CPUと独立して動作し、動作モードに反した電流値の定常状態が観測された場合、前記リセット制御部に前記CPUをリセットさせる電流監視部と、を備える。

(もっと読む)

電子機器装置

【課題】電子機器装置において、電源供給が瞬間的に断たれたときに、マイコンが異常状態にならないようにする。

【解決手段】電子機器装置1は、マイコン6と、リセットIC7と、電圧低下回路8とを備える。マイコン6は、ハイレベルの信号が入力されている状態からローレベルの信号が入力される状態に変化すると、動作をリセットし、ローレベルの信号が入力されている状態からハイレベルの信号が入力される状態に変化すると、起動処理を実行し、その後、通常処理を実行する。リセットIC7は、所定電圧値未満の電圧が入力されているときには、マイコン6にローレベルの信号を入力し、所定電圧値以上の電圧が入力されているときには、マイコン6にハイレベルの信号を入力する。電圧低下回路8は、商用AC電源10から電子機器装置1への電源供給が瞬間的に断たれたときに、リセットIC7に入力される電圧を一時的に所定電圧値未満に低下させる。

(もっと読む)

コンピュータのリセット方法およびコンピュータ

【課題】筐体を開放しないでRTCメモリをリセットする。

【解決手段】カレンダー時刻およびBIOSの設定情報を記憶するRTCメモリ25には、バックアップ電池51から電力が供給される。コンピュータがパワー・オフ状態のときにパワー・コントローラ31には電力が供給される。パワー・オフ状態においてキーボード63のFnキーおよびパワー・ボタン61を同時に押下すると、パワー・コントローラ31はリセット・スイッチ91を所定時間だけオフにしその後オンにする。その後、パワー・コントローラ31は自らに供給されている電力を一旦停止してから復帰させる。

(もっと読む)

P−RUN信号出力装置、組込制御装置

【課題】組込ソフトウェアが異常動作したときは確実にリセット信号を出力し、組込ソフトウェアが正常動作している間はリセット信号を不要に発生させないようにすることのできる技術を提供することを目的とする。

【解決手段】本発明に係るP−RUN信号出力装置は、優先度の異なる複数の組込プログラムの実行状態を監視し、システムクロックが示す時刻と各組込プログラムの前回実行時刻との差分が所定閾値を超えている場合は、P−RUN信号を出力しない。また、P−RUN信号を出力するか否かを判断してP−RUN信号を出力する処理を、組込プログラムのなかで最も優先度の高いもの以上の優先度で実行する。

(もっと読む)

光通信制御装置

【課題】親局と子局との間で光信号を通信する光通信制御装置で、CPUが動作不能な場合においても、装置のリセットを確実に行う。

【解決手段】親局1又は子局2では、PLD11、21とCPU13、23とFPGA12、22を有し、PLDはリセットを行うことを検出した場合にタイマを起動しリセットを行う旨の信号をCPUへ送信し、CPUは当該信号を受信した場合にはリセット前処理を実行しリセットの指示をPLDへ送信し、PLDは、当該指示を受信した場合にはCPUをリセットする信号をCPUへ送信し、タイマのタイムアウトが発生した場合にはCPUをリセットする信号をCPUへ送信し、FPGAはリセットに関する信号を相手の局との間で通信する。

(もっと読む)

電圧検出システム及びその制御方法

【課題】電源電圧の降下が急峻な場合、システムが誤作動を起こす可能性があった。

【解決手段】割込みモードと、リセットモードとを有する電圧検出システムの制御方法であって、第1、第2の検出レベルを設定し、電源電圧が前記第1の検出レベルより高い場合、ラッチ回路を第1の状態として、前記割込みモードに設定し、前記電源電圧が前記第1の検出レベル以下となった場合、割込み信号を生成し、前記ラッチ回路を前記第1の状態から第2の状態とすることで、前記リセットモードに設定し、前記リセットモード時に、前記電源電圧が前記第2の検出レベル以下となった場合、システムリセットする電圧検出システムの制御方法

(もっと読む)

データプロセッサ及びデータ処理システム

【課題】POR/LVD検出回路によるリセット信号の外部出力と外部リセット信号の入力を同一端子で兼用でき、外部出力するリセット信号が外部からのリセット信号の入力系に回り込むことを抑制する。

【解決手段】リセット信号の外部出力と外部からのリセット信号の入力に外部リセット端子(RESION)を兼用させ、電源電圧の安定状態では外部リセット端子からのリセット入力を許可し、検出回路(3)により電源電圧の投入又は電源電圧のレベル低下のリセット要因を検知したときはその検出信号を利用して、入出力バッファ(4)にリセット信号を外部リセット端子に出力させると共に入出力バッファからその入力経路への当該リセット信号の回り込みをマスクする制御を行う、リセットコントローラ(10)を採用する。外部へのリセット信号の出力より早く前記マスクを行い、マスク期間は、リセット指示から解除までの期間よりも長い期間とする。

(もっと読む)

集積回路、及びこれを用いた情報処理システム

【課題】CPUによるブートコードの実行速度の高速化とシステムの柔軟性の確保とを両立させつつ、マスタ回路と集積回路とを組み合わせた情報処理システムと、マスタ回路を備えない小規模な情報処理システムとに共用することが容易な集積回路、及びこの集積回路を用いた情報処理システムを提供する。

【解決手段】CPUと、RAMと、外部に不揮発性メモリを接続可能なSPIマスタ23と、RAMへのアクセスを受け付けるSPIスレーブ24と、第1ブートモードが設定された場合、開始アドレスを含んで不揮発性メモリをマッピングし、第2ブートモードが設定された場合、開始アドレスを含んでRAMのアドレスをマッピングするアドレスマッピング部25と、第1ブートモードではリセット信号に応じてCPUのリセットを解除し、第2ブートモードでは第2インターフェース部を介したアクセスに応じてCPUのリセットを解除するリセット制御部26とを備えた。

(もっと読む)

電子回路、その制御方法及び画像形成装置

【課題】内部メモリを有する電子回路において、待機状態での動作要求時の処理効率および省電力化の向上を図れる電子回路を提供する。

【解決手段】電子回路31は、通常モードにおいて外部メモリ34とアクセス可能な制御部41と、外部メモリより消費電力の少ない内部メモリ44と、ネットワークI/F67と、省電力モードにおいて、ネットワークI/F67から内部メモリ44へのアクセスを可能とする第2アクセス経路G2,F2と、経路切替部65とを含む。経路切替部65は、通常モードから省電力モードへの切替時に、制御部41の制御に応じて、外部メモリ34への第1アクセス経路G1を第2アクセス経路G2,F2に切替えることによって、通常モードにおいて外部メモリ用のアドレスがマッピングされていたアドレス空間を、内部メモリ用のアドレス空間に切替る。

(もっと読む)

画像処理装置、起動処理方法、起動処理プログラム及び記録媒体

【課題】本発明は、自動起動を適切に行う安価で小型の半導体集積回路を搭載する画像処理装置、起動処理方法、起動処理プログラム及び記録媒体に関する。

【解決手段】画像処理装置1は、起動時、バス制御回路14が内蔵CPU11を搭載し所定の動作処理を行う半導体集積回路10を起動させるのに必要な起動情報を取得するまで、リセット制御回路12が、内蔵CPU11の起動動作を待たせている。したがって、外部CPU2と内蔵CPU11を同時に起動させる必要がある場合にも、コンフィグレーション端子を設けることなく、半導体集積回路10の起動を安価にかつ適切に行うことができる。

(もっと読む)

画像形成装置及びその制御方法

【課題】コスト増加を招くことなく分散制御システムを適用するとともに、省電力モードからの復帰処理の高速化と安全性を向上させた画像形成装置を提供する。

【解決手段】本画像形成装置によれば、各CPUは、省電力モード遷移時に初期化処理に必要な情報の一部を自身の不揮発メモリに保持し、それ以外の情報については上位層のCPUに保存を依頼する。さらに、再起動時おいて、各CPUは、自身の不揮発メモリに記憶した情報を使用して再起動し、他のCPUとの通信接続が完了すると、下位層のCPUから依頼された保持データを当該CPUに提供する。

(もっと読む)

コンピュータのリセット装置

【課題】機器全体として確実にリセットを行うことができるコンピュータのリセット装置を提供する。

【解決手段】スイッチング回路を用い、外部から入力される大元の電源をオン/オフすることにより、リセット信号を電源のオン/オフと連動させる。これにより、コンピュータの各機器を確実にリセットする。即ち、各ICに出力されるDC−DCコンバータ等の電源変換部に入力される電源VDDを、直接オフし、他の全ての機器をリセットした後再起動させることによって、確実なリセット動作を行う。

(もっと読む)

システムの立ち上げ時間を早めるための方法、装置およびコンピュータ・プログラム

【課題】システムの立ち上げ時間を早めるための方法を提供する。

【解決手段】システム上にストアされたオペレーティング・システムの起動動作と並行しかつその後に、追加量のメモリを割り当てのためにスクラビングして利用することができるようにするステップとを含む。システムは、各々が最少ノード資源構成に関連付けられた1個もしくは複数個のノードを含むことができ、前記最少ノード資源構成は、前記ノードを活性化するために、活性化される必要のあるノードに含まれる最少数のプロセッサに対応する。システムは、各パーティションが少なくとも1個のノードを包含する1個もしくは複数個のパーティションを更に含むことができる。各パーティションには他のパーティションに対する優先度が割り当てられることができ、そのパーティションはその割り当てられた優先度に基づき活性化される。

(もっと読む)

情報処理装置及び情報処理装置の起動方法

【課題】起動時間を短縮できる情報処理装置及び情報処理装置の起動方法を提供する。

【解決手段】情報処理装置は、PLLを備え、低速の第1のクロック信号と第1のリセット信号とが入力し、前記第1のリセット信号の入力後、前記PLLの安定化期間経過後に、前記第1のクロック信号より高速の第2のクロック信号を出力するクロック生成部と、前記第2のクロック信号に基づいて、入力するデータを処理するデータ処理部と、内部メモリを備え、前記クロック生成部の前記PLLの安定化期間に、前記データ処理部に処理させる前記データの少なくとも一部を、外部メモリから前記内部メモリにロードするデータロード部と、を備える。

(もっと読む)

データ処理装置

【課題】リブート時の初期値設定を速やかに行うデータ処理装置を提供すること。

【解決手段】データ処理装置10は、プルアップ抵抗Ruあるいはプルダウン抵抗Rdに接続される複数の信号線であって、初期設定データboardid_in[2:0]を生成する複数の信号線rom_adr[2:0]と、当該装置10の電源投入時において、前記初期設定データboardid_in[2:0]によって当該装置10の初期設定を行う設定部42と、初期設定データboardid_in[2:0]を保持する保持部41とを含む。設定部42は、電源投入時に初期設定データboardid_in[2:0]を保持部41に保持させ、当該装置10のリブート時において、保持部41に保持された初期設定データboardid_in[2:0]を利用して当該装置10を再初期設定する。

(もっと読む)

1 - 20 / 97

[ Back to top ]